带有外同步输入的图像处理和实时显示系统

王慧中,吴永欣,茹运蕊,褚成琴,栗武华

(中国电子科技集团公司第27研究所,河南 郑州 450047)

1 引言

近年来,随着多媒体技术的迅速发展和普及,数字图像处理技术的应用越来越广泛,在航空航天遥感、生物医学、军事和公共安全、工业生产和管理、多媒体应用等各个领域都得到了广泛的应用[1]。

笔者介绍的图像处理和实时显示系统以TI公司C6000系列的高速DSP和Xilinx公司的Spartan 2E系列的现场可编程门阵列(FPGA)为核心构建而成[2]。其中,DSP主要用来完成解压缩、数字图像叠加、视频合成等复杂的数字图像处理工作,而FPGA主要用来完成视频时序控制和外围设备的硬件逻辑控制等工作。文中重点内容为该系统的软硬件设计以及关键环节的解决方案。

2 系统原理及工作过程

由于数字图像的信息量大,而且该系统的设计对实时性要求较高,因此系统设计采用高速DSP作为数字图像处理的核心单元。同时,为了实现外部时钟信号对视频输出的控制,该系统的设计选择采用内嵌大容量RAM的FPGA来实现视频时序的产生及控制。整个系统设计采用DSP+FPGA结构来实现。系统的原理框图如图1所示。

图1 系统原理框图

该系统的工作过程如下:DSP通过EMIF接口从Flash中读取欲处理的图像数据,以EDMA方式写入SDRAM,DSP对SDRAM中的原始图像数据进行解压、滤波、复合等数字图像处理,并将处理后的数据转换为符合CCIR-6564∶2∶2 格式的 8 bit数字视频流,处理后的数据仍放到SDRAM中。DSP在响应FPGA视频时序产生模块生成的行中断信号后,由EDMA控制器以PDT传输的方式写入FPGA内建的显示行FIFO,在显示同步时序的控制下,从显示行FIFO输出到视频编码器中,生成复合视频,送显示。

3 系统软硬件设计

3.1 硬件设计

本系统主处理器采用了TMS320DM642,它是TI公司推出的专用于数字媒体应用的高性能64位定点DSP,工作频率最高为720 MHz,处理性能可达5760 MI/s(兆指令每秒)[3]。TMS320DM642片内集成了大容量的存储器,片内采用二级存储器结构。此外,还提供丰富的外围设备接口,包括外部存储器接口(EMIF)、GPIO接口、I2C总线控制器、中断控制器等[4]。

由于本系统的视频输出受外部时钟的控制,因此,未采用TMS320DM642的VP口,而是由可编程逻辑器件FPGA生成视频显示的同步时序信号。本系统的硬件设计框图如图2所示。

图2 系统硬件设计框图

1)数字图像存储单元

TMS320DM642的外部存储器接口(EMIF)支持各种外部器件的无缝接口[5],包括流水线式同步猝发SRAM(SBSRAM),同步 DRAM(SDRAM),包括 SRAM,ROM 和FIFO等在内的异步器件,以及外部共享存储器等[6]。

本系统设计中,在CE1子空间外扩了8M×8 bit的非易失性存储器(Flash),用来存储DSP的配置程序和原始数据,由于TMS320DM642的外部地址总线只有20根,所以CE1子空间的最大寻址范围为1M×8 bit,为了寻址到Flash的所有地址空间,系统设计中采用了分页技术来实现对Flash的访问。在CE2子空间外扩了SDRAM组成大容量高速帧存储器和行缓冲,系统对SDRAM中2块不同帧存储区域轮流进行读写操作,大大提高了通信速度和数据吞吐量[7]。系统对帧存1和帧存2的轮流读写是通过乒乓传输结构来实现的,乒乓传输结构可有效保证数据传输的连续性。

2)FPGA逻辑控制单元

本系统中视频时序控制信号的产生是由FPGA实现的,FPGA内部逻辑设计采用模块化设计[8],以原理图或VHDL语言生产各功能模块:主要包括水平像素计算模块、垂直行计数模块、同步信号发生模块、FIFO读控制和复位信号产生模块以及DSP中断信号产生模块。采用ISE软件进行编译仿真,各底层模块均采用计数器实现,能够精确产生各种信号。除此之外,可与外部时钟保持良好的一致性,在每一场的起始重新与外部系统时钟同步一次。

FPGA内部形成的的延迟锁相环用来调整视频同步信号时序和视频编码芯片的像素时钟之间的相位差。此外,由于视频编码模块和帧存储器之间的时钟频率不同,设计中采用FPGA中内嵌的BlockRam构造了异步FI⁃FO,用来做时钟域之间的隔离,协调数据传输速度。

3)视频编码单元

考虑到系统的工作环境和应用领域,视频编码模块的设计采用了ADI公司的专用视频编码器ADV7171,可在-40℃~+85℃温度下正常工作。ADV7171兼容全球各种视频标准,对芯片的初始化可通过I2C总线完成。I2C总线只有串行数据线(SDATA)和串行时钟线(SCLOCK),总线上的每个设备都有一个由软件设定的唯一地址。I2C总线的数据读写格式如图3所示。

图3 I2C总线数据读写格式

DSP通过内部集成的I2C总线接口实现对视频编码器ADV7171内部寄存器的读写访问操作,完成对视频制式选择、同步信号模式选择等工作。专用视频编码器的使用,不仅提高了系统的可靠性,增强了系统功能,还缩短了开发周期,降低了成本。这些优越性是使用普通D/A所不具有的。

3.2 软件设计

本系统的软件设计采用“C语言+线性汇编”的模式在CCS2.2编译环境下编写,系统的软件设计包括顶层应用程序和设备驱动程序两部分。顶层应用程序主要完成对系统流程的控制、底层设备的管理和初始化,设备驱动程序主要用于实现对底层设备(如Flash,SDRAM和视频编码器等)的读写操作和控制。系统的软件设计框架如图4所示。

1)设备驱动程序的开发

图4 系统软件设计框图

该系统的设备驱动程序主要包括定时器、通用目的输入输出(GPIO)、中断控制器等片上外设的配置和管理,外部扩展存储器(SDRAM,Flash和FIFO等)的读写操作和管理,以及视频编码芯片的配置和控制。片内外设的驱动程序主要通过芯片支持库(CSL)提供的API函数来完成对片内外设寄存器的设置,从而实现对片内外设的配置和管理,外部存储器(SDRAM,Flash以及FIFO)的读写操作和管理是外部存储器接口(EMIF)寄存器、增强的直接存储器访问(EDMA)控制寄存器以及中断控制寄存器的配置来完成的,而对视频编码芯片的管理和控制则是通过DSP片内集成的I2C模块对视频编码芯片相关寄存器的配置来实现的。

2)应用程序的开发

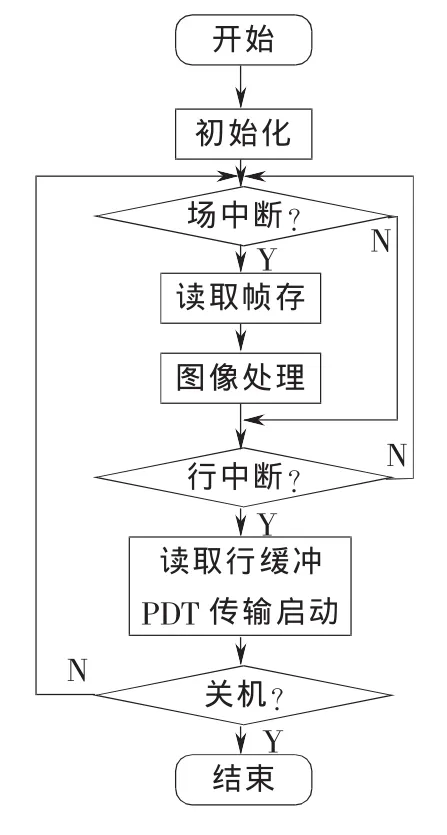

该系统的顶层应用管理程序的设计采用了模块化结构,根据工程应用的具体要求,主要划分为初始化模块、图像处理模块、中断管理模块和外部存储器模块等几个部分,模块化的设计结构使得程序更加易于调试和修改,应用程序的软件设计流程如图5所示。

图5 应用程序设计流程图

4 小结

本文给出了基于DSP和FPGA结构的带有外同步输入的图像处理和实时显示系统的设计方案,已成功地应用于工程实践中。由于本设计中采用FPGA来产生和控制视频时序信号,可在不改变硬件电路的情况下,只通过重写FPGA来满足不同视频制式的时序要求,大大提高了电路的适应性和灵活性。此外,由于在本设计中,每场起始时均与外部50 Hz时钟重新同步一次,因此,本设计可适用于对同步要求较高的场合。

[1]何斌,马天予.Visual C++数字图像处理[M].2版.北京:人民邮电出版社,2002.

[2]盛磊,徐科军.基于DSP和FPGA的实时视频处理平台的设计与实现[J].电气测量及仪器,2006,36(3):304-309.

[3]TI.TMS320DM642 Video/Imaging Fixed-Point Digital Signal Processor[EB/OL].[2009-12-12].http∶//focus.ti.com/lit/ds/sprs200m/sprs200m.pdf.

[4]江思敏,刘畅.TMS320C6000 DSP应用开发教程[M].北京:机械工业出版设,2005.

[5]TI.TMS320C6000 DSP external memory interface(EMIF)reference guide[EB/OL].[2009-12-12].http∶//wisconsin.cern.ch/ROD/ti_documents/EMIF%20Reference%20Guide-%20spru266b.pdf.

[6]美国德州仪器公司,TMS320C6000系列DSP的CPU与外设[M].北京:清华大学出版社,2007.

[7]王建华,刘缠牢,陈大川,等.基于DSP+FDGA技术的实时视频采集系统的设计[J].国外电子测量技术,2007,26(9):42-48.

[8]史彩娟,李文元,张培芳.基于CPLD的电视信号发生器的设计与实现[J].电子测量技术,2006,29(3):76-78.