基于PicoBlaze的GPS信号数据解调设计与实现*

胡永春 欧 钢 张 建 陈 亮

(国防科技大学电子科学与工程学院卫星导航定位研发中心 长沙 410073)

1 引言

全球定位系统(GPS)是基于卫星星座的导航定位系统。对用户而言,GPS应用的关键设备是能够捕获、跟踪、变换和测量GPS信号的接收机[1]。如何优化接收机的各个组成部分,设计出低成本、高性能的接收机一直是人们关注的重点。

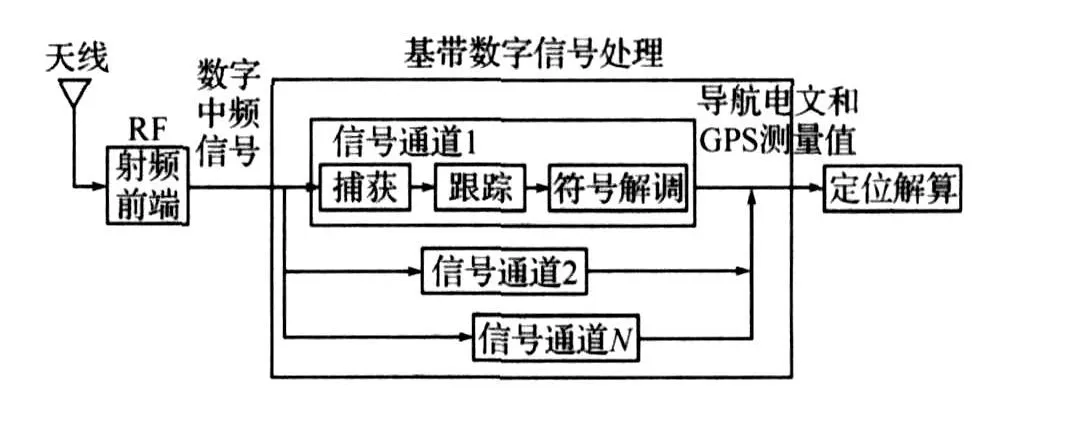

如图1所示为接收机示意图,GPS天线感应包括多颗卫星信号在内的各种电磁场信号,射频前端将这些信号滤波放大后输出数字中频信号进入基带处理模块,基带处理模块通常采用信号通道的形式,即每个通道各自捕获、跟踪和测量一颗不同卫星的信号,输出导航电文和GPS测量值。全部 N个通道输出的有效电文和测量值一起输入定位终端进行导航定位解算[2]。

图1 接收机内部信号通道

数据解调是指在完成GPS信号的捕获和跟踪后,根据跟踪环路输出的相关值解调出导航电文的过程,包括位同步、帧同步、奇偶校验和电文译码四个步骤。本文主要讨论GPS信号数据解调电路的优化设计。

2 数据解调算法概述

2.1 位同步

如图1所示,信号通道中的载波跟踪环路输出码速率为1000bps的二进制数,而GPS卫星导航电文的码速率为50bps,因此要恢复导航电文,就必须找到每个导航电文数据位在载波跟踪环路输出的二进制数据串中的起始位置,并将从该位置开始的20个连续的二进制数合并成一个导航电文数据位,这个过程称为位同步。

位同步最常用的方法是直方图法,该方法统计20个假定的位边界下的符号翻转的次数。当其中某个假定的位边界的统计次数明显大于其它位置时,则认为该位置即为正确的位边界。由于该方法只使用了准时相关通道同相支路的相关累加值的符号位,因此在低载噪比时,其检测性能会急剧下降。文献[3]介绍的分段累加的思想采用分段相关-视频积累的方法,计算各种可能的位边界下,I支路的相关值与二级调制码的分段相关-视频积累值,并选择使该值达到最大时的位边界作为正确的位边界。该方法相比直方图法能提高检测性能,减少位同步错误,故本文采用该方法进行位同步操作。

2.2 帧同步

GPS导航电文的格式为:每帧导航电文长1500比特,依次由5个子帧组成,每个子帧长300比特,依次由10个字组成,每个字长30比特,且每个子帧的第一字的前8比特固定为同步码10001011。载波跟踪环输出的二进制数据串在经过位同步之后解调出码速率为50bps的数据比特流,帧同步就是根据同步码确定子帧帧头位置并将这些数据比特按GPS导航电文格式每30个比特组成一个字的过程。

GPS导航电文的同步引导码—巴克码的特点是只有当完全匹配时,才有较大的相关值,否则其值很小。巴克码的这种特性十分适合用于帧同步。本地生成一个预定的巴克码与接收到的信息进行相关,若相关值达超过门限,则可判定找到了帧头。

2.3 奇偶校验和电文译码

在帧同步完成后,就可以按照GPS界面控制文件[4]中规定的奇偶校验方式和导航电文的格式对数据进行校验和译码,输出导航电文信息了。

3 数据解调方案设计

如图2所示为我们设计的GPS接收机的数字部分的硬件结构,利用现场可编程门阵列器件(FPGA)进行基带处理,具有 12个信号通道,能同时对12路GPS信号进行捕获、跟踪,完成信号的解扩解调。利用ARM处理器进行终端处理,实现最后的定位解算,并辅助基带处理部分完成信号的捕获、跟踪、解扩解调等操作。

3.1 实现方式

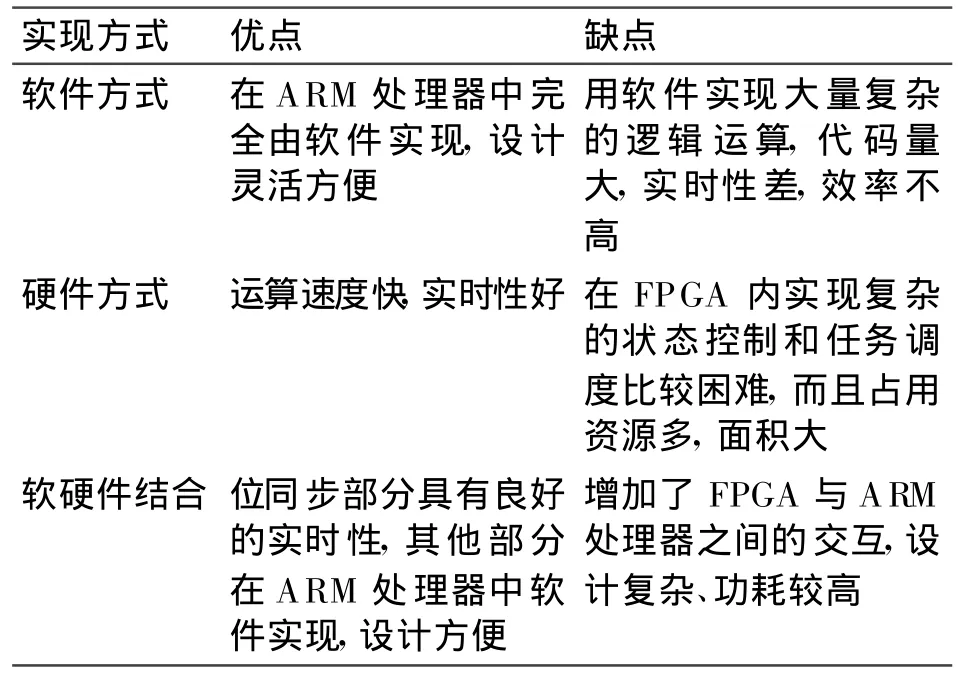

基于图2所示的接收机数字部分硬件结构,GPS信号数据解调的实现方式有三种,第一种是硬件方式:在基带处理部分用FPGA实现;第二种是软件方式:在终端处理部分用ARM处理器实现;第三种是软硬件结合:在基带处理部分用硬件实现位同步,而将帧同步、奇偶校验和电文译码过程在终端处理部分用软件实现。三种方案的优缺点如表1所示。

表1 数据解调实现方式比较

从表1对数据解调的三种实现方式的优缺点的分析比较可知,由于同时对12路GPS信号进行数据解调涉及复杂的状态控制和大量的逻辑计算,ARM处理器能很方便地实现复杂的状态控制,用FPGA以硬件方式来实现逻辑计算则具有实时性高,占用资源小的优点。上述三种方式各有优势,但也各具有明显的缺点,没有有效地结合处理器进行状态控制和硬件进行逻辑计算两者的优势。

表1中的第三种方式即软硬件结合的方式根据GPS信号的处理流程将数据解调分解为位同步、帧同步、奇偶校验和电文译码,其中位同步在FPGA中硬件实现,而帧同步、奇偶校验和电文译码则在ARM处理器中软件实现,这种方式在一定程度上结合了软件实现和硬件实现的优点,但由于划分过于简单,而且位同步和帧同步、奇偶校验、电文译码分别在FPGA和ARM处理器中实现,增加了FPGA与ARM 处理器的交互,设计复杂,功耗较高,并不是最优方案,将位同步、帧同步、奇偶校验和电文译码都用FPGA实现,采用嵌入式处理器加专用加速硬件的结构,由嵌入式处理器进行状态控制,专用硬件进行逻辑计算,则可以充分利用两者的优势,设计出比上述三种方式都加优化的GPS信号数据解调电路。

3.2 嵌入式处理器选型

GPS信号数据解调方案中的嵌入式处理器的选择非常关键,处理器的速度、面积、性能将直接决定整个数据解调电路的软硬件划分,影响软硬件协同设计,在资源紧张的情况下,还将影响基带处理部分的捕获、跟踪功能的实现。

表2 Xilinx主要的嵌入式处理器及其特性

表2列出了Xilinx主要的嵌入式处理器,PowerPC硬核处理器由于集成在Virtex系列FPGA中,成本过高,不宜采用。MicroBlaze是32位高性能处理器,尽管性能优异,但是由于数据解调电路的状态控制部分并不是非常复杂,选用MicroBlaze处理器反而会增加系统的功耗、占用过多的资源,所以不适合数据解调电路。

PicoBlaze是英国的 Ken Chapman开发的8位可编程定序器,由A LU、程序计数器栈(使用于嵌套子程序)、16个8位寄存器、64字节暂存器、程序计数器和控制器以及中断支持电路构成。具有集成的图形开发环境和c编译器,多个成熟稳定的开发实例。作为嵌入式定序器,该器件非常适用于控制灵活性快速超过传统HDL表达的应用,其实用特性包括极低的资源占用率(1个18KB BRAM和96个Spartan-3逻辑片)和每条指令确定的两个时钟执行周期[5]。特别适合作为数据解调电路中的嵌入式处理器。

4 基于PicoBlaze的数据解调

4.1 硬件结构

由于PicoBlaze的代码容量有限,仅为1024行代码,为了充分发挥PicoBlaze处理器在状态控制方面的优势,于是将位同步和帧同步过程中的大量相关运算以及GPS校验译码设计成专用硬件,加速逻辑运算,同时PicoBlaze控制12个通道以分时复用的方式调度专用硬件,提高专用硬件的利用效率。

GPS信号数据解调的硬件整体结构如图3所示,包括PicoBlaze处理器、总线译码模块、外部总线接口、数据存储器、数据相关器和GPS译码模块。

图3 硬件结构

PicoBlaze处理器模块通过总线译码模块可以访问本模块内的各个子模块以及外部的12个跟踪通道。通过在处理器上运行的软件调度其它模块工作,完成位同步、帧同步、奇偶校验和电文译码等操作。数据存储器为每个通道分配了相应的存储空间,供PicoBlaze运行软件时存储与各个通道有关的数据,以及存储外部微处理器可以通过外部总线读取的导航电文。数据相关器用于在位同步和帧同步过程中加速相关运算的实现。GPS译码模块对1个字(30bit)的GPS导航电文进行奇偶校验和电文译码,输出校验结果和译码后的电文。

4.2 软件流程

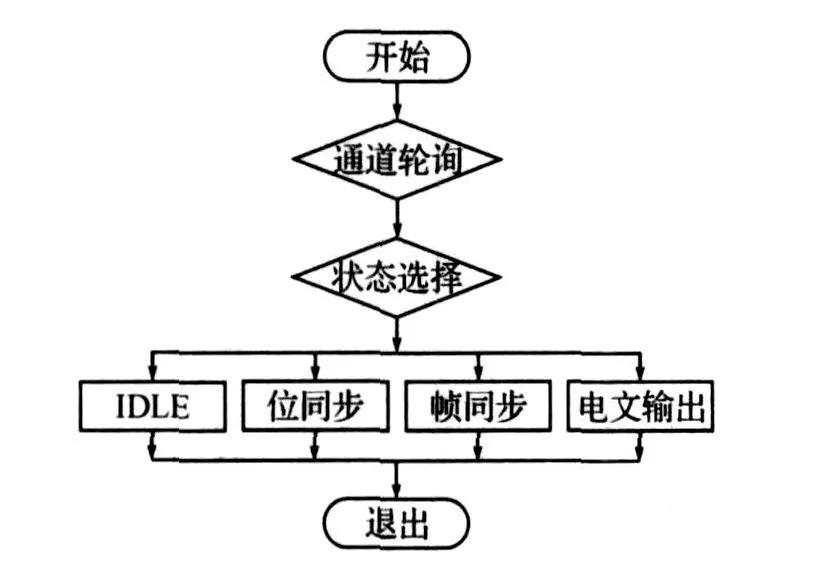

PicoBlaze软件总的处理流程如图4所示。根据数据解调的信号处理流程,将数据解调大致分为IDLE、位同步、帧同步和电文输出四个状态,其中在IDLE状态时PicoBlaze闲置,电文输出阶段完成奇偶校验和电文译码,工作时,首先进行通道轮询,然后根据该通道的状态寄存器进入相应的状态分支,在每个状态分支中调用相应的专用硬件完成该状态的处理后退出,进行下一个通道的处理。

通过划分状态和通道轮询,软件部分以分时复用的方式与专用硬件紧密配合完成与12个跟踪通道的数据交互以及每个通道的位同步、帧同步和电文译码等任务,程序模块化设计方便,结构优化,代码的可读性和可维护性良好。

图4 软件流程

5 测试

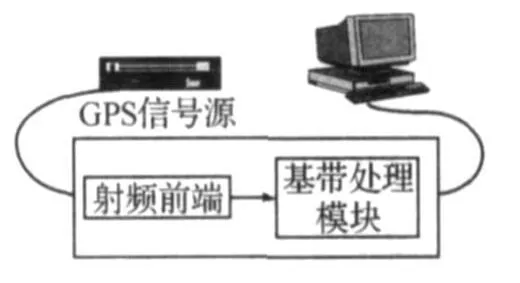

图5 测试

在实际测试中,搭建如图5所示的验证平台,利用GPS信号源产生信号进行测试,射频前端将射频信号转换为中频信号,数据解调模块作为GPS基带处理模块的一个子模块,负责解调经过捕获和跟踪后的GPS信号,PC端接收基带处理模块输出的的导航电文,并将其与GPS信号源播发的电文进行比对,测试结果表明设计方案有效,12个通道均正确输出导航电文。

6 结语

在GPS信号基带处理中,同时对12路GPS信号进行数据解调状态控制复杂、逻辑计算量大。采用PicoBlaze处理器加专用硬件的结构,由嵌入式处理器完成状态控制,专用硬件实现逻辑计算、加速处理速度。通过时分复用的方式使12路信号共用一个解调电路,软件开发灵活、硬件逻辑简单、占用资源少、电路利用效率高。通过实际测试表明,硬件正常工作,12个通道均正确解调导航电文。

[1]廖晰,张晓林,王宇恒.GPS信号捕获跟踪环路的研究及实现[J].电子测量技术,2009,32(2):36

[2]谢钢.GPS原理与接收机设计[M].北京:电子工业出版社,2009,7:238

[3]M.Kokkonen,S.Pietila.A New Bit Synchronization Method for a GPS Receiver[C]∥Proc.of the IEEE Position Location and Navigation Sym posium.Pa lm Springs.CA,2002:85~90

[4]INTERFACE SPECIFICATION IS-GPS-200.U.S.A.2004,12:134

[5]隐藏的珍宝:PicoBlaze IP[J].赛灵思中国通信,2009(32):24