基于FPGA的线阵CCD驱动电路设计

王习东 陈重江 陈志勇

(1.三峡大学理学院光电技术研究所,湖北 宜昌 443002;2.三峡大学 理学院电子信息系,湖北 宜昌 443002;3.当阳市第一高级中学物理组,湖北 当阳 444100)

1 概 述

电荷耦合器件CCD是近40年来发展的新型光电传感器[1-2],由于其独特的性能使CCD器件的研究和相关应用技术的研究取得了惊人的进展,特别是应用在图像传感和非接触测量领域.线阵CCD驱动信号一般为复杂的周期信号,由于不同型号的CCD其驱动时序不同,使得CCD的驱动电路复杂多样[3-5],一般驱动信号产生方法有通用逻辑电路驱动、专用IC驱动、FPGA芯片驱动、复杂的CPLD驱动、单片机驱动等.由普通数字电路芯片实现的驱动,电路体积大,设计复杂且过于偏重于硬件的实现,调试工作量大、容易出错和灵活性较差,特别是工作在较高频率时系统容易受到干扰,工作不稳定.用可编程逻辑器件实现驱动电路的好处是电路规模减小,使用芯片数目较少,可以把精力放在程序的编写和仿真上,略去了数字电路的搭建与芯片选择的繁琐步骤,从而可以保证系统较为稳定.

基于FPGA的CCD驱动主要是通过程序指令在FPGA芯片的I/O口上输出逻辑状态,从而产生相应的驱动脉冲,这种方法硬件电路非常简单,可以通过修改程序方便地改变驱动脉冲及调整积分时间,根据环境要求改变系统工作的性能.文章设计的是一个频率在外部可调的CCD驱动电路,可根据具体要求选择所需要的频率,满足不同环境下的探测要求.

2 TCD1206SUP驱动脉冲时序

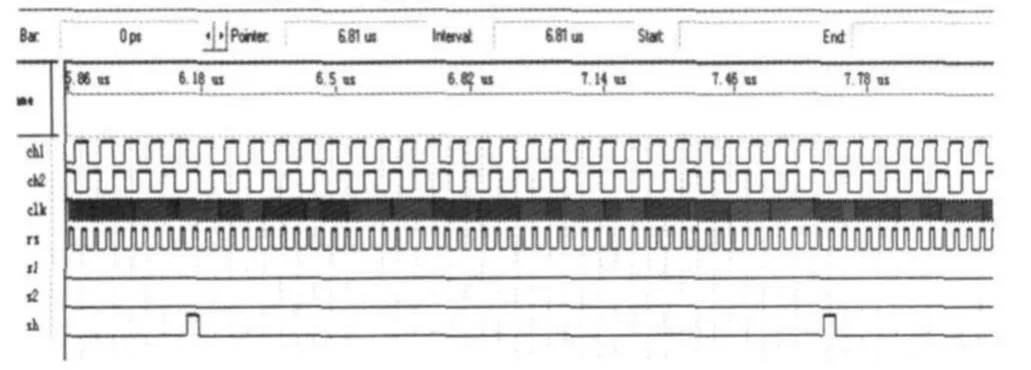

TCD1206SUP是由2236个PN结光电二极管构成光敏单元阵列,其中前64个和后12个是用作暗电流检测而被遮蔽的,中间的2160个光电二极管是曝光像敏单元,MOS电容存储栅的两侧是转移栅电极SH,转移栅电极的两侧为CCD模拟移位寄存器,其信号输出部分由输出放大器单元的OS端输出,并在补偿输出单元的DOS端输出补偿信号.TCD1206SUP的驱动脉冲时序如图1所示.

图1 TCD1206SUP驱动脉冲波形图

3 TCD1206SUP驱动电路的实现

3.1 开发工具和流程

国内外使用FPGA完成CCD的驱动已有不少工作,但大多都是基于FPGA单独使用来完成单一信号输出,没有附加频率可选功能.增加频率可选功能,减少了芯片使用量,使频率选择和信号产生两项功能在一块FPGA芯片中就能实现,节约了成本,性能更加可靠.Quartus II 7.2是Altera公司近几年推出的新一代、功能强大的可编程逻辑器件开发环境[2,4],输入、处理和校验功能集成在统一的开发环境下,含有丰富的设计库,支持多种输入方式,如文本输入,波形输入,图形输入等,文中采用VHDL文本语言输入方式,Quartus II 7.2采用的自顶向下的设计方法.

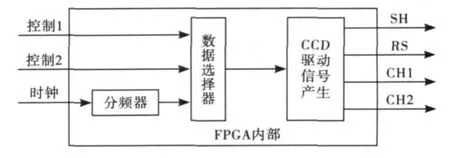

3.2 驱动脉冲产生工作原理

为了满足TCD1206SUP驱动脉冲时序要求,设计的FPGA脉冲驱动器包括分频器、数据选择器以及CCD驱动信号产生器等功能模块,在FPGA内部工作原理如图2所示.

图2 FPGA内部工作原理图

外部时钟信号由晶体振荡电路产生的6MHz方波脉冲提供,在FPGA芯片内部再进行二分频、四分频、八分频,以满足TCD1206SUP复位脉冲RS、同步脉冲HC、转移脉冲SH、采样脉冲SP等驱动频率的要求.通过数据选择器来对频率进行选择,以不同的频率脉冲驱动 TCD1206SUP,实现在不同的积分时间下获取较好的效果.在Quartus II 7.2开发环境下,选用 EP1K30TC144-3芯片,其工作电压为2.5V,芯片的功耗较低,集成度为11.9万门,基于查找表结构.采用先进的1.8V/0.18μ m、6层金属连线的SRAM工艺制成.共有144个管脚.依据驱动信号的要求,设计信号产生系统的顶层工作原理,如图3所示.

图3 Quartus II 7.2平台下驱动信号产生工作原理图

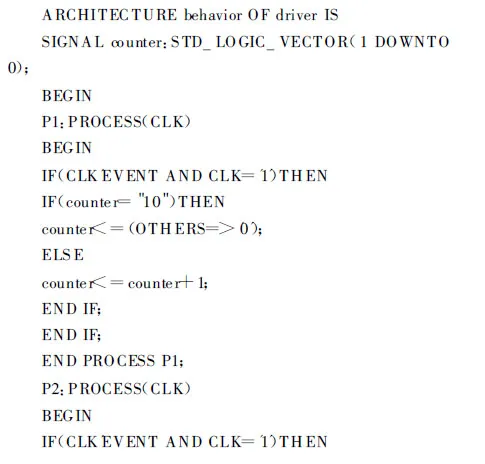

CCD驱动信号产生由VHDL程序实现,首先对输入脉冲进行三分频,对其进行脉宽调整,实现复位脉冲RS,然后对其进行二分频,得到CH1及CH2信号,再获得电荷转移脉冲信号,部分源代码如下.

编译后,系统仿真得到的波形图如图4所示.

图4 CCD驱动时序图

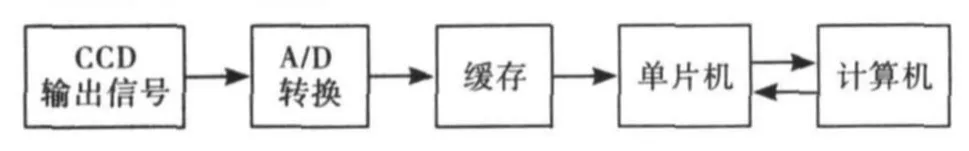

4 TCD1206SUP输出信号处理

将基于FPGA的CCD驱动信号输入到TCD1206SUP芯片,光电信号由CCD的OS端输出.对输出的信号采用浮动阈值二值化法处理,通过单片机采集和处理信号,并且保持与计算机进行通信,便于对信号存储和进一步的分析处理,其中信号处理部分功能如图5所示.

图5 CCD输出处理功能图

5 结 语

在该系统中,只采用一块芯片即可实现频率可调的CCD驱动信号的产生,所需芯片数量远少于数字电路搭建的系统,通过编程测试,减少了搭建硬件所带来不必要的损失,在实现效果上驱动信号质量也更优于一般的数字电路,提高了可靠性,易于维护和升级.

[1]王庆友.图像传感器应用技术[M].北京:电子工业出版社,2002.

[2]江国强.EDA技术与应用[M].北京:电子工业出版社,2004.

[3]喻 川,邹 建.基于CPLD的可调积分时间线阵CCD驱动的设计[J].四川兵工学报,2008,29(3):94-96.

[4]张殿富,赵 源.基于FPGA的线阵CCD驱动时序及模拟信号处理的设计[J].电子设计工程,2009,17(1):41-43.

[5]袁金风,陈文艺,李 凯.基于FPGA的线阵 CCD驱动时序电路的设计[J].现代电子技术,2009,290(3):160-162.