FPGA中浮点运算功能的实现技术

茅 飞 刘树青 朱兴华 朱昊

1.南京康尼电子科技有限公司,江苏 南京 210013

2.南京工程学院先进数控技术江苏省高校重点建设实验室,江苏 南京 211167

3.常州大学机械工程学院,江苏 常州 213016

FPGA中浮点运算功能的实现技术

茅 飞1刘树青2朱兴华3朱昊2

1.南京康尼电子科技有限公司,江苏 南京 210013

2.南京工程学院先进数控技术江苏省高校重点建设实验室,江苏 南京 211167

3.常州大学机械工程学院,江苏 常州 213016

浮点运算在众多领域广泛应用,通过采用纯硬件电路方法实现并形成模块化,可以增强可移植性、提高浮点运算速度和精度、缩短研发周期和降低开发成本。详细介绍了FPGA中浮点运算功能的实现算法和实现技术,实现了32位浮点数的加减乘除功能运算单元设计,通过QuartusII自带的仿真软件获得仿真波形,验证了正确性。

浮点运算;现场可编程门阵列;模块化

随着半导体技术的快速发展和生产工艺水平的不断提高,FPGA芯片在性能和密度方面得到了提高,已具有性能高、密度高、电压低、功耗低、可靠性高等特点,可满足纯硬件实现浮点运算的需要。本文介绍了FPGA中浮点运算功能的实现算法和实现技术。

1.浮点数的描述

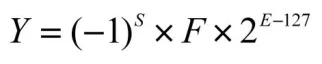

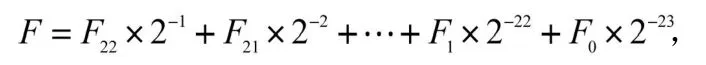

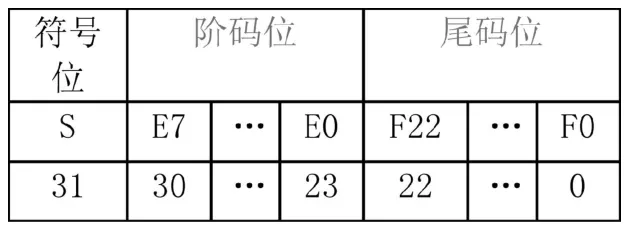

E为阶码位,共8位,E∈[1,254],当E=0或E=255时Y为非数(NAN,Not A Number)或非规格化数。32位浮点数(单精度)组成结构如表1。

表1 32位浮点数组成结构

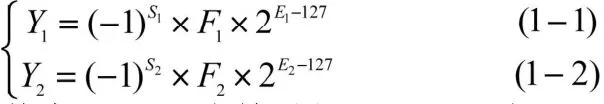

为表述方便,设有浮点数Y1和Y2,分别为:

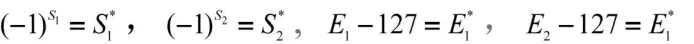

其中S1,S2为符号位;F1,F2为尾码位;E1,E2为阶码位。令

2.浮点数加减法设计

2.1 浮点数加减法算法

如(1-3)、(1-4)两个浮点数,其加减法运算可如下表示:

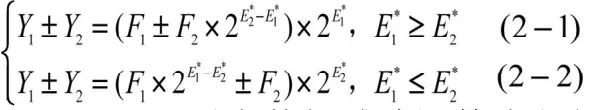

Y1和Y2两浮点数加减法运算流程如图1所示。其运算步骤如下:

⑷ 求和或求差:对阶完毕浮点数的尾码需要进行求和或求差;

图1 浮点数加减法流程

2.2 加减法模块实现

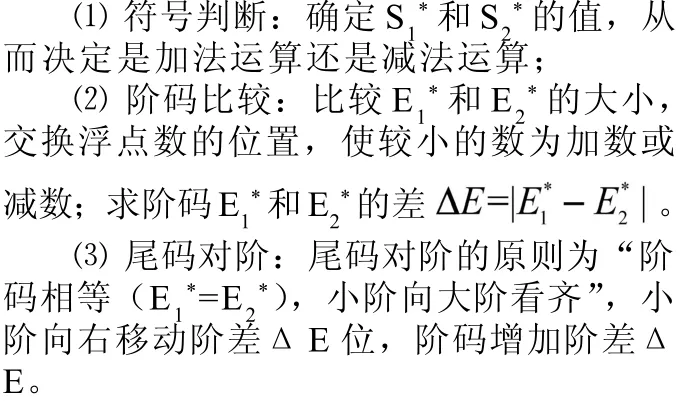

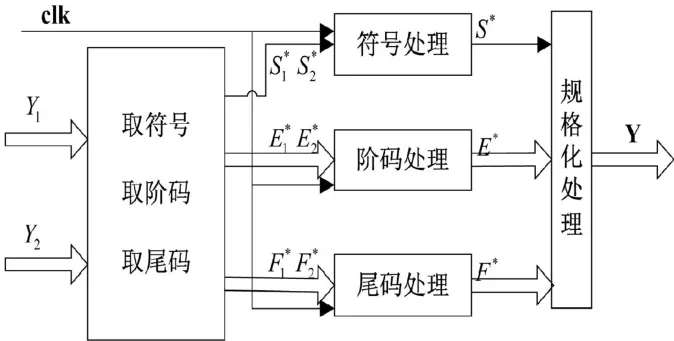

根据2.1算法,可利用Verilog HDL硬件描述语言实现浮点数加减法运算器。浮点数运算器逻辑框图如图2所示。

图2 浮点运算器逻辑框

浮点数进入输入单元后,提取出符号位、阶码位、尾码位送到相应的运算单元进行处理,再经过规格化处理单元,得到结果。浮点运算器端口定义见表2。

在加减法运算单元中,符号判断和前导1检测比较重要,前者决定运算方式和最终结果符号,后者为规格化服务。

表2 浮点运算器端口

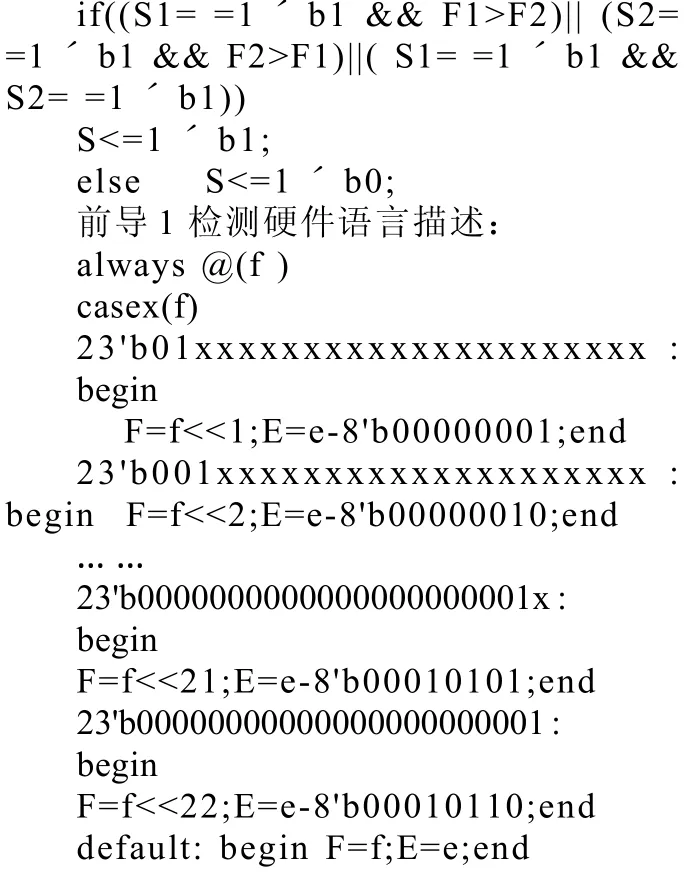

符号判断硬件语言描述:

其中y为两浮点数尾码相加或相减后的结果,e为两浮点数阶码比较后的阶码,前导1检测就是检测尾码运算结果的第一位是否为1,如不是,则左移,左移1位,阶码减1;casex语句中x表示0、1均可,如23'b001xxxxxxxxxxxxxxxxxxxx表示只判断前三位是否001,条件成立则f左移2 位赋值给F 输出,F 值为23'b1xxxxxxxxxxxxxxxxxxxx00,同时阶码减2(8'b00000010)。

3.浮点数乘除法设计

3.1 浮点数乘除法算法

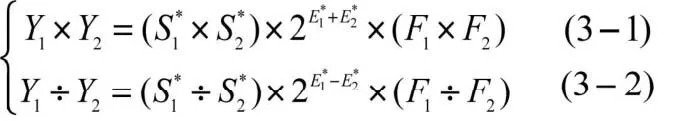

如(1-3)、(1-4)两个浮点数,其乘除法运算可如下表示:

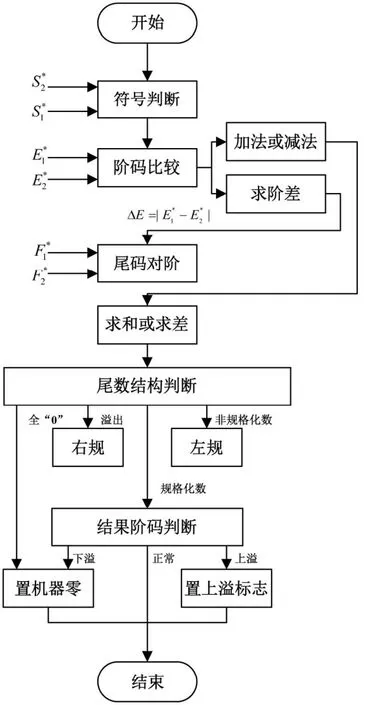

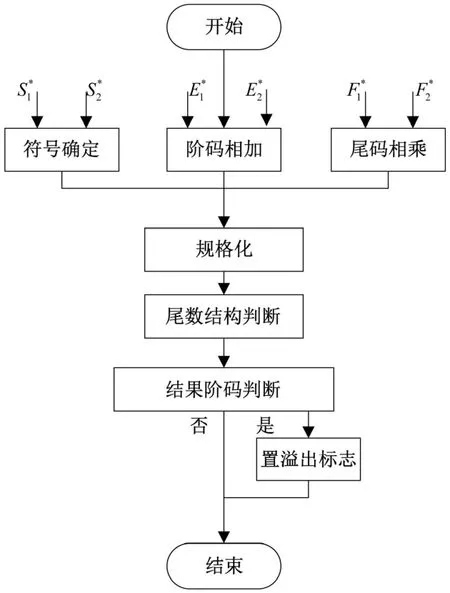

Y1和Y2两浮点数乘除法运算流程如图3所示。其运算步骤如下:

得出结果符号。

⑷ 规格化处理:对结果进行前导零检测、初次规格化、尾数舍入和最终规格化得到最后结果。

图3 浮点数乘除法流程

3.2 乘除法模块实现

根据3.1算法,利用Verilog HDL硬件描述语言、FPGA内嵌的硬件乘法器和除法器实现浮点数乘除法运算单元。浮点数乘除法运算逻辑框图如图2所示。

浮点数进入输入单元后,提取出符号位、阶码位、尾码位送到相应的运算单元进行处理,再经过规格化处理单元,得到结果。浮点运算器端口定义见表2。

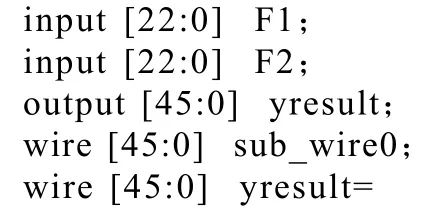

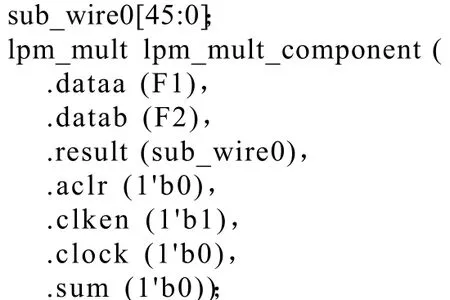

内嵌硬件乘法器和除法器可完成高速乘除法操作,精度较高。比使用逻辑单元完成乘除法运算更节省逻资源,延时更小。内嵌硬件乘法器例化描述如下:

其输入为23位,输出结果为45位,结果经舍入处理为23位后,规格化得到尾码23位。

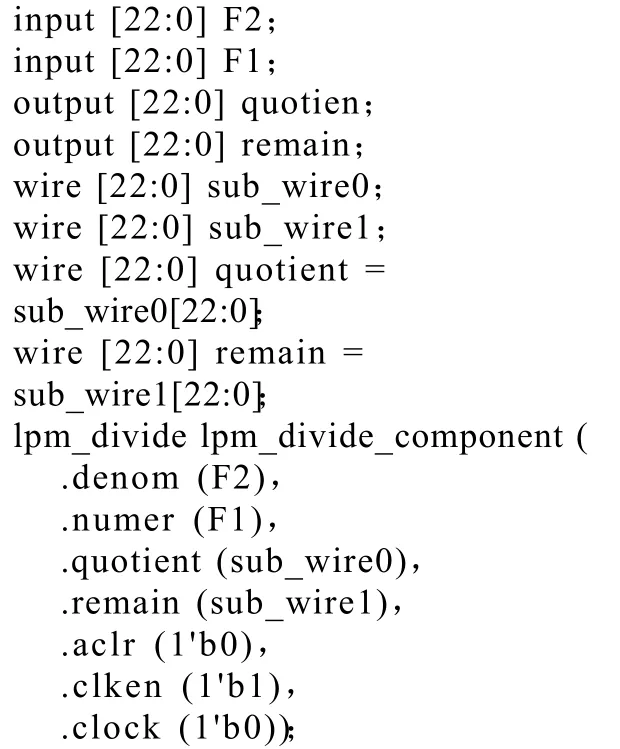

硬件除法器例化与乘法器有所不同,其结果分

为商和余数,内嵌硬件除法器例化描述如下:

其输入为23位,输出商为23位,余数为23位,余数经过移位与除数辗转相除,得到最后结果。

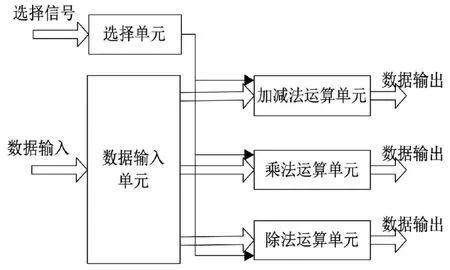

4.浮点数运算模块化

在浮点数加减、乘除运算单元的基础上,实现三个子单元的模块化设计,可以缩短研发周期和降低开发成本,为以后的I P核固化打下基础。模块由数据输入单元、运算选择单元和运算处理单元组成,运算处理单元包含加减法运算单元、乘法运算单元和除法运算单元。模块通过数据输入单元提取符号位、阶码位和尾码位;通过运算选择单元决定是何种运算;通过运算处理单元处理相应的运算。模块逻辑框如图4所示。

图4 模块逻辑框

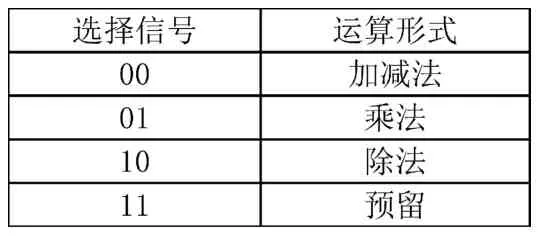

由于只有3个运算单元,选择信号只需2位,具体选择信号与运算单元之间关系见表3。

表3 选择信号与运算单元关系

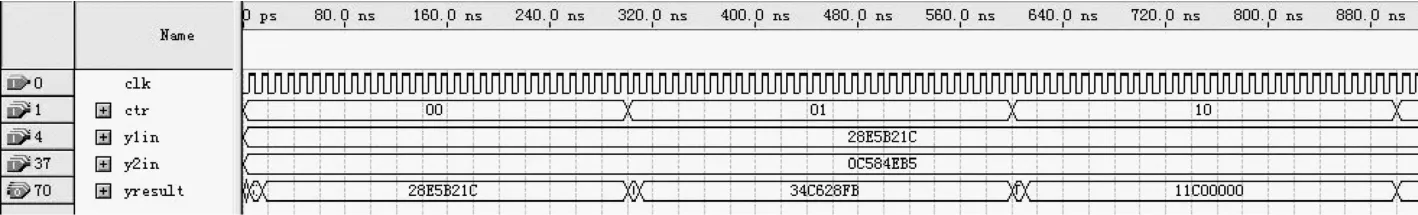

使用硬件描述言语输入和原理图输入,在Altera公司的可编程逻辑器件开发软件Quartus II中经过分析和综合后得到的模块封装图如图5所示,模块综合仿真图如图6所示。

图5 模块封装图

图6 模块综合仿真图

仿真图中clk(1位)是时钟信号,ctr(2位)是运算模式控制信号;y1in(32位),y2in(32位) 为输入信号;yresult(32位)为输出信号。图中控制信号是二进制格式,输入输出信号是十六进制格式。

5.结束语

本文详细介绍浮点运算的加减运算和乘除运算的实现算法和技术,并在此基础上实现三个运算单元的模块化设计。通过Altera公司的可编程逻辑

器件开发软件Quartus II软件仿真,验证了设计的正确性。

[1]刘增明,张文山.嵌入式软件浮点运算精度分析[J].洛阳:航空兵器,2010

10.3969/j.issn.1001-8972.2011.23.034

江苏省自然科学研究基金项目(BK2008367);南京工程学院科研创新基金项目(CKJ2009004)