数字直放站中DLMS算法的FPGA实现

石栋元,刘正平,钱 锐,夏 威,何子述

(电子科技大学电子工程学院,四川 成都 611731)

自适应算法被广泛用来解决数字直放站中存在的回波干扰问题,以降低系统的自激风险。最小均方(LMS)算法由于其结构简单,稳定性好,易于实现等优点,在回波抵消中被广范应用[1]。

但LMS算法在FPGA实现时不能并行计算,这就使得其难以用在高速实时处理的系统中。为了解决此问题,Long[2-3]等人提出了 DLMS(Delayed LMS)算法,同时为了减少延时,Long还提出了用树状结构来实现DLMS算法;Yi[4]和 Ting[5]等人在前人的基础上运用重定时技术,提出的结构既可以提高系统的采样率,又可以得到较快的收敛速度和良好的跟踪性能,但他们所提的结构都是针对的实数,而在数字直放站中,基带所处理的数据是复数,故需要对其进行改进。

本文在Ting所提出理论的基础上,提出了复数DLMS算法的实现结构,由仿真结果可知,该系统的处理速度可达到135 MHz。同时为了节省乘法器资源,笔者还提出了2倍复用的结构,由测试结果可知,16阶2倍复用的DLMS算法实现了回波抵消功能,同时还放大了所接收到的信号,从而实现了数字直放站的功能。

1 回波抵消系统模型

具有自适应回波抵消功能的直放站模型如图1所示。真实回波信道(包含功放)采用FIR滤波器建模,可表示为

图1 具有自适应回波抵消功能的直放站模型

式中:N为通道阶数;[g]T表示转置。

n时刻接收端的接收到的总信号为

式中:x(n)=[x(n),x(n-1),…,x(n-N+1)]T为FIR滤波器的输入信号,它由误差信号反馈回滤波器而形成;y(n)为回波干扰;r(n)为接收到的来自基站的电视信号;v(n)为加性白噪声,其均值都为0,方差分别为和。

从系统接收到的总信号中减去回波干扰估计值,即回波抵消后,可得误差信号

式中:μ是LMS算法的步长,其选取范围为

2 DLMS算法

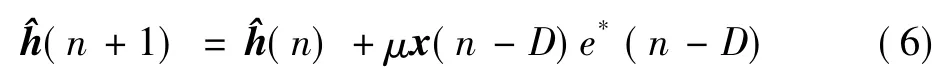

由于LMS算法的3个方程之间存在顺序关系,使其不能并行计算,只能按照算法固有的顺序进行迭代更新,这就使得LMS算法难以用在高速实时处理的系统中。为了解决此问题,Long[2-3]等人提出了 DLMS(Delayed LMS)算法。图2给出了DLMS算法的功能框图。

图2 DLMS算法的功能框图

由图2可知,DLMS算法的权系数更新方程为

由式可知在DLMS算法中,滤波和权系数更新可以同时进行。因此,在相同的时间内其吞吐量是LMS算法的2倍。

对于DLMS算法的性能,Long等人做了相应的分析。权系数更新中引入的延时D对系统的稳态性能影响不大,只要步长μ的取值在式所示的范围内即可。

对比式和式可知,DLMS算法对步长的要求更苛刻,但是通过选取更小的步长,可以灵活地选择所需要的延迟。

3 DLMS算法结构

3.1 复数乘法器的结构

由于该设计的结构是针对复数DLMS算法,故需要先设计复数乘法器。在DLMS算法的滤波和权系数更新中所用的复数乘法形式为

由式可知,构造1个复数乘法器需要4个乘法器和2个加法器。通过对式的化简,可以节省资源。

从而通过增加3个加法器来减少1个乘法器。

如果由式直接构建复数乘法器,其关键路径为T=2Ta+Tm,其中Ta和Tm分别表示执行1个加法器和1个乘法器所需的时间。由于Altera公司Stratix II芯片中含有丰富的寄存器资源,故可以在复数乘法器中插入9个寄存器,以减短关键路径,提高系统的处理速度。此时,复数乘法器的结构如图3所示,其中D为寄存器。由图3可知,此时的关键路径变为T=Tm,假设Tm>Ta。

图3 加入寄存器后复数乘法器的结构图

3.2 复数DLMS算法的结构

图4 8阶DLMS算法的结构图

图4是由Ting所提出的8阶DLMS算法的结构图,在该结构中关键路径为T=Tm,假设Tm>Ta。由于本文针对的是复数DLMS算法,所以图4中所有的乘法器和加法器都要替换成复数乘法器和复数加法器。同时,由图3可知本文所设计的复数乘法器具有两级流水线结构,所以图4中乘法器后面的3D(即3个寄存器)应变为D。此时,复数DLMS算法的结构如图5所示,图中的输入信号和输出信号均为复数。

图5 8阶复数DLMS算法的结构图

图5中的关键路径与图4一样仍为T=Tm。将该结构用Altera公司Stratix II EP2S60F672C芯片实现时,根据Classic Timing Analyzer Tool的分析,如图6所示,该系统可以在135 MHz的时钟下正常工作。

图6 Classic Timing Analyzer对图7结构的时序分析结果

由于在具有回波抵消功能的数字直放站中,基带的系统的时钟为10 MHz,故本文选择图8所示的结构进行2倍复用是可行的。2倍复用的思想是:DLMS模块的处理时钟为系统时钟的2倍,即20 MHz,在第一个时钟周期计算奇数阶,在第二个时钟计算偶数阶,然后将两次所得的值相加得到滤波器的输出。此时,滤波器的输出速度仍为10 MHz。

2倍复用即折叠因子为2的折叠变换。由折叠方程[6],如式所示,可以计算出2倍复用中,每个处理模块中各个节点处所对应的延迟数,具体变换如图7所示。

式中:DF(U→V)为折叠后节点U到V所需的延迟数;N为折叠因子;w(e)为折叠前节点U到V间的延迟数;PU是输入节点处所引入的流水线寄存器;v和u为节点在折叠集中的序号。

在图7中0,1表示节点在折叠集中的序号;2l+0,2l+1表示两路选择器在不同时刻的选通输入。其中,xfilter(n)和xupdate(n)分别表示滤波和权系数更新过程的输入信号;e(n)表示误差信号;xfilter(n)和xupdate(n)分别表示滤波过程的输入信号和权系数更新过程的输入信号。

图7 2倍复用结构变换示意图

由文献[7]可知,在同频数字直放站中,当LMS滤波器的阶数为16时就能满足系统处理时钟频率的要求。故本文用8阶所用的乘法器资源,来构造16阶LMS滤波器,其结构如图8所示,其中One tap的结构如图7所示,图中除了One tap的处理时钟为20 MHz外,其余的处理时钟为10 MHz。

将图5和图8所示的结构分别用Altera公司Stratix II EP2S60F672C芯片实现时,它们所用的资源如表1所示。由表1可知,16阶2倍复用结构所用的乘法器资源和8阶的是一样的,只多用了2%的组合逻辑资源和1%的寄存器资源,而这些资源在Stratix II芯片中非常丰富,故用其来换33%的乘法器是值得的。

图8 16阶2倍复用复数DLMS算法的结构图

表1 8阶直接型结构和16阶2倍复用结构所用资源的对比

4 仿真实验与结果

本仿真实验是根据参考文献[8]进行的,其测试框图如图9所示,其中模拟基站所发射的信号是中心频率为506 MHz、带宽为8 MHz、功率为20 dBm的OFDM信号,如图10所示,接收天线分别接收来自基站的信号和回波,即图9中的a和c,信号叠加后经过一系列处理模块,最后从b端经发射天线发射出去。图中的DDC、EC和DUC分别表示数字下变频、回波抵消,即16阶DLMS算法模块和数字上变频,这3个模块都是在Altera公司的Stratix II中实现的。

图9 全无线环境下ICS直放站系统测试框图

当系统没有加入直放站时,接收天线接收到的信号的频谱图如图10所示。为了对比有、无回波抵消模块时系统工作的情况,该设计采用先去掉EC模块然后再加上该模块的方式,此时发射天线所发射信号的频谱如图11所示。然后将加入了回波抵消模块后,Signal Tap II所抓取的数据导入Matlab画出信号的频谱图,其结果如图12所示。回波抵消之前采样数据的频谱如图13所示,回波抵消后采样数据的频谱如图14所示。

由图11可知,当直放站系统中没有加EC模块时,系统自激了;由图12可知加入EC模块后,系统正常工作。同时,由图13和图14可知,加了EC模块的系统,不仅抑制了回波,还放大了所接收到的信号。

5 结论

本文根据数字直放站的需求,利用pipeline和systolic技术,提出了复数DLMS算法的实现框图。同时为了节约资源,提出了2倍复用结构。由测试结果可知,数字直放站系统在加入DLMS算法模块后,系统就能正常工作,即放大信号和抵消回波。

[1]LEE M,KEUM B,SHIM Y S,et al.An interference cancellation scheme for mobile communication radio repeaters[J].IEICE Trans.Commun.,2009(5):1778-1785.

[2]LONG G,LING F,PROAKIS J G.The LMS algorithm with delayed coefficient adaptation[J].IEEE Trans.Acoustics,Speech,Signal Processing,1989,37(9):1397-1405.

[3]LONG G,LING F,PROAKIS J G.Correction to‘the lms algorithm with delayed coefficient adaptation’[J].IEEE Trans.Signal Processing,1992,40(1):230-232.

[4]YI Y,WOODS R,TING L K,et al.High sampling rate retimed DLMS filter implementations in Virtex-II FPGA[C]//Proc.IEEE Workshop on Signal Processing Systems.[S.l.]:IEEE Press,2002:139-145.

[5]TING L K,WOODS R,COWNA C F N.Virtex FPGA implementation of a pipelined adaptive LMS predictor for electronic support measures receivers[J].IEEE Trans.Very Large Scale Integration Systems,2005,13(1):86-95.

[6]KESHAB K P.VLSI数字信号处理系统:设计与实现[M].陈弘毅,白国强,吴行军,等,译.北京:机械工业出版社,2004.

[7]ANDERSON C R,KRISHNAMOORTHY S,RANSON C G,et al.Antenna isolation,wideband multipath propagation measurements,and interference mitigation for on-frequency repeaters[C]//Proc.IEEE SECON 2004.[S.l.]:IEEE Press,2004:110-114.

[8]李学易,郝禄国,杨建坡,等.同频数字直放站回波干扰消除器的设计[J]. 电视技术,2010,34(7):16-19.