基于NIOSⅡ的声纳主机与显控台之间的RS232通信协议

王 斌,许伟杰

(中国科学院声学研究所(上海研究站),上海200032)

声纳设备一般由换能器(信号转换、收发设备)、信号处理主机(DSP等)和显示控制分机(简称显控台)三部分构成。显控台和主机之间的通信非常重要[1]。

显控台和主机之间的通信距离较远,对通信的可靠性和安全性要求高,但是对通信速度要求不高。所以通信方式可以选择串口通信协议RS232[2]。

显控台上诸多的旋钮、开关以及指示灯、数码管等设备需要丰富的外围接口。这些接口之间具有复杂的逻辑关系。选用FPGA作为显控台主芯片可以满足这些要求。以ALTERA公司的CycloneⅡ开发板为例,其主芯片EP2C8Q208C最多可提供182个用户I/O口,可以满足外围接口要求[3]。在ALTERA公司提供的硬件开发环境Quartus和片上系统开发环境SoPC下,可以非常方便地进行控制模块的开发。也可以构建NIOSⅡ处理器,以及配置NIOS系统自带的硬核,如串口通信模块UART、储存模块 Serial Flash等[4]。

本文利用FPGA芯片设计了一套显示控制分机系统,并且以声纳训练靶为应用背景编制了串口通信协议。

1 利用SoPC Builder构建显控台的片上系统

SoPC Builder是ALTERA公司提供的片上系统(SoC)开发工具,它可以配合QuartusII完成FPGA芯片的CPU以及外围设备的配置工作。

1.1 片上系统的构建

在SoPC Builder的开发环境下,选择ALTERA公司开发的32位RISC处理器NIOSⅡ。标准型的处理器NIOSⅡ/s可以运行在100 MHz的系统时钟下,运算速度超过50 DMIPS[2]。再构建配套的数据存储器SDRAM、程序存储器Serial Flash、系统地址管理器(System ID Peripheral)、编程调试接口(JTAG_UART)以及数码管(SEG)、显示和旋钮(KNOB)、按键(KEYS)等 PIO 接口。

1.2 RS232 Serial Port的结构

对UART的控制主要通过编程寄存器来实现[2]。根据UART的寄存器结构,在SoPC对应的软件开发环境NIOSⅡIDE下建立C语言的结构体UART_ST,代码如下:

2 显控台与主机之间的通信

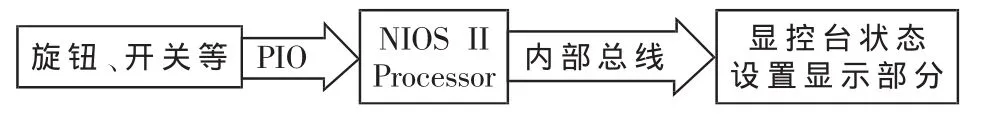

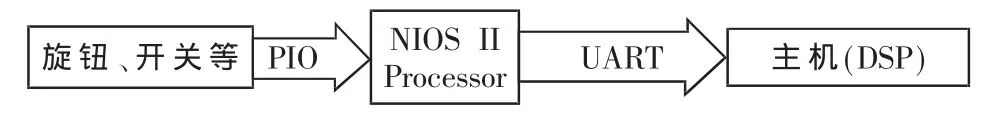

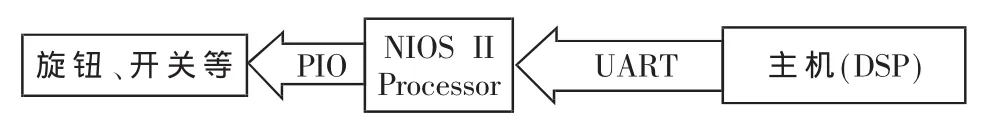

声纳设备有两种工作状态——设置和工作。在这两种状态下,显控台与主机的通信方式有三种,分别如图1~3所示。

图1 设置状态下NIOSⅡ处理器与显控台通信

图2 设置状态下NIOSⅡ处理器通过UART与主机(DSP)通信

图3 工作状态NIOSⅡ处理器通过UART与主机(DSP)通信

在声纳设备工作之前,操作员在显控台要完成开机与参数设置等动作。此时,开关等外围设备会触发处理器的中断处理程序,完成参数设置和显示。这些参数不仅要在显控台显示,还得通过UART发送到主机(DSP),作为主机信号处理运算的某些参数。因为是通过串口发送,所以这些数据要进行适当的分割与编码,并加上地址信息等。

在主机(DSP)接收到开始工作的指令后,主机会把处理过程中或者处理后的数据通过UART发送到显控台,方便操作员实时了解设备的工作状态和工作结果。

3 在NIOSⅡIDE上实现串口通信协议

NIOSⅡIDE是ALTERA公司开发套件中用来进行嵌入式开发的平台。所有软件开发任务都可以在NIOSⅡIDE下完成,包括编辑、编译和调试程序。它支持C/C++语言编程,可以根据SoPC建立的SoC,生成相应 makefile,在编译时,又可以根据makefile生成系统头文件system.h,从而把软硬件隔离开来[5]。

3.1 串口通信协议

在NIOSⅡIDE下用C语言开发通信协议较为方便。由于RS232每帧数据有效数据位为8 bit,所以将unsigned char作为协议中的基本数据类型。在库文件中,这种数据类型被定义为alt_u8。指令的前4位为0,后4位为指令内容。数据前4位为数据的地址信息,后4位为数据内容。

显控台与主机所有通信数据和指令分为三种:(1)显控台处理器发送到主机(DSP)的指令,取值范围为0x00~0x0f。典型的如0x00为开始工作指令,0x0f为停止工作指令,0x01~0x07为通信检查指令。(2)显控台处理器发送到主机(DSP)的数据,取值范围为 0x1x~0xfx。典型的如0x9x和0xax,分别为多普勒频移的低4位数据和高4位数据。(3)主机(DSP)发送到显控台处理器的数据,取值范围为0x0x~0xfx。典型的如0x5x噪声级别。

3.2 程序设计

根据以上分析,以声纳训练靶为例,设计C语言程序。框图如图4所示。

NIOSⅡ嵌入式编程可以直接调用ALTERA的库函数进行操作。例如对PIO的操作函数:IOWR_ALTERA_AVALON_PIO_DATA(BASE,DATA)(写 IO 函数),IOWR_ALTERA_AVALON_PIO_DATA(BASE,DATA)(读 IO 函 数)。也可以构建硬件寄存器的结构,例如UART_ST这样的结构,通过对结构实例化的操作,同样可以方便地编程。本设计中结合了这两种编程的优势,对于结构复杂,操作要求简单的硬件,采用库函数的操作方法,如Flash;对结构较为简单、操作较为细化的硬件,采用寄存器结构化的操作方法,如UART。

图4 程序框图

本文利用FPGA芯片构建了声纳设备的显示控制分机。基于ALTERA公司的 NIOSⅡ嵌入式处理器,建立了片上系统,实现了显示控制分机和主机(DSP)之间的RS232通信协议。在以EP2C8Q208C为主芯片的FPGA开发板上,实现了硬件系统的构建和软件编程以及下载。此显示控制分机应用在一体化声靶中,工作稳定可靠。由于片上系统构建的灵活性,所以这种显示控制方案在声纳设备中具有很好的可扩展性,便于维护和升级。

[1]蒋均齐.鱼雷声靶技术研究[D].长沙:国防科技大学,2006:8-9.

[2]李金力,刘文怡,彭旭峰.基于 FPGA的 RS232异步串行口 IP 核设计[J].电子设计工程,2009,17(8):31-35.

[3]Altera Corporation.Cyclone II Device Handbook[S].2007(1):12-34.

[4]张新喜,许军,杨雨迎,等.基于 SoPC技术的战车综合显控终端设计[J].火力与指挥控制,2008,33(增刊):109-112.

[5]洪胜峰.基于嵌入式技术的军用车辆车载显控终端的研制[D].青岛:中国海洋大学,2007:25-26.