天河-1A互连系统的接口设计*

刘 路,张 磊,谢 旻,王永庆

(国防科学技术大学计算机学院,湖南 长沙 410073)

1 引言

THNet是国防科学技术大学研制的最新一代高速互连交换网络,包括两款自主研制的ASIC芯片,即交换芯片NRC 和网络接口芯片NIC。THNet用于构建大规模计算机系统的专用互连网络,使用NIC接口卡可访问各种不同类型处理器节点和I/O 节点。NRC交换机可以配置为任意拓扑结构。

THNet在数据链路层具有可变长的包格式,对每条链路实行基于信用的流控和16位Rolling CRC校验[1],链路层具有基于滑动窗口的重传机制[2],可保证数据在链路层正确传输。在物理层上,THNet使用全双工高速串行链路,任意两个端口间可实现数据交换,在长至30米的光纤或电缆上仍可实现流水传输,获得双向160Gbps的峰值速率。

NRC交换芯片使用虫孔路由机制。在任意网络拓扑结构中,多端口NRC通过链路和其它NRC或单端口的网络接口相连。NRC 内部采用瓦片式交换结构,具有流控和输入缓冲功能,当收到包头并解码后,包便立即送到选定的输出通道上。多个包可以同时流过NRC。16端口NRC 交换芯片的吞吐率高达2.56Tbps,数据包从进入NRC 到离开,产生的时延至多100ns。

NIC网络接口芯片做为网络和节点间的桥梁,其设计目标是获得延迟更低、带宽更高、更可靠和扩展性更好的性能。它的主机接口支持PCI Express 2.0标准,能提供16×5Gbps的传输带宽。网络接口为8×10Gbps的全双工高速串行链路。内置DRAM(Remote Direct Memory Access)接口,可外接256MB 的DRAM。以下就NIC 芯片设计与实现的技术途径及性能测试结果进行介绍。

2 通信机制

NIC支持短消息MP(Mini Packet)和远程内存直接访问RDMA 两种数据传输机制。MP是长度为128字节的报文,其前8字节被称为MP 头,包含传输这个MP所需的控制信息,后120字节为用户数据。MP 从发送方传送到接收方后,写入MP头指定的某个MPQ(MP Queue),以中断或查询方式通知接收方。MPQ 是MP 接收队列,位于节点主存中,是一个物理地址连续、页面边界对齐、循环使用的缓冲区。NIC 提供的RDMA,可将虚地址连续的内存数据块在节点间传输,进程只需提供发送方数据块首地址、接收方首地址、数据长度以及RDMA 类型等信息,即可启动RDMA。RDMA 完成后,可采用各种不同的方式通知接收方或发送方进程。例如,RDMA 描述符中可携带一个接收方地址和16字节的数据,当RDMA 完成后,将这16字节数据写入指定的地址,接收方进程查询该地址是否有数据写入即可知道RDMA 是否完成,这被称作事件机制。也可以选择在RDMA后紧跟着传输一个MP或立即数RDMA 来通知接收方。事件机制既可以采用查询方式,也可以采用中断方式。RDMA 使用的地址,既可以是虚地址,也可以是物理地址,对用户级通信和内核级的应用都能很好地支持。进程用提交描述符(Descriptor)的方式启动数据传输。描述符的内容规定了RDMA 的类型、源节点地址、目的节点地址、RDMA长度、传输结束后以何种方式通知源节点进程和目的节点进程,以及RDMA 传输的一些控制信息。NIC 的RDMA 传输机制不需要在发送方和接收方之间建立连接,数据的接收方地址已经在描述符中了。进程之间可以使用MP 来交换所需的RD-MA 地址和事件地址。

2.1 虚拟接口

NIC 实现了32 个虚拟接口VP(Virtual Port),VP 的控制寄存器组的地址被映射到用户空间,用户进程可以直接访问这些寄存器,进而通过VP直接访问NIC,完成各种用户级通信操作。VP实现了硬件资源的虚拟化,为每个进程形成一个独占使用硬件的编程视图。每个VP 都有自己专用的描述符队列DQ(Descriptor Queue)、MP接收队列MPQ和完成队列CQ (Completion Queue)。NIC既实现了片上DQ,也可在主存中扩展为容量更大的主存DQ,用于接收进程提交的描述符。当进程使用PIO 写提交描述符时,它将描述符数据直接写入片上DQ。当进程使用DMA 方式提交描述符时,它将描述符数据先写入主存DQ,然后通知NIC 用DMA 读回描述符。NIC 按round-robin法则处理32个VP的描述符,可保证每个VP内描述符是顺序执行的,但不保证各VP间描述符的执行顺序。每个VP 内的描述符的执行可以是非阻塞的,也可以是阻塞的,由描述符本身的控制字段决定。MPQ 和CQ 在主存中,大小可配。CQ 的组织结构与MPQ 类似,执行完毕的描述符置上完成信息字段后,可以被写入CQ。描述符是否写入CQ 由软件决定,例如,软件可设定当发生传输错误时才将描述符写入CQ。

2.2 基于网络接口的虚实地址变换

NIC用硬件实现虚实地址变换表ATT(Address Translation Table),以便用较低的资源代价换得最佳地址变换性能。所谓最佳地址变换性能[3]是指:每次地址变换的开销最小,没有或几乎没有地址变换失效,可提供足够多的地址变换表项。

NIC 外接DRAM 存放ATT 表,容量为256M字节,可存放32M 个物理页面地址。在用户进程注册内存时,驱动程序锁定用户进程空间的数据页面,计算页面的基地址(物理地址),按照与用户进程虚地址一一对应的顺序写入ATT 表,建立起连续的用户进程虚地址到非连续物理地址的映射关系。

RDMA 传输的虚实地址变换在NIC 中完成,首次地址变换与启动DMA 的准备工作并行进行,隐藏了首次地址变换开销。换页的地址变换与数据发送过程重叠,其开销也被隐藏,这样能很好地支持RDMA 操作的流水性,充分利用硬件的带宽性能。由于ATT 表的容量足够大,能覆盖绝大多数应用进程的全部地址空间,对可以访问的用户空间没有大小和位置的限制,不会产生地址变换失效,也就没有地址变换失效开销。用户进程内存注册具有较大的软件层开销,但注册一般在通信开始前完成,对通信过程本身没有影响。

数据发送方使用物理地址读主存中的数据,在接收方同样也使用物理地址将从网络上接收到的数据写入主存。一次完整的用户级数据传输至少要执行两次地址变换。对于接收方的地址变换,可以在发送方执行,也可以在接收方执行。但是,如果在发送方执行接收方的虚实地址变换,会使得换页查表、错误报文隔离、安全性检查以及处理多对一通信等方面的处理变得很困难。NIC 采取了后一种地址变换策略,即所有的虚实地址变换都在距离它要访问的主存最近的NIC进行。

依赖ATT 表的片上虚实地址变换,进程仅使用发送方和接收方的虚地址信息就能将数据块在节点间直接传输,不需要任何额外的数据拷贝,传输过程也不需要操作系统的参与。

2.3 基于PIO 的描述符提交

传统的用户级通信中,描述符队列在主存,进程将描述符准备好后,向NIC执行一次PIO 写(置门铃标志);NIC 收到门铃后,执行一次DMA 读,从主存中将描述符取回,然后分析描述符,根据描述符的请求再次执行DMA 读,取回要传输的数据,再将数据打包发走。采用上述方法,一次PIO写加两次DMA 读才能读回数据,这导致了RDMA 的启动开销较大,对于几十字节的细粒度数据,RDMA 传输的通信延迟就会比较大。NIC 芯片为每个VP 实现了一个512深、64位宽的DQ,进程用PIO 写将描述符写入DQ,可以节省一次DMA 读的开销。NIC 不能控制进程调度,进程上下文切换随时可能发生,进程可能没有写完描述符就被切换出去,需要采取措施保证描述符的原子性。NIC为每个DQ 设置了一个检查模块,将描述符数据依次从DQ 中读出,确定描述符完整后,再进行处理。

一次PIO 写可传送64位数据,而NIC定义的描述符最大有128个字节,需要执行16次PIO 写才能将一个描述符全部写入DQ。在设计过程中发现,即使进程连续执行PIO 写,可是在PCIE 总线接口处“看到”的PIO 写入的数据并不是连续写入的,而是每间隔16个时钟周期才写入一个数据。PCIE接口的时钟频率是250MHz,写完一个128字节的描述符耗时4ns*16*16≈1μs,这比一次DMA 读数据的时间(约0.8μs)还要大。通过测试与分析,认为原因与桥芯片对PIO 写的处理有关。Intel的Intel®64和IA-32体系结构中[4],其存储器类型中有一类是WC(Write Combining)类型,对这种类型存储器的写可以被推迟,后续的写在WC缓冲区中被合并,以减少对存储器总线的访问次数。Intel 的CPU 提供了一种写合并缓冲(Write Combining Buffer),一般有64 个字节,可将地址连续的PIO 写的数据合并后,再以burst方式驱动到数据总线上。如果128字节的描述符按这种方式处理,只需要两次可“看到”的PIO 写就可以写入NIC的DQ 中,耗时约4ns*(16+16+16)≈0.2μs。我们将NIC 上的DQ 地址空间映射为WC类型的存储器,就可以实现PIO 的写合并,这是通过对MTRR[4](Memory Type Range Registers)进行编程或在页面属性表PAT[4](Page Attribute Table)中配置参数实现的。

为兼顾用户使用的灵活性,NIC也支持以传统的DMA 方式提交描述符,这时其描述符队列在主存用户空间。NIC支持以PIO 方式提交描述符与DMA 方式提交描述符在同一个VP 中混合使用。NIC还支持立即数RDMA 传输,它利用描述符中的空闲区域,将少部分数据夹带在描述符中,与描述符一起提交到NIC,省却了一次DMA 读取数据的开销,这种机制可显著减小细粒度数据的传输延迟。NIC支持1~128字节的立即数传输。

2.4 RDMA 数据拆分与对准

DMA 跨越PCIE 总线读主存数据的延迟较大,我们没有办法消除首次DMA 读的延迟,但可以设法隐藏后续DMA 读的延迟,并且付出尽可能小的硬件代价。NIC 启动RDMA 传输时,将总的数据块拆分为多个1KB的小数据块,然后向PCIE接口提交多个小数据块的读请求,只要RDMA 数据接收FIFO 有足够的空闲空间接收挂起的读请求所要求的数据的合计长度。PCIE 接口内部将1 KB的用户读请求再拆分生成128 字节或256 字节的读请求报文发至PCIE 总线(由参数Max_Read_Request_Size决定)。PCIE 总线MASTER事务的最大数据长度为4K 字节,我们将拆分的长度定为1K 而不是4K 字节,拆分算法的复杂性几乎一样,却能够在使用最小尺寸的数据接收FIFO的情况下有效隐藏PCIE 读延迟。NIC 的RDMA数据接收FIFO 大小为8K 字节。

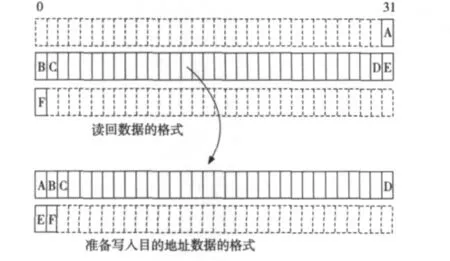

NIC支持字节边界对齐方式RDMA 传输,数据块的发送方首地址和接收方首地址都由用户指定,没有任何限制。发送方地址用于从发送方主存读数据,接收方地址用于把数据写入接收方主存,NIC内部数据帧的宽度是32字节,发送方首地址和接收方首地址相对于数据帧首的偏移可以不同,这将导致数据在数据帧中位置的变化,需要将按发送方地址格式读回的数据重新对准成接收方地址要求的数据格式。例如有如下传输:数据块的长度是34字节,发送方的地址偏移是31,接收方的地址偏移是0。那么,从发送方主存读回的数据的格式和准备写入接收方主存的数据格式如图1所示。可以看出,虽然有效数据的长度是一样,但是从发送方读回的数据在首帧的偏移是31,帧数是3,准备写入接收方的数据在首帧的偏移是0,帧数是2。

Figure 1 Data alignment图1 数据对准

NIC中用地址对准模块解决这个问题。在NIC中设置了两组FIFO,一组是RDMA 数据FIFO,存储从主存中读回的数据;另一组是RDMA 发送数据FIFO,存储经过地址对准模块变换的数据。地址对准模块将数据对准与组装网络报文的任务结合在一起完成,尽量减少数据传输通路上的节拍数并使对准过程流水起来。对准模块把数据的目的地址按128字节边界进行拆分,按拆分后的地址进行数据对准,得到的网络报文到达目的节点后,都是对齐128字节边界的,在目的节点只要再做一次地址变换,就可以很规整地写入目的节点主存中。

2.5 聚合通信

NIC实现了基于控制报文CP(Control Packet)触发的描述符队列处理机制,以支持卸载的聚合通信。其基本思想是:描述符在DQ 中排队,但描述符的执行需要某种触发机制,既可以由软件主动启动,也可以是网络中接收的报文状态达到一定条件而启动。将聚合通信算法树构造到NIC 中的方法是:软件先通过算法构造过程计算当前任务在算法树中所处的位置,以及当前任务需要执行的通信操作;然后向DQ 中提交对应的通信操作的描述符,但控制这些描述符的执行,只有在特定条件满足后才执行。

控制报文CP是一种特殊的MP报文,在它的MP头增加了一些控制字段,使它的行为不同于普通MP的行为,以达到一个NIC 的VP 能够控制另外一个NIC的VP上的通信操作的目的。其功能有:CP 到达目的VP 后,能够启动目的VP 的DQ 中已排队描述符的执行;CP 携带的数据由用户控制是否写入目的VP 的MPQ 中;CP 携带的数据由用户控制是否替换目的VP 的DQ 中排队的MP描述符中的数据。

NIC为每个VP设置一个CP 计数器,软件用户可以用它来对到达的CP报文进行计数,每收到一个CP报文,就触发检查描述符队列的动作,将计数结果与DQ 中排队的CP描述符中设定的CP报文个数进行比对,如相符就启动描述符队列的执行。启动描述符执行后,CP计数器减去描述符CP值并继续计数。由于每个任务进入聚合通信的时间不能精确同步,可能会出现当CP报文到达目的VP时,目的VP的DQ 中还没有提交描述符的情况,但此时对CP报文还是会进行计数,CP报文也可以按用户设置的控制位被写入MPQ 中。

3 芯片结构与实现

NIC芯片结构如图2 所示。它实现了三个DMA 引擎,分别称为0#、1#、2#引擎。0#引擎处理本地RDMA 写类型描述符,负责读本地主存中的数据。1#引擎处理远地节点送至本地的RDMA 读类型描述符,也读本地主存中的数据,这些数据是远地节点请求的。这两个引擎各自独立工作,产生的读数据请求2 选1 仲裁后写入同一个DMA 读请求缓冲区。读回的数据分别进入各自的数据FIFO,每个FIFO 大小为8K 字节,足够隐藏PCIE读延迟。数据通过对准模块和发送数据FIFO,再由链路发送到链路接口。本地RDMA 写类型描述符产生的数据和远地RDMA 读类型描述符产生的数据在链路层使用不同的虚信道,链路报文组装发送模块按round-robin法则发送数据,其中还需要用到虚信道发送信用、滑动窗口重传、缓冲区是否空闲等条件进行调度。2#引擎专门处理写事务,所有主存用户数据的写入以及中断的产生都由2#引擎负责。

链路发送模块负责链路报文的组装和发送。它从片上路由表中取出路由场填入报文的头flit,不仅要将网络报文数据分割转换成链路报文、流水地发送出去,还要应付在这个过程中随时可能出现的特殊情况:重传缓冲区不可用信号置1。一旦这个信号升起,表明重传缓冲区中没有空闲的缓冲块来接收链路报文flit,这时,链路发送模块就得及时“刹车”,并保留当时的发送状态,处理好其它流水线的暂停,保存中间结果,等重传缓冲区不可用信号无效后,再次启动发送数据。NIC中该模块的实现效率很高,对于一个RDMA 传输的所有报文,仅在发送第一个报文时额外增加了一拍用于查表读路由场,其它任何时候只要链路允许,都可以每拍流出一个链路报文flit。

链路报文处理模块负责将网络输入的链路报文还原成网络报文,并且对报文的完整性和正确性进行检测,剔除头尾标志不全、超长、迷路、数据错等不合格报文,不让错误报文数据被误写入主存,避免主机因错误的DMA 写操作导致死机,这种机制称为脏包丢弃。该模块可以发中断通知主机有脏包丢弃,被丢弃的脏包保存在错误缓冲区,用户可查看,该功能在调试时很有用。

链路接口完成基于滑动窗口的重传、信用维护、发送方完整性检查、接收方完整性检查、链路状态维护、发送数据的仲裁、CRC校验逻辑等功能。

Figure 2 NIC architecture图2 NIC芯片结构

主机接口支持PCI Express 2.0 标准,16lanes,速率为5Gbps,支持链路宽度、速率自动协商,支持链路反转、极性交换功能。在事务层之上提供一个用户接口模块,实现PCIE 报文的解析和封装,以及TC-VC映射、响应超时管理、端到端数据校验、数据错误检测、电源管理、高级错误报告等功能,以简化用户数据的发送和接收。用户接口模块中,PIO 模块负责描述符的发送和寄存器的读写;DMA 模块将DMA 读写请求发送给主机,将接收到的读响应数据分送到各自的数据FIFO;中断处理模块将中断请求转换为PCIE 中断报文,支持INTx和MSI两种中断类型。

NIC芯片没有内嵌微处理器,所有功能都用硬件逻辑实现。NIC采用标准单元90nm 工艺,8层金属,芯片尺寸10mm×10mm,芯片规模1 200万门,采用倒装BGA 封装,引腿数个673。支持IEEE 1149.1JTAG边界扫描测试,系统扫描链用于芯片生产测试和板级导通测试,用户扫描链用于用户逻辑状态观测与芯片调试,支持扫入和扫出功能。芯片最大功耗18W。NIC 实现了三个PLL,分别给各外部接口和核心逻辑提供时钟,核心逻辑的工作频率是312.5MHz,DRAM 接口的工作频率是200~266MHz。

4 性能评测

测试平台使用两台SMP 服务器,CPU 为2.93GHz的Intel至强系列X5670 处理器,6 核,运行2.6.32 版的Linux 内核。在服务器PCIE 2.0总线上安装NIC 接口卡,工作频率5GHz,链路数为16,用光纤直连,构成最短传输链路。

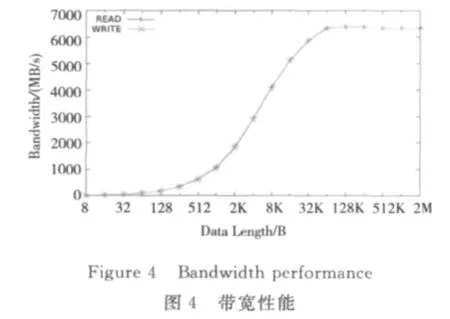

节点间通讯延迟测试程序使用Ping Pong方式,测试结果如图3所示,用DMA 方式提交描述符的最小延迟为2.5μs,使用立即数RDMA 的最小延迟为1.95μs。如果采用PIO 写提交描述符,测到的RDMA 最小延时为1.57μs。RDMA 带宽测试中,采用流水传输方式,由发送方进程连续提交多个RDMA 写操作,然后等待接收方进程收到所有数据后的应答,收到应答后,计算单向数据传输带宽。测试结果如图4所示,单向的数据传输峰值带宽达到6.34GB/s,考虑到必要的硬件协议处理开销,这个带宽值基本上达到了PCIE 总线和网络链路所能提供的极限应用带宽(接近80%)。表1给出了当前用于超级计算机的几种主要互连网络的性能[5],其中既有定制的互连网络,也有基于通用I/O 总线的商用互连网络产品,如Infiniband、Infinipath、Myrinet。与它们相比,NIC 的延迟与带宽性能具有较大的优势。

为了验证NIC 硬件提供的聚合通信机制,我们对软件构造的相应算法树进行了测试,图5和图6给出Barrier和Bcast的测试结果。这个测试是在天津超算中心“天河一号”主机上进行的。可以看出,在4 096节点规模时,基于NIC 硬件机制的通信对比使用点点通信时,可以将聚合通信的延迟降低4倍以上。

Table 1 Some bandwidths and latencies for various networks表1 几种互连网络的带宽和延迟性能

5 相关工作

目前最成功的商用互连产品是Infiniband,在2010年世界TOP 500排名中[6],有42.6%的超级计算机采用Infiniband做互连系统。Infiniband是I/O 标准化组织制定的一种连接服务器、网络设备和存储设备等交换结构的互连规范[7],由不同的公司开发生产符合其规范的硬件产品,如Mellanox、Qlogic等。Infiniband规范定义了四种传输模式:可靠连接、不可靠连接、可靠数据报、不可靠数据报。这四种模式中,Infiniband规范要求主机适配器HCA 硬件实现可靠连接、不可靠连接、不可靠数据报这三种,对可靠数据报不做要求。可靠连接是目前基于Infiniband实现MPI实际使用的传输服务。在这种模式下,任意两个进程在通信前,都必须各自产生一个QP对,与对方进程的QP对建立连接后才能进行通信。使用QP 对建立连接会耗费节点的内存资源,且耗费量随系统节点数目(进程数目)的增加而呈平方关系增加,这种工作模式给系统的可扩展性带来严重影响。假设系统有N 个节点,每个节点上有M 个core,每个core上运行一个进程,所有进程都要相互通信,则每个节点需建立的连接的总数为O(M2N)个[7]。假设每个QP对只占用4K 字节内存,则每个节点上QP对占用内存的总数为O(M2N*4K)字节。日本“京”超级计算机系统[8]安装的CPU 数是80K,每个CPU 有8 核。如果采用Infiniband互连,则每个节点建立连接所需的内存将达到82*80K*4K=20GB,考虑到每个节点还要为与之通信的进程预定义一定数量的数据接收缓冲区,所需的内存数量将比20GB 大得多。文献[9]为了解决Infiniband可靠连接的可扩展性问题,提出了可扩展的可靠连接XRC(eXtended Reliable Connection)的方案。在XRC中,源进程只需与目标节点建立一个连接,目标节点上所有的进程共享这个连接与源进程通信。这将极大缓解Infiniband的可扩展性问题。但是,即使这样,在未来几年构建100P(Petascale)或E(Exascale)级系统时,Infiniband的使用仍然会受到限制。据估算,即使每个CPU上集成个64核,每核每拍流出8个浮点运算结果,CPU 工作频率2GHz,单CPU 的浮点运算能力也只有64*8*2=1 024GFlops/s,构建E 级系统所需的CPU 个数将为1M 个。如果使用基于XRC连接的Infiniband互连,每个节点建立连接所需内存64*1M*4K=256GB,这几乎是不可能承受的。除非Infiniband的连接机制进一步改进,一个进程只需要一个QP 对就可以与其它所有进程进行通信。所以,E 级超级计算机的互连不太可能采用Infiniband,只能是定制的。NIC 实现的无连接RDMA 机制、MPI实现都基于RDMA 读/写操作,具有很好的可扩展性,在研制下一代面向100P或E级超算系统时可以继承使用。

在高维mesh/torus网络中,采用自适应路由可使全系统节点获得均衡的带宽和延迟性能,减少网络拥塞和热点。如Cray的Gemini[10]实现了自适应路由。自适应路由能极大改善网络性能,但硬件实现难度较大,如在交换层要避免死锁,在接收端需要识别机制来判断乱序到达的报文是否收齐等。很多互连系统采取的路由策略是确定性路由,如Infiniband采用分布式确定路由[7],“京”系统的Tofu互连采用确定性路由[8]。“天河一号”的互连采用源路由,NIC 中采用了小尺寸的链路报文长度,每个链路报文的长度为160个字节,分拆成5个flit进行传输,每个报文的净数据载荷为128个字节,在交换层传完1个报文只需5个时钟周期。相比于Infiniband的最大报文长度4K 字节,Tofu互连的最大报文长度为1 920字节,在都采用确定性路由策略时,NIC的小粒度报文策略能较好地缓解网络拥塞,减少网络热点的产生,且NIC 使用小粒度报文,仍能获得理论峰值带宽80%的实测带宽。

很多互连系统硬件有选择地支持某些聚合通信操作,如IBM 的BlueGene/L[11]有独立的reduction和barrier 网 络;QsNet硬 件[12]支 持broadcast、barrier及卸载的reduction;Tofu互连[8]支持barrier。NIC中利用CP 报文触发的描述符队列处理机制,能够将聚合通信操作卸载到网络接口中执行,能大幅加速broadcast和barrier的执行。

6 结束语

NIC 实现了无连接、零拷贝、用户级通信的RDMA 传输机制,具有较好的可扩展性,支持的节点数可达16 384个,对目前主流的多核CPU 的运用也有较好的支持。NIC 已成功应用于天津超算中心“天河一号”超级计算机。“天河一号”的Linpack实测峰值性能达到每秒2.566千万亿次浮点运算,在2010年世界超级计算机TOP 500中排名第一[6],实现了中国在高性能计算领域的重大突破。下一代面向100P 或E 级规模超算系统的研制,对互连网络将有更高的要求,网络在面对瞬发失效和硬件永久失效时要能保证正常工作。在NIC中我们已经实现了链路级的可靠传输(报文级可靠性),下一步我们要基于硬件实现端到端的可靠传输(消息级可靠性),进一步提高系统网络的可靠性和可用性。

[1]Maddox R A,Singh G,Safranek R J.Weaving high per-formance multiprocessor fabric[M].Santa clara:Intel Press,2009.

[2]Tanenbaum A S.Computer networks[M].4th Edition.San Antonio:Pearson Education Inc,2002.

[3]Schoinas I,Hill M D.Address translation mechanisms in network interfaces[C]∥Proc of the 4th International Symposium on High Performance Computer Architecture,1998:219-230.

[4]Intel® 64and IA-32architectures software developer’s manual[EB/OL].[2010-05-17].http://www.intel.com.

[5]Overview of recent supercomputers[EB/OL].[2010-05-17].http://www.hpcresearch.nl.

[6]Top500_201011.xls[EB/OL].[2010-05-17].http://www.top500.org/.

[7]InfiniBand Trade Association.Infiniband architecture specification,version 1.2.1[EB/OL].[2010-05-17].http://www.infinibandta.org.

[8]Toyoshima T.ICC:An interconnect controller for the Tofu interconnect architecture[C]∥Proc of A Symposium on High Performance Chips-Hot Chips 22,2010:1.

[9]Koop M J,Sridhar J K,Panda D K.Scalable MPI design over Infiniband using eXtended reliable connection[C]∥Proc of 2008IEEE International Conference on Cluster Computing,2008:203-212.

[10]Alverson R,Roweth D,Kaplan L.The Gemini system interconnect[C]∥Proc of the 18th IEEE Symposium on High Performance Interconnects,2010:83-87.

[11]Almási G,Archer C J,Erway C C.Optimization of MPI collective communication on BlueGene/L systems[C]∥Proc of ICS’05,2005:253-262.

[12]Roweth D.HPC interconnects.A review of current products and introduction to QsNetIII[EB/OL].[2008-02-10].http://www.epcc.ed.ac.uk/msc/programme-information/guest-lectures/2007-2008/duncan-roweth-talk.