单通道恒模抗干扰民航VHF接收机设计与实现

吴仁彪,王心鹏,胡铁乔,石庆研,汪万维

(中国民航大学天津市智能信号与图像处理重点实验室,天津 300300)

随着国内电信业和民航业的快速发展,VHF地空话音通信系统受到的无线电干扰越来越多,严重威胁航空安全。目前民航VHF地空话音通信系统主要使用进口电台,其不具备干扰抑制功能。对于空管无线电干扰问题,现行的主要解决措施是:改频、监测和清查等被动的非技术手段,效果很不理想。因此,研制出具有自主知识产权的民航VHF地空通信自适应干扰抑制系统具有重要的现实意义。

随着EDA技术的高速发展,数字信号处理器的性能在不断的提高。本接收机的信号处理平台采用FPGA和DSP作为数字信号处理芯片,使用Verilog[1]和C作为编程开发语言,以DSP作为控制芯片,在FPGA内部实现了单通道恒模干扰抑制系统。当存在恒模干扰时,系统抑制干扰的过程如下:首先对信号进行载频估计,然后利用陷波器将受干扰的AM信号分离为载波和去载波信号,最后使用非线性最小二乘方法提取恒模干扰信号,将去载波信号与干扰信号相减得到去载波的AM信号,经解调和低通滤波输出清晰的话音信号,实现抗干扰的功能。

1 单通道恒模干扰抑制算法

文献[2-3]中提出了基于非线性最小二乘方法的单通道恒模干扰抑制算法,提取恒模信号的基本思想如下。设恒模信号为

其中:α表示未知恒模信号的幅度;{φ(n)}为未知恒模信号的相位序列;n为采样快拍;N表示采样快拍数。

建立关于 α 与{φ(n)}N-1n=0的最小化准则

其中:e1(n)表示去载波信号经正交变换后得到的复信号。从最小化式(2)所示的代价函数,可得恒模干扰信号序列的幅度估计

恒模干扰信号序列的相位估计为

则恒模干扰信号估计值为[2-3]

基于非线性最小二乘的恒模信号估计算法,避免了一般自适应干扰抑制方法中的收敛和步长因子选取等问题,适合作为系统实现时使用的算法。将抑制载波后的受干扰信号直接与估计出的恒模干扰进行相减,可得到有用信号。

2 系统设计

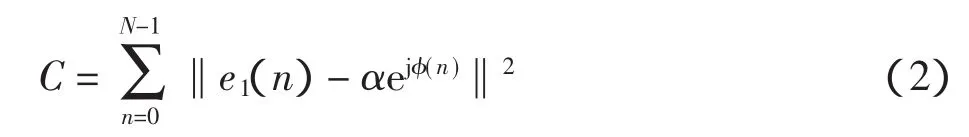

单通道恒模抗干扰接收机主要由射频前端和信号处理平台两部分组成,系统框图如图1所示。射频前端采用两级混频的超外差式结构,其输出为70 MHz的中频信号。信号处理平台以FPGA-XC2VP30和DSP-TMS320C5410A为处理器,以单通道恒模干扰抑制算法为核心对数据进行处理。FPGA的特点是对数据的并行处理能力强,对结构不复杂的算法处理效率较高。C54系列的DSP具有低功耗的特点,使用C语言可对其进行开发调试。本系统中恒模干扰抑制算法在FPGA中完成,控制部分与载频估计在DSP中完成。由于DSP中程序为顺序执行,处理速度慢,因此与仅使用DSP作处理器的抗干扰系统[6]相比,基于FPGA和DSP的抗干扰系统具有处理速度快,实时性好,功耗低等优点。

图1 单通道恒模抗干扰民航VHF接收机Fig.1 Single-channel constant modulus anti-interference civil aviation VHF receiver

接收机的工作过程如下:天线接收到的甚高频信号经射频前端处理转化为70 MHz中频信号后,经40 MHz采样、下变频、低通滤波处理得到载频频率为50 kHz的信号。由于后续模块算法复杂,使用较低的采样率更有利于对FPGA中乘除法器等IP核进行分时复用以节省硬件资源,因此在满足奈奎斯特采样定理的前提下将采样率降低为200 kHz。对降速后的信号利用Goertzel算法[4]进行载频估计,为避免恒模算法的误捕获现象进行陷波处理[5],对去载波信号进行正交变换得到复信号,利用单通道恒模干扰抑制算法对干扰信号进行实时估计,将去载波受干扰信号与提取的恒模干扰相减,其输出为抑制干扰后的去载波AM信号,经相干解调和低通滤波处理,通过数模转换便可得到清晰的话音信号。

3 硬件设计

3.1 射频前端设计

射频前端采用超外差接收结构,主要性能指标为:接收频段为118~137 MHz,灵敏度-80 dBm,动态范围40 dBm,输出中频频率为70 MHz,输出最大幅值±0.80 V至±1 V。射频前端的硬件框图如图2(a)所示,实物图如图2(b)所示。由上至下的三路通道分别为两路接收和一路发射通道,本接收机使用上方的一路作为接收通道,左端为射频输入,右端为中频输出。来自天线的信号经过低噪声放大、两级混频、带通滤波(BPF)、中频放大和自动增益控制(AGC)后输出载频为70 MHz的中频信号。其中第一级本振的频率由基准频率和可变频率两部分组成,基准频率为613 MHz,可变频率的数值由单片机进行设置,以满足民航VHF通信760个通道选择的要求。第二级本振频率固定为425 MHz。射频前端工作电压为5 V。

图2 抗干扰接收机射频前端Fig.2 RF front end of anti-interference receiver

3.2 信号处理平台设计

图3 抗干扰接收机信号处理平台Fig.3 Signal processing platform of anti-interference receiver

信号处理平台的硬件框图如图3(a)所示,实物图如图3(b)所示。处理平台由FPGA、DSP、中频接收通道、中频发射通道、语音通道、AGC接口、控制接口和电源构成。在接收通道中使用AD9244对中频信号采样,发射通道中使用AD9777将FPGA内部的数字信号转换成载频为70 MHz模拟AM信号,再上变频至民航VHF频段后通过天线发射出去。在语音通道中使用LTC1864对话音信号进行采样,使用LTC1655对FPGA处理后的信号进行数模转换并输出至扬声器。信号处理平台工作电压为5 V。

4 软件设计

4.1 Matlab算法定点化

FPGA中处理的数据均为定点数,而Matlab仿真程序中的数据为浮点数。在工程实现前需对浮点算法进行定点化处理,以保证在变量均为定点数时算法的性能和浮点时保持一致,处理过程如图4所示。其中,生成数据源方法为:在FPGA程序中找到与Matlab仿真算法起始处相对应的位置,测试FPGA中该模块输入数据的幅度变化范围,将Matlab中的仿真数据源放大到此范围并取整,以保证其与FPGA中的数据源幅度相一致。计算误差的方法为:设浮点程序中的变量为x,定点化后该变量为xf,定点化时该变量的放大倍数为M,设误差e为xf/M与x对应元素相减后取绝对值,设定误差门限E,当误差e中的最大值em<E时认为本次定点化合理;当em≥E时重新选择放大倍数,再次进行定点化处理。最后,确定出定点算法中各变量的位宽,在FPGA程序设计中对相应变量使用已确定的位宽,这样可保证系统在运行时所有变量都不会发生溢出。

图4 定点化处理流程图Fig.4 Flow chart of fixed-point processing

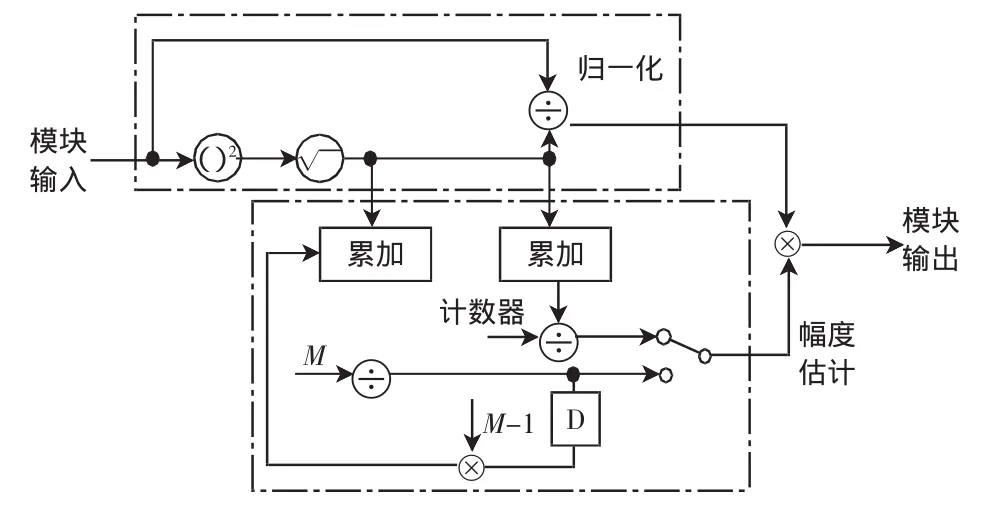

4.2 FPGA程序设计

FPGA的程序设计建立在文献[2-3]中已完成的仿真实验和定点化处理基础上,设计时采用了模块化的方法,将芯片内部资源划分为下变频、低通滤波、抽取滤波、陷波、正交变换、恒模干扰实时估计、解调滤波等模块。下面给出系统的核心——恒模干扰实时估计模块的原理,其内部结构如图5所示。模块输入数据为抑制载波后的受干扰复信号e1(n),对其归一化得到带有相位估计(n)的变量 ejφ^(n)。式(4)中的采样快拍随时间单调递增,而硬件系统中变量的数据范围有限,因此要计算幅度估计(n)应使用如下方法:设定一个门限,利用计数器对采样快拍n进行计数,当计数值小于门限时,切换开关位置如图5中所示(n)由对模块输入数据的模值进行累加并对当前采样快拍n取平均的方法得到。当计数值大于门限时,开关进行切换,将式(4)中的采样快拍n固定为常数M,α^(n)由当前时刻与前M-1时刻数据的模值累加和对M 取平均得到。将幅度估计(n)与 ejφ^(n)相乘可得恒模干扰信号估计(n),将去载波的受干扰信号与本模块输出的恒模干扰直接相减,可得干扰抑制后的去载波AM信号。

图5 恒模干扰实时估计模块硬件框图Fig.5 Hardware block diagram of module of constant modulus interference real-time estimation

4.3 DSP程序设计

DSP的载频估计原理在文献[2-3]中已进行了详细描述,这里给出DSP中程序的设计流程,如图6所示。系统复位后,首先向FPGA传输相应的控制字[7],然后进入载频估计部分。估频数据来自FPGA,估频点数为10 000点。当首次估频时,先进行频点间隔为10 Hz和1 Hz的两次粗估,然后进行间隔为0.1 Hz的精估,通过估出的载波频率值计算出陷波器的初始值及陷波参数,将其分别进行定点化处理后传给FPGA,系统重新打开中断准备进行下一次估频,随后估频过程在原有估计频率的基础上只进行精估即可。

图6 DSP程序流程图Fig.6 Flow chart of DSP program

5 实验结果及分析

5.1 单通道恒模算法定点化处理结果

将Matlab中仿真数据源的幅度放大到与FPGA中相应模块的输入数据范围相一致,分别对浮点和定点单通道恒模干扰抑制算法进行性能测试,其输出结果分别如图7(a)和图7(b)所示。从波形上可直观看出,算法经定点化处理后,输出的话音信号与定点化之前基本没有变化,两种算法的相关系数为0.992 4。使用实测数据源对定点化前后的算法进行测试,干扰抑制性能良好。仿真和实测数据源的测试结果为定点算法在硬件平台上的实现提供了保障。

5.2 抗干扰接收机性能测试结果

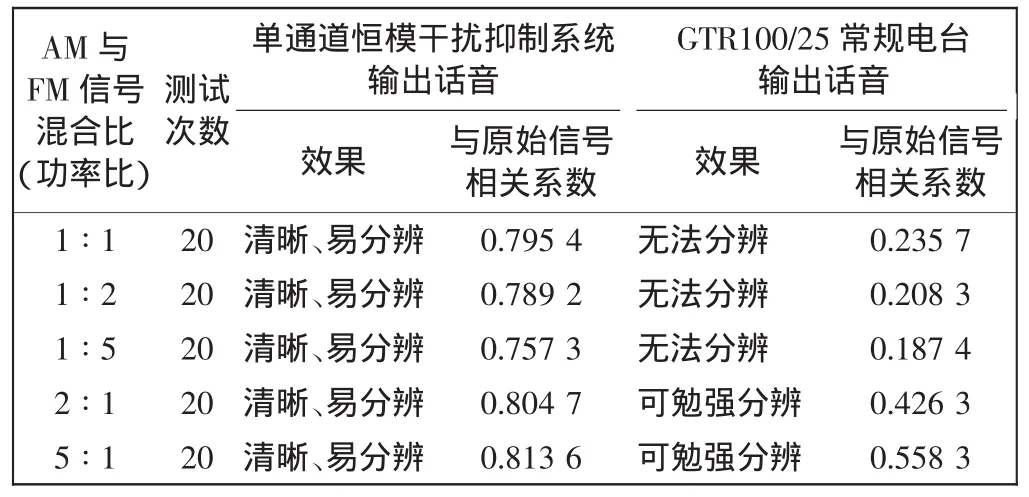

在FPGA中对接收机的恒模干扰抑制性能进行测试,测试条件:AM信号载频118 MHz,调制度为80%,FM信号载频118 MHz,频偏15 kHz,AM信号和FM干扰的功率均为0 dBm,将两种信号进行混合作为接收机的输入。利用ChipScope软件观察系统的话音输出,如图8所示。由测试结果可知,对混合信号直接解调时输出信号与原始话音信号相差较大,而经过恒模干扰抑制处理后接收机输出的话音信号与原始话音基本一致,实现了抗干扰的功能。使用OTE公司的GTR100/25常规电台作参考,改变AM信号与FM干扰的功率比,对比两接收机输出的话音信号,其结果如表1所示。对抗干扰接收机的性能测试并与常规接收机进行性能对比,这两种测试方式均证明了单通道恒模抗干扰接收机可输出清晰的话音信号,具有良好的干扰抑制效果。

图7 定点化处理前后输出结果对比Fig.7 Contrast of output results before and after fixed-point processing

图8 抗干扰接收机性能测试Fig.8 Performance testing of anti-interference receiver

表1 抗干扰接收机与常规接收机性能对比Tab.1 Performance contrast between anti-interference and conventional receivers

6 结语

本文在基于FPGA和DSP的平台上完成了单通恒模抗干扰民航VHF接收机的设计与实现。在设计过程中针对单通道恒模算法和Goertzel算法的特点,合理地分配了FPGA和DSP的功能及资源:在FPGA中搭建单通道恒模干扰抑制系统的主体部分,在DSP中完成对FPGA的控制和载频估计部分。系统测试表明:单通道恒模抗干扰接收机能够有效地抑制恒模干扰,明显提高话音通信质量。本实现方案亦可应用于甚高频数据链通信抗干扰,具有一定的扩展性。

[1]刘福奇,刘 波.Verilog HDL应用程序设计实例精讲[M].北京:电子工业出版社,2009.

[2]吴仁彪,钟伦珑,胡铁乔,等.民航地空通信中单通道最优恒模干扰抑制方法及其系统[P].中国专利:ZL200710059767.1,2008-05-07.

[3]石庆研,吴仁彪,钟伦珑.单通道最优恒模自适应干扰抑制方法[J].电子与信息学报,2011,33(5):1126-1130.

[4]ALAN V.Oppenheim.Discrete-time Signal Processing[M].2版.北京:清华大学出版社,2005.

[5]钟伦珑.地空通信自适应干扰抑制实验系统的研究与设计[D].天津:中国民用航空学院,2006.

[6]吴 鹏.单通道地空通信干扰抑制系统的设计与实现[D].天津:中国民航大学,2009.

[7]Texas Instruments Incorporated.TMS320C54x系列DSP的CPU与外设[M].北京:清华大学出版社,2006.