星载扩频应答机抗SEU方法及验证

(航天东方红卫星有限公司,北京 100094)

1 引言

近年来,扩频微波统一测控系统已广泛应用于我国航天测控领域,它利用伪随机码序列对传送的信息数据进行调制传输,依靠高速率扩频码保证测距精度,从而实现测距、遥控、遥测及时间同步一体化。扩频应答机是卫星测控的设备之一,其与地面测控站配合工作,完成卫星的测控和工程测量任务,它接收、解调来自地面测控站发送的遥控信息及来自地面站发送的测距帧信息,同时采集测距相关信息填入下行测距帧中,调制后发送至地面站;对遥测数据进行调制后发送给地面测控站。

由于现场可编程门阵列(FPGA)和数字信号处理(DSP)有计算速度快等优点,星载扩频应答机的基带部分采用了FPGA 加DSP的结构,完成扩频信号解调捕获等相关功能。

国内外相关领域对FPGA 的太空应用正处于发展阶段,对其中亟待解决的可靠性问题研究相对较多,尤其是抗单粒子翻转(SEU)研究是一项重要的课题。FPGA 和DSP 两种器件对单粒子翻转的敏感,其抗单粒子能力直接影响了扩频应答机的功能和性能,以及整星测控信道的可靠性。本文的研究目的是提高扩频应答机抗SEU 的能力,尽量减少SEU 对扩频应答机功能的影响,确保卫星测控链路的稳定和可靠。

本文首先对单机层面扩频应答机抗SEU 的方法进行了介绍,列举了几种目前小卫星使用的扩频应答机中FPGA 和DSP 抗SEU 的设计方法,又从系统层面提出了由星上特定设备根据规定的原则对应答机进行关机和开机操作以消除SEU 故障的方法,最后对目前我国小卫星扩频应答机在轨飞行结果进行了统计和总结,验证了本文所述方法的正确性和有效性。

2 SEU 效应机理及后果

SEU 是发生在具有单稳态或双稳态的逻辑器件和逻辑电路的一种带电粒子辐射效应。当单个空间高能带电粒子轰击到大规模的逻辑型微电子器件的芯片时,沿着粒子的入射轨迹,在芯片内部的P型半导体和N 型半导体交界面(PN 结)附近区域发生电离效应,生成一定数量的电子-空穴对。如果这时芯片处于加电状态,这些由于辐射产生的载流子将在芯片内部的电场作用下发生漂移和重新分布,从而改变了芯片内部正常载流子的运动和分布状态,当这种改变足够大时,将引起器件电性能状态的改变,造成逻辑器件或电路的逻辑错误,如存储器单元中存储的数据发生翻转,进而引起数据处理错误,电路逻辑功能混乱,程序故障,甚至死机。

常用于航天器研制的FPGA 产品主要分为两种:基于反熔丝的一次性编程FPGA 和基于随机静态存储器(Static Random Access Memory,SRAM)型的FPGA。目前,我国航天领域使用的超大规模逻辑型微电子电路XQR2V1000和XQR2V3000均为SRAM 型FPGA。SRAM 型FPGA 发展的工艺特点仍以互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,Bu1kCMOS)为主,其配置信息都存储在SRAM 中,它与一次编程的反熔丝FPGA相比,容易受到单粒子辐射效应的影响,发生单粒子翻转和锁定等故障,主要有以下2个原因[1-3]:

(1)基于SRAM 型FPGA 的配置数据存储在芯片内部的SRAM 中,而SRAM 对SEU 较为敏感;

(2)基于SRAM 型FPGA 的可编程逻辑开关主要采用多路选择器实现,内部逻辑功能主要采用查找表实现,而多路选择器与查找表对单粒子辐射效应都较为敏感。

当存储设计逻辑的SRAM 在轨发生单粒子翻转后,整个FPGA 功能可能失效。

3 扩频应答机基带部分的基本结构

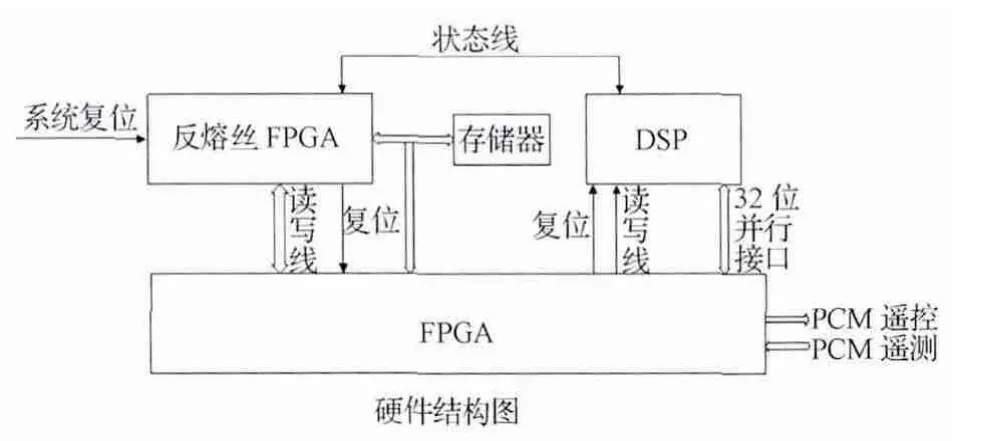

目前,小卫星使用的S频段非相干体制扩频应答机共有4个模块,分别为接收通道、发送通道、下位机和数字基带模块。扩频应答机基带采用FPGA 加DSP的结构,组成如图1所示。主要由A54SX32、XQR2V1000、SMJ320C6415组成,A54SX32是系统中央管理单元,统一管理XQR2V1000、SMJ320C6415。

图1 应答机数字基带的组成框图Fig.1 Composing frame of digital baseband

数字基带部分完成的主要功能包括:捕获、解调解扩上行扩频信号,精细估计上行扩频信号相位和多普勒频率,形成持续的发送报文,将相位、多普勒频率遥测信息和采样时刻等信息扩频调制发送到地面站。若其发生SEU 故障后,可能影响应答机的功能和性能,甚至威胁到卫星的安全,故在整星及单机设计时须考虑抗SEU 设计,减小其带来的影响,下文分别从单机和系统两个层面介绍抗SEU 的方法。

4 单机级抗SEU 的方法

根据应用的不同,单机级抗SEU 的设计可以从2个方面开展:

(1)改进用户设计,屏蔽软错误对应用的影响,避免产生软失效;

(2)采取自主诊断和修复措施,减少软失效恢复时间。

高可靠硬件系统结构是实现上述设计的重要前提,是实现冗余加固和其他补充措施的基础。设计的根本原则是按照对于空间单粒子效应的敏感程度进行功能分层,由单粒子效应不敏感的高可靠器件作为系统仲裁和智能控制单元,采用高可靠单元(HRU)加DSP 加FPGA 的金字塔型处理平台结构[4-6]。HRU 是指采用反熔丝型FPGA(A54SX32),其对FPGA和DSP的运行状态进行监控,通过完善的检测和故障处理手段,避免由于发生单粒子翻转而导致的功能异常。

4.1 基带处理FPGA(XQR2V1000)抗SEU 方法

基带处理FPGA 抗SEU 的主要措施如下。

1)配置存储区回读校验

监控FPGA 每30min对处理FPGA 的配置存储区进行回读校验,将回读数据与可编程只读存储器(PROM)中的备份文件进行逐位比较,当发现不一致时会刷新配置存储区。

2)“看门狗”设计

基带处理FPGA 根据时钟管理单元产生一个“喂狗”方波输入到反熔丝型FPGA 中,由其执行FPGA 时钟基准的监测,在“看门狗”“喂狗”周期内,若未收到“喂狗”信号则对基带处理FPGA 进行重新引导。

3)三模冗余设计[7-9]

基带处理FPGA 设计对内部重要数据的寄存器采取三取二多数表决设计(Triple Module Redundancy,TMR),重要数据是长期存在的,并且其翻转将造成应答机功能错误的数据,包括PN 码的生成多项式及初相数据、扩频码解扩积分长度参数、下位机接口数据传输同步字等。

4)低速时钟的双采样设计

针对外部接口的低速数据时钟,采用双采样的方式滤掉数据传输时钟上的抖动。

4.2 DSP抗SEU 的主要措施

扩频应答机基带DSP采取的抗SEU 设计措施如下。

1)重要全局变量的三模冗余设计

关键变量的选取准则为:长时间存在的变量(如主程序的大循环控制变量)和主程序重要的全局指针、重要的全局标志。这些变量关系到DSP运行程序的总体进程,而且存在的时间比较长,发生单粒子翻转的概率比一些临时局部变量大的多,影响也更加严重,它们的翻转可能导致信号处理结果的大范围错误。

2)“看门狗”设计

DSP工作正常时,根据自身运行的状态,在每个处理流程内定期生成方波信号。反熔丝型FPGA在“狗咬”时间内收到该脉冲,则认为DSP 工作正常,否则对DSP 程序重新进行引导。一旦DSP 程序由于某些原因出现故障,“喂狗”信号会变得较长或者停止。

3)动态刷新设计

DSP根据自身的工作状态,在空闲的时候会对外设设置进行动态刷新,用以清除外设配置存储器的单粒子翻转。DSP根据自身的工作状态,在空闲的时候会对内部存储区和关键数据区进行校验,如果发现这部分区域的内容发生翻转,它会通过通用I/O 脚的上跳动作,向反熔丝型FPGA 主动申请动态刷新。反熔丝型FPGA 在收到DSP 的动态刷新申请时,会对DSP的程序区和关键数据区进行重新写入操作,重新写入操作不会对DSP正在进行的逻辑功能产生干扰。

4)内部程序和关键数据区检错和修复

采用Berger编码检验算法[10],对被检区域进行编码运算处理,计算结果为一个32位数据,分别存放在3个不同的地方备份。进行单粒子翻转检测前对存放的数据再次比较,表决输出,检测到错误则通过输出一个错误信号指示,利用监控FPGA 对程序区和关键数据区进行刷新,以完成错误的修复。

5)程序区巡检

DSP巡检模块的作用是在DSP工作正常时,定期巡回检测程序区:将DSP的内部程序区进行累加校验,得出一个结果,和已知结果进行比较,如果不一致,立即申请重新加载程序。

定期巡检程序执行情况,如果异常,停止看门狗“喂狗”脉冲,请求复位DSP。反熔丝型FPGA 收到复位命令后,对DSP进行程序引导和初始化等工作。

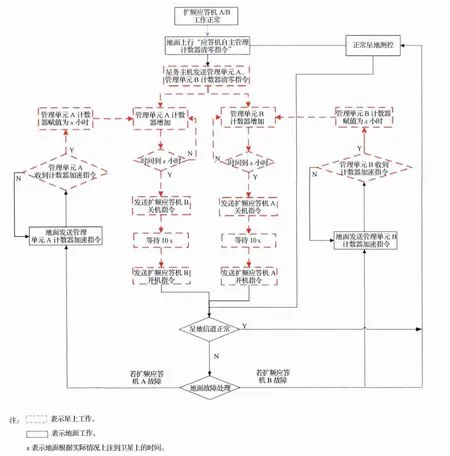

5 系统级扩频应答机抗SEU 的方法

由于DSP器件Cache区的动态特性,无法对其进行预计和检测,因此当DSP的Cache区出现单粒子翻转后,仍然有可能导致DSP 工作异常;且当异常未导致DSP 死机时,A54SX32 中的“看门狗”不能发挥作用,DSP就无法自主退出异常状态。故在系统层面进行了抗SEU 设计,由星上特定设备根据规定的原则对应答机进行关机和开机操作,以有效地解除单粒子故障,恢复星地测控信道,具体设计方法如下(见图2)。

图2 系统级扩频应答机处理SEU 故障操作流程图Fig.2 Flow chart of solving transponder’s SEU fault at system level

(1)根据风险分散的原则,分别由管理单元A和管理单元B 对扩频应答机进行在轨有条件的自主管理;为了防止两台应答机同时被关闭的可能,管理单元A 和管理单元B 的定时器设置可以相差一定时间。

(2)在进行卫星长期业务管理时,地面测控系统应在不长于24h内上行2条指令:“管理单元A 定时器清零指令”和“管理单元B 定时器清零指令”。星上接收到该上注指令时,说明地面上行信道畅通,管理单元A 或管理单元B 定时器归零后重新开始计数;

(3)如果星上一直没有接收到“管理单元A 定时器清零指令”和“管理单元B 定时器清零指令”,当管理单元A 或管理单元B计数器溢出时,说明地面上行链路出现问题,此时对扩频应答机整机关机,间隔10s后再开机;然后计数器再次从零开始计数;

(4)为在某些特殊情况下,加速星地信道问题处理,允许通过地面上注指令,缩短管理单元A 或管理单元B的计时时间长度。当管理单元A 或管理单元B 收到加速指令后,计数器计数一定时间后后对应答机进行关机和开机操作。

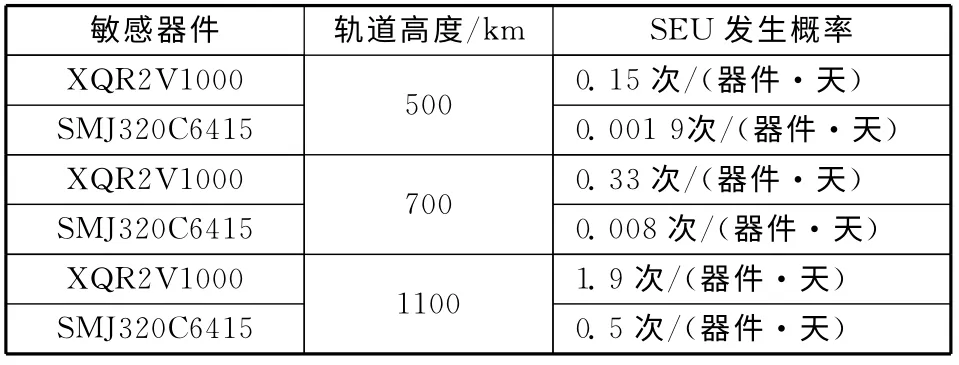

6 在轨试验与验证

本文对我国小卫星领域不同轨道高度小卫星的扩频应答机在轨FPGA 和DSP发生SEU 的情况进行了统计(见表1)。当扩频应答机发生SEU 后,通过第4节所述的方法自主恢复的概率超过99%,其余1%采用第5节所述系统级的方法进行恢复,保证了卫星遥控和遥测的正常发送与执行,验证了上述方法的有效性和正确性。

表1 扩频应答机发生SEU 情况统计表Table 1 Statistics of transponder occurring SEU

7 结束语

本文对非相干扩频应答机抗SEU 的设计方法进行了研究,从单机和系统层面介绍了由星上特定设备根据规定的原则对应答机进行关机和开机操作的抗SEU 方法。根据目前在轨飞行的情况来看,扩频应答机能够在轨稳定运行,保证了卫星测控链路的安全和可靠,采用上述方法能够对应答机FPGA和DSP等单粒子敏感器件受单粒子影响进行纠正和恢复。应答机采取的单机和系统级的抗SEU 的方法合理可行,可作为其它星载单粒子敏感器件抗SEU 设计的参考。

(References)

[1]Nozomu Nishinaga,Masayoshi Yoneda.Availability analysis of Xilinx FPGA on orbit[C].Military and Aerospace Programmable Logic Devices(MAPLD).Washington D.C.:NASA Office of Logic Design,2005

[2]丁义刚.空间辐射环境单粒子效应研究[J].航天器环境工程,2007,24(5):283-290 Ding Yigang.Single event effects in space radiation environment[J].Spacecraft Enviroment Engineering,2007,24(5):283-290(in Chinese)

[3]Sonza Reorda,Paccagnella A.Analyzing SEU effects in SRAM-based FPGAs[C].IOLTS2003:IEEE On-line Testing Symposium.New York:IEEE,2003

[4]刑克飞,杨俊,王跃科,等.星载软件无线电平台及其单粒子效应研究方法[J].空间科学学报,2006,26(7):477-481 Xing Kefei,Yang Jun,Wang Yueke,et al.Single event simulation and evaluation methodology for spaceborne software radio platform[J].Space Sci.,2006,26(6):477-481(in Chinese)

[5]Robert F,Hodson,Kevin Somervill,et al.An architecture for recongfigurable computing in space[C].Military and Aerospace Programmable Logic Devices(MAPLD).Washington D.C.:NASA Office of Logic Design,2005

[6]Chandru Mirchandani.Using software rules to enhance FPGA reliability[C].Military and Aerospace Programmable Logic Devices(MAPLD).Washington D.C.:NASA Office of Logic Design,2005

[7]黄影,张春元,刘东.SRAM 型FPGA 的抗SEU 方 法研究[J].中国空间科学技术,2007,4:57-64 Huang Ying,Zhang Chunyuan,Liu Dong.Research on SEU mitigation of FPGA BASE-on SRAM[J].Chinese Space Science and Technology,2007,27(4):57-64(in Chinese)

[8]Pratt B,Johnson E,Wirthlin M,et al.Improving FPGA design robustness with partial TMR[C]//Military and Aerospace Programmable Logic Devices (MAPLD.Washington D.C.:NASA Office of Logic Design,2005

[9]Fuller E,Caffrey M,Salazar A,et al.Radiation testing update,SEU mitigation,and availability analysis of the Virtex FPGA for space reconfigurable computing[C]//Military and Aerospace Programmable Logic Devices(MAPLD).Washington D.C.:NASA Office of Logic Design,2000

[10]Lo J C.An SFS Berger check prediction ALU and its application to self checking processor designs[J].IEEE Trans.on Computer Aided-Design,1992,11(4):525-540