提升LED驱动芯片视觉刷新率的逻辑电路设计

黎官华,王卫东

(桂林电子科技大学信息与通信学院,广西桂林541004)

提升LED驱动芯片视觉刷新率的逻辑电路设计

黎官华,王卫东*

(桂林电子科技大学信息与通信学院,广西桂林541004)

摘要:为了提升LED显示屏的画面质量,设计了能提高LED显示屏视觉刷新率的逻辑电路。该电路将一个显示周期分为32段,每一段包含有128个灰度时钟周期,占空比由12位灰度数据控制。逻辑电路产生的PWM和传统的PWM相比能提高视觉刷新率,最高能将视觉刷新率提高至32倍;能弥补S-PWM(Scrambled-PWM)在灰度数据低时视觉刷新率低的不足。在Cadence软件下进行设计仿真,并在开发板上进行了验证设计的可行性。

关键词:LED显示屏;逻辑电路; PWM;刷新率

LED显示屏具有节能、环保、色彩鲜艳等优势被广泛使用于公共媒体、户外广告、亮化工程等领域中[1]。灰度等级和视觉刷新率是衡量LED显示屏显示效果的两个重要的指标,刷新率越高,人眼越不能感觉到画面的闪烁;灰度等级越高,显示画面就更加细腻,同时色彩会更加丰富,但是高的灰度等级和刷新率是相互矛盾的指标[2]。在相同的灰阶时钟下,灰度等级越高,会产生刷新率过低的问题[3]。降低灰度等级或提高灰阶时钟频率可以提高视觉刷新率,但是降低灰度等级会严重影响画面的细腻和色彩,而提高灰阶时钟频率容易产生电磁干扰。

1 传统的PWM和S-PWM

传统的PWM用灰度数据和灰阶计数器的计数值相比较,计数器的计数值小于或是等于灰阶数据值时,LED点亮;计数器的计数值大于灰阶数据值后,LED关闭。对于任何级别亮度点亮脉冲的起始位置在同一个时间点上,如果所有LED同时被点亮会产生一个很大的电流尖峰,会产生严重的电磁干扰[4]。同时,在一个刷新周期内,LED点亮和关闭只有一次,只出现一个连续的时间可变点亮脉冲,刷新率会很低,可能给人眼带来闪烁感。S-PWM是将一个计数周期打散为若干个较短的计数周期,打散的计数周期之和等于打散前的计数周期,占空比也相等,这样就增加了整体的刷新率[5-6]。S-PWM将一个PWM周期分为最重要为(MSB)和最不重要位(LSB),MSB计数周期打散后重复更新多次,再加上一次LSB计数周期,使打散的计数周期之和等于打散前的计数周期,占空比也相等。但是这种调制也存在一个重要的问题,当MSB的数据全为0,LSB数据不为0时,S-PWM和传统的PWM产生的灰度控制信号几乎一样[7]。这种情况下刷新率并没有得到提升。

2 改进的PWM工作原理

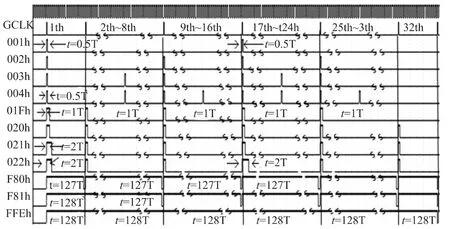

针对传统的PWM和S-PWM存在的不足,本文提出了一种改进型的PWM。改进型的PWM的工作原理是:以4 096个灰度时钟周期(GCLK)为一个LED显示周期,将一个显示周期分为32段,也就是将一个完整的PWM划分为32段pwm,每一段含有128个灰度时钟,每一段占空比由12位灰度数据控制,整个PWM的高电平时间随着灰阶数值的加1而增加一个GCLK,整个PWM高电平包含的GCLK个数等于灰阶数据的十进制值。计数器的计数值的高5位和灰阶数据的低5位(LSB)共同进行段选,计数器值的低7位和灰阶数据的高7位(MSB)相比较决定每一段的pwm高电平时间。灰阶数据小于010h时,选中的段数为输入灰阶数值对应的十进制值的两倍,每段pwm高电平时间为0.5个GCLK。选中段的顺序为:1、17>9、25>5、21>13、29>3、19>11、27>7、23>15、31>2、18>10、26>6、22>14、30>4、20>12、28>8、24。灰阶数据大于或等于010h时,选中的段数等于与输入灰阶数值对应的十进制值,选中的段pwm的高电平时间包含的GCLK个数等于MSB对应的十进制数值加1,未选中的段pwm的高电平时间包含的GCLK个数等于MSB对应的十进制数值。选中的段顺序为:1>17>9>25>5>21>13>29>3>19>11>27>7>23>15>31>2>18>10>26>6>22>14>30>4>20>12>28>8>24>16>32。例如灰阶数据为二进制000000100001时,MSB为0000001,那么段的pwm高电平时间为2个GCLK,LSB位为00001表示第1段被选中,选中的第1段pwm高电平时间为2个GCLK,剩余的31段为1个GCLK。随着灰阶数据加1,MSB不变,但是低LSB加1,则选中的段数加1,此时第1、17段pwm高电平时间为2个GCLK,剩余的30段为1个GCLK。灰阶数据为FFFh时,MSB为1111111,那么段的pwm高电平时间为128个GCLK,LSB位为11111表示中的1到31段被选中,选中的1到31的pwm高电平时间128 个GCLK,剩余的第32段为127个GCLK。部分波形如图1所示。

图1 PWM部分波形

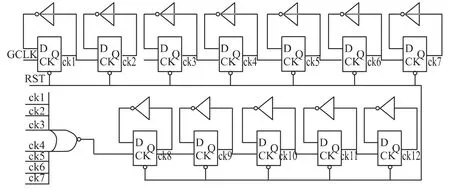

图2 计数器电路

3 逻辑电路实现图

3.1计数器

12bit的计数器如图2所示,计数器由12个D触发器构成。其中GCLK为计数时钟,RST为复位信号。当RST为低电平时,各个触发器的输出端Q 为1,ck1~ck12全为1。当RST为高电平时,低7位计数器开始进行减1计数。当ck1~ck7位全为0时,计数了128个GCLK,经过或非门,产生一个脉冲,高5位开始计数。在高5位中,ck8~ck12全为1时表示第一个128个GCLK计数5段,随着计数的不断进行,ck8~ck12为0时表示第32计数段。在一个刷新周期内,包含32×128个GCLK,实现了12bit的计数器。

3.2PWMH及PWML电路

PWMH及PWML电路包括有比较器、加法器,CP、CI模块电路及辅助选通逻辑判断电路。比较器由14个全加器构成。灰阶数据和计数器的计数值相比较,计数器的计数值小于或是等于灰阶数据值时,LED点亮;计数器的计数值大于灰阶数据值后,LED关闭。在上述原理分析中可知,MSB位全为灰0时,而且灰阶数据不小于010h时,选中段导通时间为1个GCLK,未选中的段为0个GCLK。因此在整个比较器进行两路数据比较,一路是原始的MSB,产生PWML;另一路是MSB加1后的灰阶数据,经过逻辑判断电路进行选择后产生PWMH。但是灰阶数据为0的时,LED在整个周期不亮的,如图1所示,所以用LSB位进行段选时只有31个状态。但是每当在MSB不为0,LSB全为0的时,所有的段都被选中,第32段才被选中,因此可以利用这个条件产生一个第32段才选中的控制信号。

在图1中,灰阶数据为020h,二进制位000000100001时,32段全部被选中,每段的高电平时间还是1个GCLK。若在图3的加法器模块还是加1,那么加1后的MSB位数据将变为0000010,再送入比较器中,那么此时的pwm的高电平时间为2个 GCLK,和实际相违背。同理,每当LSB位全为0,但是MSB位不全为0时都会出现中这种情况。为了解决这个问题,可以对灰阶数据进行一个预先判断,判断电路如图3的CP、CI模块。当遇到LSB位全为0,但是MSB位不全为0时,CI为0,那么加法器进行加0,再送入比较器进行比较。LSB不全为0时,CI为1,加法器进行加1。例如灰阶数据位为二进制000000100001,即图1中的021h时,由于LSB不为0,那么加法器加1,输出为0000010,PM1高电平时间为2个GCLK,PWML的高电平时间为1个GCLK,低5位为00001表示第一段选中,因此有第一段的高电平时间为2个GCLK,其余的31段没被选中,各段高电平时间为1个GCLK。加法器模块是由7个半加器构成,输入信号为G5~G11及CI,输出为g5~g11,F。由于在灰阶数据小于010h时,每段的高电平时间为0.5个灰阶周期。因此利用比较器的比较结果PM1和灰阶时钟GCLK相与,即可得到一个高电平时间为0.5 个GCLK的脉宽调制波PM2。灰阶数据G5~G11经过一个8输出或门产生一个判断信号C,灰阶数据小于010h时,C为1,否则为0。C可以作为PM1和PM2的选通信号,C为1,PM3等于PM2,否则PM3等于PM1。在MSB全为1时,对应的十进制数为127,加1后变为十进制数128,MSB各位为0,进位标志F 为1。F和PM3经过或门,或门的输出为PWMH,F 为0,PWMH为PM3,F位1,PWMH在整个长为128 个GCLK段中保持高电平。

图3 PWMH及PWML电路

3.3译码电路

灰度数据的LSB和计数器的高5位ck8~ck12共同进行段选。从上述段选的顺序可知,随着LSB的增加,选中的段数会加1,LSB所对应的十进制数值是多少,就会有多少段被选中,温度计译码也是输入的二进制信号所对应的十进制是多少就会有多少个“1”输出。因此对LSB译码时采用温度计译码。为了降低电路的复杂性,5位温度计译码由2位温度计译码和3位温度计译码共同构成。其中2位温度计译码的输出作为列信号,3位温度计译码的输出作为行信号,再结合电源和地,就构成了4行8列的阵列,32个输出;每个输出端的状态是由行、列的状态和行列选择逻辑电路决定[8]。N位温度计译码有2N-1个“1”输出,但是第32段是在LSB全为0,MSB不为0的时候才被选中。因此可以通过图3中的CP、CI产生模块中产生一个判断信号CP,译码器的第32个输出端CP相或,则5位温度计译码可以输出32个“1”。灰阶数据小于010h时,选中的段数为输入灰阶数值对应的十进制值的两倍,灰阶数据大于010h时选中的段数为输入灰阶数值对应的十进制值,二进制左移一位,相当于乘以2。因此可以设置一个位移电路,在图3中,C为1时,灰阶数值进行左移一位。段译码器电路的输入信号为计数器的计数值高5位,译码32个输出,每一个输出表示一个包含128个GCLK计数段。

图4 译码电路

3.4选择逻辑电路

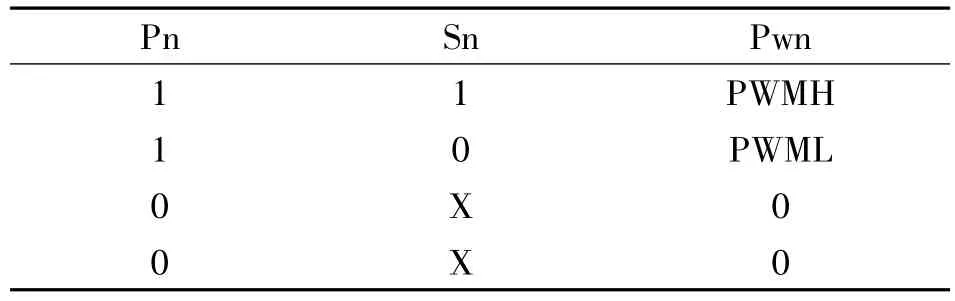

比较器产生了两个不同的结果,一个是PWML,另一个是PWMH。每一段pwm是PWML还是PWMH,由温度计译码决定,温度计译码输出为“1”,则段的输出为PWMH,否则为PWML。但是第几段pwm输出由段译码器决定,段译码器的P1端输出为“1”则表示第一段输出。温度计译码的结果和段译码的结果共同决定第图5中pw状态。他们逻辑关系如表1所示,pwn经过图5的PWM合成模块,得到一个完整的PWM。

图5 选择逻辑电路

表1 Pn、Sn与Pwn的逻辑关系表

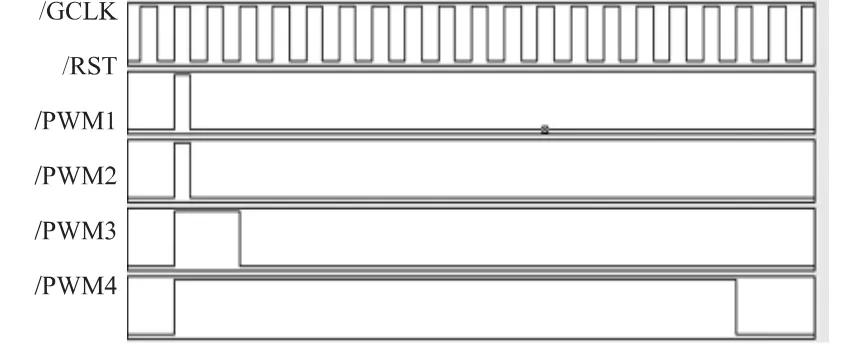

5 仿真验证结果及分析

采用Cadence ADE仿真平台中的Spectre Verilog数模混合仿真器对电路进行仿真。PWM1、PWM2、PWM3、PWM4分别为输入灰阶数据003h、007h、023h及103h时PWM输出波形。003h和007h都小于010h,选中的段数是其对应的二进制输出数值的两倍,因此PWM1、PWM2分别有6个和14个高电平脉冲,可见在灰阶数据低的时候,刷新率也有了提高。023h及103h都大于010h,MSB和LSB位不全为0,选中的段数是其对应的二进制输出数值。因此,选中的段数分3,即有3段输出的是两路比较器输出PWMH,剩下29段输出的是PWML,在一个完整的PWM内有32个高电平脉冲,刷新率是传统的PWM的32倍。

图6 PWM的仿真结果图

图7是第17段的pwm高电平包含的GCLK个数。003h、007h、023h及103h时,17th都被选中。003h和007h都小于010h,其pwm只包含0.5个GCLK,PWM1和PWM2的总的高电平时间分别为3个、7个GCLK。023h的MSB为0000001,那么比较器输出中PWMH包含2个GCLK,PWM包含1个GCLK,所以PWM1的高电平包含有(3×2+29×1)个GCLK,和023h对应的十进制值35相符合。

图7 第17显示段pwm仿真图

为了进一步验证电路的可靠性,在QuartsⅡ软件中建立上述原理图,并下载到FPGA中,用拨码开关模拟灰阶数据输入,通过示波器观看PWM的输出波形。当模拟的输入值为103h时,PWM的输出波形如图8所示,波形和图7中的PWM4相符合。

图8 灰阶数据为103 h时PWM图

6 总结

本文分析了传统的PWM和S-PWM的不足,设计了一种实现改进型的PWM的电路。电路包含了计数器、比较器、译码器等模块,将一个完整的PWM显示周期划分为32个显示段,不同的灰阶数据每个显示段包含的GCLK不同。划分前的PWM和划分后的PWM占空比相一致。改进型的PWM即使在灰阶数据很低时视觉刷新率也有了很大提高,提升了LED显示屏的画面质量。

参考文献:

[1]陈龙,鲁宝春,庄明照,等.全彩LED显示屏灰度改进研究[J].辽宁工业大学学报,2011,31(1) :9-12.

[2]宗庆国,袁胜春,何国经.LED显示屏高灰阶高刷新技术探讨[J].现代显示,2012,140:335-339.

[3]邓宏贵,梅卫平,曹文辉,等.基于PWM的LED显示屏像素亮度控制方法[J].光电子技术,2010,30(2) :131-134.

[4]宋超,王瑞光,冯英翘.LED显示屏驱动电流的潜在电磁干扰分析[J].光电子·激光,2013,24(6) :1059-1064.

[5]苏信华.可提高影像刷新率及电磁干扰的高灰度LED驱动芯片[J].现代显示,2007(10) :66-68.

[6]邱天奇.基于SPWM功能的LED恒流驱动芯片[D].西安:西安电子科技大学,2011:27-28.

[7]王巍,黄展,安友伟,等.全彩LED驱动芯片的S-PWM优化[J].电视技术,2012,36(21) :74-76.

[8]刘卫平.8位高速电流舵型DAC电路研究与设计[D].电子科技大学,2006:36-38.

[9]Svilainis L.LED Brightness Control for Video Display Application [J].Displays,2008,29(5) :506-511.

黎官华(1987-),男,汉族,广西玉林人,桂林电子科技大学集成电路工程硕士研究生,研究方向为数模混合集成电路设计,69571294@ qq.com;

王卫东(1956-),男,汉族,桂林电子科技大学硕士生导师,教授,中国通信学会高级会员,研究方向为模拟集成电路与电流模式电路。

Design of High Refresh Rate and High Precision LED Constant Current Drive Circuit

LI Guanhua,WANG Weidong*

(School of Information and Communication Engineering,Guilin University of Electronic Technology,Guilin Guangxi 541004,China)

Abstract:In order to improve the quality of image of LED display,a high refresh rate and high stability LED constant current drive circuit was designed.A complete PWM is divided into 32 sections.A novel counter is designed by modified the M-serial to produce irregular PWM,improves visual refresh rate.At the same time,improve the band gap reference source and using high output impedance current mirror to improve the stability of current.

Key words:high refresh; high stability; band gap reference source; current mirror

中图分类号:TN432

文献标识码:A

文章编号:1005-9490(2015) 03-0526-05

收稿日期:2014-06-30修改日期:2014-08-12

doi:EEACC:4240D; 121010.3969/j.issn.1005-9490.2015.03.012