基于边界扫描技术的装备电路可测性设计

许四毛,邓小鹏

(电子工程学院,合肥 230037)

基于边界扫描技术的装备电路可测性设计

许四毛,邓小鹏

(电子工程学院,合肥 230037)

随着装备中基于复杂数字电路的嵌入式系统应用越来越广泛,装备中电路系统的可测性设计(DFT)已成为装备可测试性设计的重要内容。IEEE 1149.1作为一种标准化的电路可测性设计方法,弥补了传统电路测试方法存在的缺陷,为复杂的互连电路提供了一种非入侵的测试手段。首先简述了可测试性设计和边界扫描测试技术的基本原理,并从边界扫描测试链设计、提高测试覆盖率和优化电路网络几个方面,分别提出了几种装备电子系统的电路可测试性设计的具体方法。

边界扫描技术,可测试性设计,JTAG接口,互连电路网络

0 引言

器件封装的小型化、表面贴装(SMT)技术,特别是BGA等球形封装技术的广泛应用,现代装备中的电子系统使用越来越多的高密度器件和多层印制板技术,使得其电路节点的物理可访问性逐步减低,借助于传统的针床在线测试(ICT)技术使用的局限性日益增大。为满足现代装备中电子系统测试和故障诊断需求,进行可测性设计(Design-for-Testability,DFT)[1]已成为装备电路系统设计不可或缺的重要组成部分。现代装备电子系统中大量JTAG兼容器件的应用,使得采用边界扫描测试技术进行装备电路系统的测试和故障诊断成为可能。IEEE 1149.1作为一种标准化的可测性设计方法,弥补了传统电路测试技术的缺陷,为复杂互连电路提供了有效的测试手段[2]。基于IEEE 1149.1标准(又被称为JTAG协议)制定的边界扫描技术是对电路DFT的一个飞跃发展。边界扫描技术的应用使得电路板上需要的测试节点数目减少,用于测试夹具的费用减少,比传统的ICT测试节省了时间,缩短了产品推向市场的周期。

1 装备电路系统可测试性技术

可测试性是系统和设备能及时、准确地确定其工作状态(可工作、不可工作、工作性能下降)并隔离其内部故障的一种设计特性。可测试性是设备本身的一种设计特性,描述了测试信息获取的难易程度的表征。一个产品的可测试性包括两个方面的含义:一方面,是能通过外部控制激活产品状态(通常为故障状态)的特性,即可控性;另一方面,能通过控制将激活的故障状态传送到可观测端口的特性,即可观测性。同可靠性(reliability)一样,可测试性也是装备本身所固有的一种设计特性[3-6]。通过装备电子系统的可测性设计研究,使武器系统全寿命周期费用大大降低。改善电子系统的可测试性设计是提高电子装备性能、简化维修保障工作和提高效费比的最有效途径。

20世纪80年代中期,美国军方相继实施了综合诊断研究计划,并于 1993年 2月颁发MIL-STD-2165A《系统和设备的可测性大纲》。大纲将可测试性作为与可靠性及维修性等同的设计要求,并规定了可测试性分析、设计验证的要求及实施方法。国内装备的可测性设计从20世纪80年代开始逐渐得到重视。1995年10月发布国军标GJB2547-95《装备测试性大纲》,但目前装备可测试性问题仍然没有得到很好地解决,甚至成为装备保障过程中最为突出的问题。

装备中电子系统的可测试性设计技术,大体可以分为如下3个发展阶段:特定目标可测试性设计;基于扫描设计的结构化设计;基于边界扫描机制的标准化设计[7]。1990年,IEEE组织和JTAG组织共同推出了IEEE 1149.1边界扫描标准,该标准已成为数字电路系统进行可测性设计的主流技术。采用边界扫描测试技术进行DFT设计是数字电路系统DFT设计技术的一个飞跃发展,已成为电路系统的主要测试性设计技术之一。

2 边界扫描测试技术的原理

边界扫描技术是一种应用于数字集成电路器件的测试性结构设计方法。所谓“边界”是指测试电路被设置在集成电路器件功能逻辑电路的四周,位于靠近器件输入、输出引脚的边界处。所谓“扫描”是指连接器件各输入、输出引脚的测试电路实际上是一个串行移位寄存器,这种串行移位寄存器被叫作“扫描路径”,沿着这条路径可输入由“1”和“0”组成的各种编码,对电路进行“扫描”式检测,从输出结果判断其是否正确[8]。边界扫描测试技术标准IEEE1149.1要求在集成电路中加入边界扫描电路。在板级测试时,可以在模式选择的控制下,构成一条就集成电路边界绕行的移位寄存器链,对板内集成电路的所有引脚进行扫描,通过将测试数据串行输入到该寄存器链的方法,检查发现印刷电路板上的器件焊接故障和板内连接故障,极大地方便了系统电路的调试。

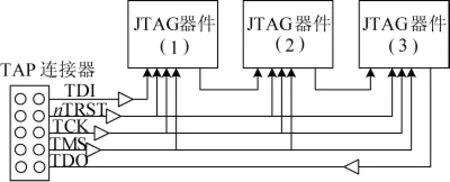

边界扫描测试机制是通过边界扫描测试总线和设计在器件内部的边界扫描结构实现的,如图1所示。边界扫描总线接口由4根(5根)测试总线构成。主要完成测试向量输入、测试响应向量输出和测试控制功能。在器件内部边界扫描逻辑主要由TAP测试存取口(又称JTAG接口)、TAP控制器和若干寄存器组成[9]。

IEEE1149.1标准中定义的JTAG接口为4线或5线端口:

TCK:测试时钟输入;

TMS:测试模式选择;

TDI:测试数据输入;

TDO:测试数据输出;

TRST:测试复位(可选)。

由图1所示的边界扫描测试结构可知,电路中各边界扫描器件(又称JTAG器件)互相串连,在电路中构成边界扫描测试链。在执行边界扫描测试时,由边界扫描测试控制器(JTAG控制器)产生边界扫描测试控制逻辑,JTAG器件中的TAP控制器接收边界扫描测试控制逻辑,执行相应的边界扫描测试任务,并通过由TDI——TDO构成的扫描数据链接收测试驱动数据和回传测试响应数据。

图1 边界扫描测试电路结构

为了降低测试时间,提高测试效率,在测试过程中需要通过测试计划来规划测试选项内容。测试计划通过裁剪测试链路长度、选择被测器件及其测试次数等来提高测试效率或实现个性化测试。当链路长度或测试器件数量及次数发生变化时,其要求的测试数据序列相应也发生变化。

3 基于边界扫描的电路可测试性设计

由边界扫描测试技术的基本原理可知,采用边界扫描测试技术实现电路互联测试的关键技术主要有:

(1)电路中边界扫描测试电路(JTAG测试链)结构完整、合理性;

(2)电路中的边界扫描测试对器件的覆盖率;

(3)边界扫描测试链对电路网络的覆盖率;

要改善装备中电路系统的DFT设计,就必须尽可能的提高电路中上述关键技术的指标。

3.1 完整、合理的边界扫描测试链设计

完整的边界扫描测试电路,需具备如下要素:

(1)提供符合IEEE1149.1标准的JTAG访问控制接口;

(2)电路中包含遵循IEEE1149.1标准的BS器件;电路中的各BS器件通过边界扫描测试总线形成JTAG测试链,BS器件在电路中构成的测试链结构可以是图2~图4的3种结构之一[10];

图2 串联JTAG测试链模式

图3 串并混合测试链模式

图4 并行测试链模式

(3)合理的JTAG链布局。确认所有的需要的TAP控制器正确布线,TAP信号线被优化布局,不受其他信号线的干扰,与电源、地线网络隔离,并确认系统的加电模式与IEEE1149.1的加电模式一致;

(4)尽可能小的边界扫描测试总线信号线之间的相位差(特别是TCK和TMS)时TAP工作正常的关键点,这取决于JTAG接口信号线之间的布线长度差、缓冲器之间的延时差;

(5)边界扫描测试总线的匹配设计。在JTAG链的终端,TCK信号线必须使用一个68 Ω的电阻和100 pF的电容与地线之间构成终端匹配电路[11]。TDI和TMS需采用10 K电阻与电源之间形成上拉电路。TDO也需要通过10 K电阻与电源网络形成上拉电路,与TJAG链中的最后一个设备采用22 Ω电阻进行串接。nTRST信号建议增加一个下拉电路,以避免浮动的输入干扰(下拉阻值的选择取决于电路的驱动能力以及JTAG’链中的JTAG兼容设备需要的驱动能力)。如图5所示;

图5 JTAG接口信号匹配设计

(6)多板集成测试链设计。当电路中使用子板时,JTAG测试链通路通过板间连接器连接子板,当子板可选时,需设计子板检测逻辑来旁路子板的JTAG测试链路,如图6所示;

图6 可选子板旁路逻辑设计

(7)合理的JTAG接口总线缓冲驱动设计。对TAP主要信号进行缓冲驱动,可以减小信号噪声、避免电阻不匹配并增加信号的扇出能力。在电路板的JTAG信号(TMS、TCK、TDI、nTRST)入口和信号(TDO)出口增加驱动电路,并且建议每隔4个~6个JTAG设备增加一个信号驱动电路,以提高信号的完整性。但切记增加信号驱动不能带来信号相位差的增大。如图7所示。

图7 JTAG接口总线缓冲驱动设计

3.2 增加对边界扫描测试链电路器件的覆盖率设计

(1)尽可能使用遵循IEEE1149.1的JTAG兼容器件,且这些JTAG器件可以方便地获取符合IEEE1149.1规范的BSDL文件,以提高边界扫描测试覆盖率;

(2)对于电路中的非JTAG器件,将非JTAG器件按功能进行逻辑簇设计,并采用JTAG兼容器件对一逻辑簇进行环绕处理,以实现对逻辑簇的输入控制和输出监视,达到对簇内有效节点的充分访问,实现对逻辑簇尽可能全面的测试,逻辑簇测试电路的设计如图5所示。如果必要,可增加JTAG兼容器件来增加对簇内电路节点的访问;

图8 逻辑簇测试电路可测试性设计

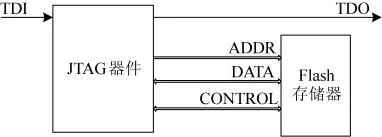

(3)现代装备的数字电路系统中,存在大量的可编程非JTAG器件,如各类存储器、AD/DA转换器件、可编程接口器件等。在进行电路可测试性设计时,需考虑通过JTAG器件实现对这些可编程非JTAG器件的所有必要引脚(数字IO引脚)的访问,最好是通过单个JTAG器件实现,如图9所示。

图9 可编程非JTAG器件的可测试性设计

3.3 针对电路网络的可测试性设计

(1)设计和利用JTAG器件的IO引脚,增加电路的测试覆盖率。合理设计与JTAG器件IO引脚连接的非JTAG器件电路,使之构成逻辑簇测试电路,利用JTAG器件的IO引脚对非JTAG器件构成的电路进行逻辑簇测试。利用空闲的JTAG器件IO引脚对设计测试点,对电路中测试链不可达的独立逻辑电路进行测试访问;

(2)特殊逻辑信号的控制逻辑设计。当存在重要的电路板或者器件的控制信号(如RESET、电源开关、看门狗、关机等信号),需设计合理的电路逻辑,可通过JTAG测试逻辑实现对这些控制信号的设置;

(3)对于多元控制的信号,应设计JTAG测试逻辑,实现对多元信号驱动器输出的独立使能控制。对于电路中的双向数据总线,应设计JTAG测试逻辑对数据总线的方向控制;

(4)对电路中需时钟同步操作的非JTAG器件,需设计JTAG测试逻辑电路实现对时钟的同步控制,例如对于电路系统中的SDRAM,若SDRAM加载一个自由运行时钟,则无法实现对次SDRAM的边界扫描测试,当SDRAM的时钟可以由JTAG测试逻辑进行同步控制时,JTAG测试向量可建立与SDRAM的时钟同步,便可实现对SDRAM的测试。如果一个JTAG器件(如CPLD或FPGA)可以在时钟源和SDRAM间建立路由(ROUTE)或者提供时钟缓冲(Clock Buffer),则可以大大提高覆盖率,如图10所示;

图10 JTAG测试逻辑对时钟同步控制设计

(5)对于不同工作电压的器件,在进行电路DFT设计时,须考虑增加相应的电平转换电路,以保证在整个边界扫描测试链中的电平一致性。在设计扫描测试链时,将逻辑电平相同的JTAG芯片组成一段扫描链,不同逻辑电平组扫描链间增加电平装换电路。在与JTAG控制器接口时,须保证TDI、TDO接口信号与JTAG控制器接口定义的逻辑电平一致。

4 结束语

基于IEEE 1149.1标准的边界扫描测试技术在装备故障检测领域有着越来越广泛的应用。本文提供的基于IEEE 1149.1标准的相关电路系统DFT设计方法,可以作为在装备中的嵌入式系统电路研制中的DFT设计参考。当然,提高装备电路系统的测试覆盖率,不仅仅和电路自身的DFT设计有关,还与边界扫描测试向量的生成算法、扫描链的冲突避免措施等密切相关。

[1]陈光禹,潘中良.可测试性设计技术[M].北京:电子工业出版社,1997.

[2]程云波,方葛丰.基于边界扫描技术的电路板可测性设计分析[J].电子测量技术,2007,30(7):24-27.

[3]王厚军.可测性设计技术的回顾与发展综述[J].中国科技论文在线,2008,3(1):52-58.

[4]MIL-STD-2165A.Testability Program for Systems and E-quipment[S].Depatrtment of Defense,Wasgington,1993.

[5]鲁昌华,蒋薇薇,章其波.浅谈数字电路的可测性设计[J].计算机时代,2003(3):8-9.

[6]熊晓英,王九龙,赵岩松.载人航天产品可测试性设计方法初步研究[J].载人航天2011(3):42-47.

[7]申宇皓,马春雷.系统级可测试性设计[J].华北工学院学报,2004,25(5):348-352.

[8]赵红军,杨日杰,崔坤林,等.边界扫描测试技术的原理及其应用[J].现代电子技术,2005(11):20-24.

[9]徐建洁.边界扫描测试系统的设计与实现[D].长沙:国防科技大学,2005.

[10]IEEEStd1149.1-2001.TestAccessPortandBoundary-scan Architecture[S].DepatrtmentofDefense,Wasgington,2001.

[11]DFT Guidelines.Design for Testability Guidelines Version3. 2[EB/OL].www.xjtag.com.Xjtag,2010.

Research of DFT of Equipment Circuiton Boundary-scan Technology

XU Si-mao,DENG Xiao-peng

(Electronic Engineering Institute,Hefei 230037,China)

With the equipment of complex digital circuit based on embedded system application is more and more widely.The Design For Testability(DFT)of equipment circuit system has become the important content of equipment’s DFT.As a kind of circuit design for testability standardization method,IEEE1149.1 makes up for the defects of the traditional circuit testing method.It provides a means for non-invasion circuit testing method for complex interconnection circuit.This paper first introduces the basic principle of circuit design for testability and boundary scan technology.And,from the aspect of design of boundary scan chain,improving the testing coverage and optimization of interconnection circuit network,some specific measures of the design for testability of equipment circuit system is girve out.

boundary-scan technology,DFT,JTAG Interface,interconnection circuit network

TP39

A

1002-0640(2015)03-0159-04

2014-01-19

2014-03-21

许四毛(1974- ),男,安徽枞阳人,硕士研究生。研究方向:嵌入式系统。