基于CPLD的DSP与CAN控制器的接口设计与实现

冯源

摘 要: 目前DSP处理器和CAN总线都在控制领域得到了广泛应用,在此以TMS320F2812 DSP处理器和独立的CAN控制器SJA1000为例,在分析DSP和SJA1000接口时序的基础上,采用CPLD有效地实现了两者之间数据和地址总线复用与非复用之间的转换和时序匹配。同时希望对于其他微处理器与CAN控制器的接口电路设计可以提供一定的参考。

关键词: DSP; CAN; CPLD; VHDL; 哈佛结构

中图分类号: TN710?34; TP302.2 文献标识码: A 文章编号: 1004?373X(2015)08?0066?04

Design and realization of interface between DSP and CAN bus controller based on CPLD

FENG Yuan1, DOU Hai?li2, YAN Hai?ming1

(1. China Aeronautics Computing Technique Research Institute, Xian 710119, China;

2. College of Science, Air Force Engineering University, Xian 710051 China)

Abstract: At present, digital signal processors (DSP) and CAN bus are applied widely to the control field. Taking the DSP TMS320F2812 and CAN controller SJA1000 as examples, the complex programmable logic device (CPLD) is used to realize the timing sequence matching effectively between data of DSP and SJA1000, and conversion of address multiplex bus and non?multiplex bus based on the analysis of the interface timing sequence of DSP and SJA1000. It is hoped that it can provide a reference for the design of interface circuit between other microprocessors and SJA1000 CAN controller.

Keywords: DSP; CAN; CPLD; VHDL; Harvard architecture

DSP(数字信号处理器)是一种具有特殊结构的微处理器。其芯片内部采用程序和数据分开的哈佛结构,具有专门的硬件乘法器,广泛采用流水线操作,提供特殊的DSP指令,可以快速地实现各种数字信号处理算法。TMS320F2812是TI公司为满足控制应用而设计的32位定点DSP处理器,它把一个高性能DSP内核和多种适合于控制的外设集成为一个芯片,运算速度可达150 MIPS,各项性能指标远远超过传统的16位处理器。

控制器局域网(Controller Area Network,CAN)是一种有效支持分布式控制或实时控制的串行通信网络。由于 CAN总线具有通信速率高、 开放性好、 报文短、 纠错能力强以及控制简单、 扩展能力强、 系统成本低等特点,再加上有众多的产品支持,已经在工业控制、汽车电子控制系统、船舶运输和航空航天等方面均得到了成功的应用,成为公认的最具有前途的现场总线之一。

CAN控制器实现了CAN协议的物理层和数据链路层的几乎所有功能,对外具有与主控制器和总线驱动器的接口。目前的CAN控制器有两种常见形式:一种是与某些微处理器集成在一起的内嵌的CAN控制器;另一种是独立的CAN控制器。采用集成了CAN控制器的微处理器实现CAN节点,电路和逻辑设计简单,减少成本;然而软、硬件设计过多地依赖于处理器的结构和资源,可移植性和灵活性比较差,协议无法有效地扩展和改进,从而使得模块的升级和维护成为一个重要问题。使用独立的CAN控制器的潜在优势是,系统开发人员可以根据需要,灵活地选择处理器来进行系统设计,而且软硬件设计具有较强的通用性,升级和维护比较简单。

目前应用最多的独立的CAN控制器是Philips公司的SJA1000芯片,它采用数据线和地址线复用的接口模式。而国内使用的 DSP 芯片以 TI 公司的 TMS320 系列为主流,它们对外的数据和地址总线结构形式是非多路复用方式。因此它们之间不能直接相连,需要数据和地址总线复用与非复用之间的转换和接口时序的匹配设计。本文以TMS320F2812 DSP处理器为例,在分析DSP和SJA1000接口时序的基础上,采用CPLD有效地实现了两者之间数据和地址总线复用与非复用之间的转换和时序匹配。

1 SJA1000与F2812 DSP接口信号与时序分析

1.1 SJA1000接口的主要信号说明

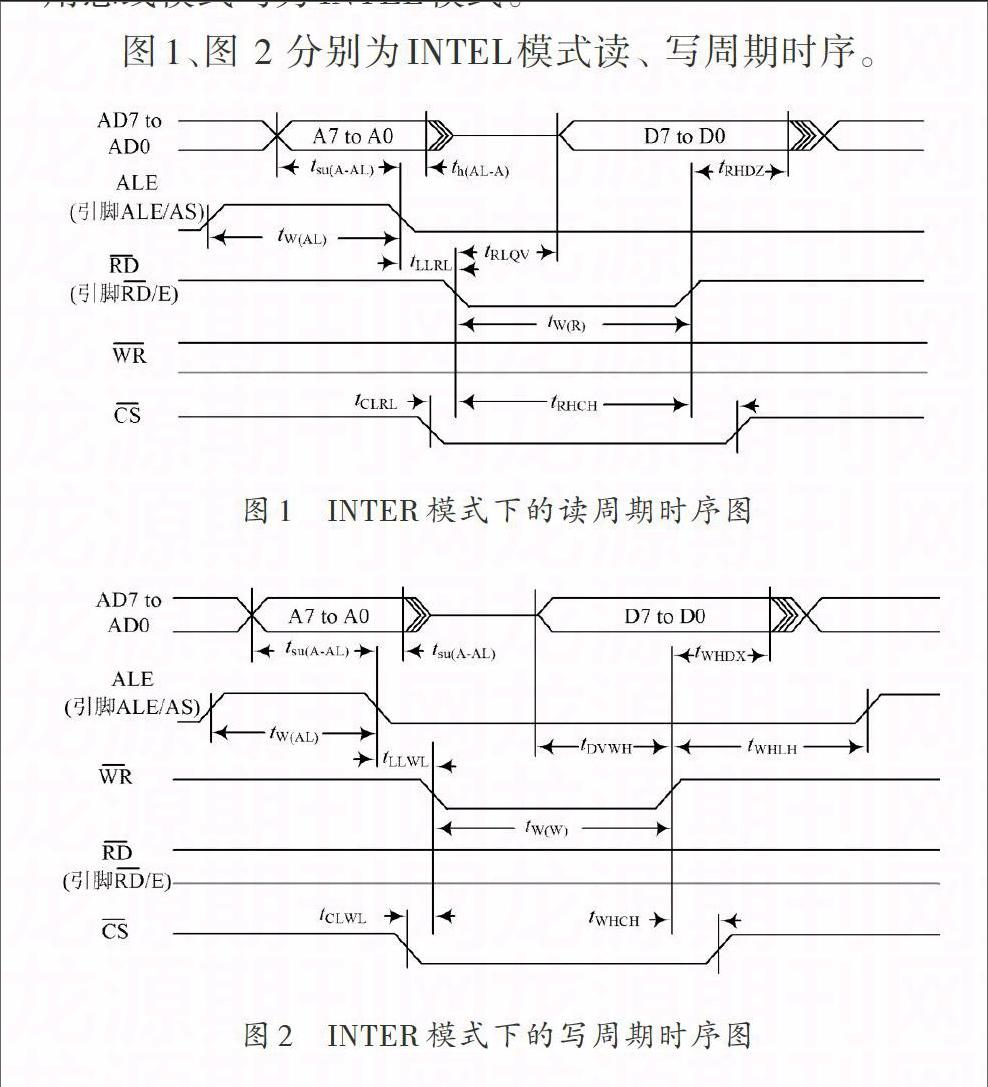

CAN 控制器 SJA1000 提供的微处理器接口方式为典型 INTEL 或 MOTOROLA 地址数据多路复用总线模式,主要信号有地址数据信号 AD7~AD0 ,地址选通信号ALE,片选信号CS,读信号RD,写信号WR,模式选择信号MODE。当MODE=时,为INTEL模式;当 MODE=0时,为MOTOROLA模式。后面描述的地址数据多路复用总线模式均为INTEL模式。

图1、图 2 分别为INTEL模式读、 写周期时序。

1.2 SJA1000接口时序分析

图1中SJA1000 的读时序,说明在设计转换桥时,多路复用总线的各信号必须满足的时间参数要求。ALE的脉冲宽度tw(AL)最小为8 ns ;地址信号(A7~A0)建立到ALE变为低电平所需时间tsu(A?AL)最小为8 ns;RD的有效脉宽tw(R)最小为40 ns;RD为低电平到数据信号(D7~D0)有效所需时间tRLQV最大为50 ns;RD变为高电平到地址数据线释放(即高阻状态)所需时间(tRHDZ)最大为30 ns。

图2中SJA1000 的写时序,与读时序相比,时间参数tw(AL)、tsu(A?AL)的要求是相同的,WR的有效脉宽tw(W)最小为20 ns;数据信号(D7~D0)有效时刻到WR撤销为高电平所需时间tDVWH最小为8 ns;WR变为高电平到地址数据线释放(即高阻状态)所需时间(tWHDX)最小为8 ns。

芯片的地址/数据复用引脚AD7~AD0,实际操作时,地址和数据分时传输,地址在前,数据在后。在地址选通信号ALE 有效时,传送的是地址信号;在RD或WR有效时,传输的是数据信号。片选信号CS与读信号RD或写信号WR同步,允许对SJA1000进行读/写操作。

1.3 TMS320F2812的XINTF接口的工作原理

TMS320F2812 DSP提供了一个可配置的存储器扩展接口(XINTF)来支持存储器空间的扩展,它是DSP与外部设备进行通信的重要接口。这个接口通常用于扩展SRAM、FLASH、ADC、DAC以及其他可以作为外部存储器的方式来访问的外设。对于DSP来说,SJA1000是一个以存储器编址的I/O器件,对它的内部寄存器的操作就像对RAM操作一样,并且其内部的地址空间0~127。在本文的设计中,将CAN控制器扩展到DSP的外部存储器空间Zone0(0x2000~0x4000)。TMS320F2812 DSP的XINTF接口被映射到5个固定的存储空间区域,可以通过软件操作配置寄存器对其中的每个区域的读/写操作的时序进行独立的设置,来实现对这些存储器或外设的正确接口。

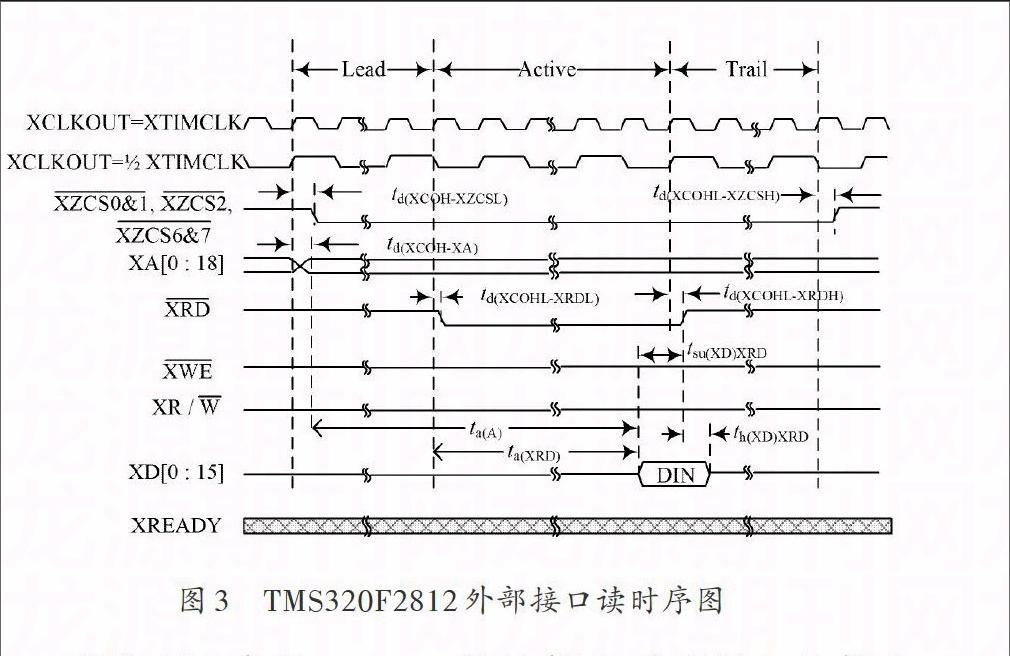

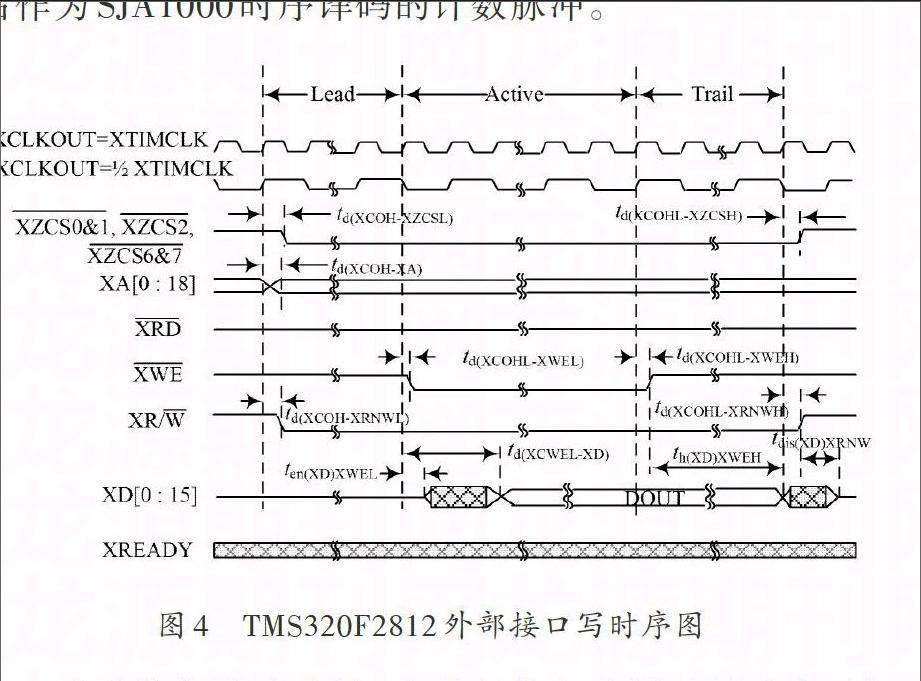

对XINTF中所有区域的访问都是以XINTF的定时时钟XTIMCLK为基础的,对外访问的时序都是从外部时钟输出XCLKOUT的上升沿开始的。XTIMCLK的大小可以通过软件设置为系统时钟SYSCLKOUT或是系统时钟的一半。XINTF对外访问时序分为三个阶段,即引导(Lead)、激活(Active)和跟踪(Trail)。另外可以通过采样由外设所提供的XREADY信号来在激活阶段添加1个或多个XTIMCLK周期的额外延时。

在本文的设计中,设置XTIMCLK=XCLKOUT=[12]SYSCLKOUT=50 MHz,即1拍的访问周期是20 ns,另外屏蔽XREADY信号的采样。

1.4 TMS320F2812的XINTF接口时序分析

下面重点对TMS320F2812的XINTF接口时序进行分析,图3和图4分别是屏蔽XREADY信号的采样时,TMS320F2812外部接口读时序图和写时序图。

首先需要参考SJA1000的时序图,确定以上时序图中引导(Lead)和激活(Active)、跟踪(Trail)三个阶段的时间参数。由图3和图4可知,对Zone0区域的实际操作是从该区域的片选信号XZCS0AND1有效作为起始基准时刻,另外对Zone0区域的访问时序都是从外部时钟输出XCLKOUT的上升沿开始的。为了使得译码逻辑简单,采样时序的可靠稳定,选定XCLKOUT的上升沿作为SJA1000时序译码的计数脉冲。

引导阶段片选有效,地址总线上有效地址稳定;激活阶段读/写信号稳定,数据稳定出现在数据总线上;跟踪阶段片选依然有效,但是读/写信号无效,从而结束读时序或完成写时序中总线上的数据到外部存储器的锁存。由图1和图2可知,引导阶段至少设置3个XCLKOUT,激活阶段至少设置4个XCLKOUT,跟踪阶段至少设置2个XCLKOUT。为了使得有效信号的译码时序尽量的宽松,在这里选定引导阶段4个XCLKOUT,激活阶段6个XCLKOUT,跟踪阶段4个XCLKOUT。

2 硬件接口的设计与实现

本文采用 Lattice公司在系统可编程器件 ISPLSI1032E,用硬件描述语言VHDL来描述逻辑,实现了系统编程调试,将硬件系统“软件化”, 其优点主要在于它有很强的灵活性,即其内部的具体逻辑功能可以根据需要配置,对电路的修改简单易行,可以很方便地实现复杂的逻辑电路,同时使得布线更简单合理,系统工作可靠性更高。TMS320F2812 DSP处理器与 CAN控制器 SJA1000的硬件接口原理图如图 5所示。因为该DSP的I/O信号的电压是3.3 V,而ISPLSI1032E和SJA1000的信号是5 V,所以DSP的数据总线ED、地址总线EA、读/写等控制信号,都事先需要经过IDT74FCT164245进行电平转换和双向缓冲,以保证信号传输的可靠性。由于篇幅有限,在图中省略了这部分电路的描述。在该电路设计中,采用1片三态缓冲驱动芯片IDT74FCT162245,通过由ISPLSI1032E生成:IDT74FCT162245的控制信号DOE#、AOE#、DDIR、ADIR;SJA1000的读/写控制信号SJA_ALE、SJA_CS#、SJA_RD#、SJA_WR#、SJA_RST#等。

3 接口逻辑设计

将SJA1000的地址范围确定为Zone0区域中的0x2000~0x20FF,根据以上的分析,由Zone0区域的片选信号XZCS0AND1和DSP的高地址EA15~EA8译码得到信号CAN_CS#,并且以该信号开始有效的时刻作为读、写时序转换的起始基准时刻。另外,整个译码以DSP的外部时钟输出XCLKOUT为节拍,并对其上升沿进行脉冲计数。图5中的接口控制信号的译码逻辑时序图如图6所示。

3.1 地址信号的转换过程

由图1和图2可知,SJA1000的读操作和写操作过程中的地址信号A7~A0和地址锁存信号ALE的时序是完全一致的。以已经确定的CAN_CS#的信号的开始有效的时刻为起始基准时刻,确定SJA1000的地址使能控制信号AOE#在CAN_CS#有效后第1个上升沿处开始有效,在Lead阶段结束时刻撤销。SJA1000的地址锁存信号SJA_ALE可以和AOE#信号同时开始有效,但是必须比AOE#信号提前1拍结束,以保证在SJA_ALE的下降沿采样到稳定的地址信号进行地址锁存。

3.2 读操作的转换过程

在TMS320F2812 DSP对CAN控制器SJA1000进行读操作时,数据流是由SJA1000流向DSP。SJA1000是数据流源端,DSP是数据流的目的端,并且目的端(DSP)的读时序是确定的。进一步分析图3可知,DSP的读信号XRD#和XD[0:15]上有效数据DIN的时序是已知的。首先根据SJA_ALE信号的结束时刻和DSP的读信号XRD#开始有效的时刻,确定SJA1000的读信号SJA_RD#是从XRD#有效后1个XCLKOUT时间后开始有效。

为了保证DSP从SJA1000所获得的数据是稳定可靠的,由图1的分析可以确定对SJA1000进行读操作时的数据使能信号RD_DOE#必须在SJA_RD#有效后大于50 ns以后才开始有效。这里,让RD_DOE#信号在SJA_RD#保持有效状态(低电平)3拍(60 ns)后开始有效。在DSP读操作的过程中,SJA1000给DSP提供的数据必须要“包住”DSP读时序中的有效数据DIN,所以RD_DOE#的有效状态在Trail阶段的第2拍结束后撤销。然后,只需让SJA1000的读信号SJA_RD#与RD_DOE#信号同时撤销即可。

3.3 写操作的转换过程

在TMS320F2812 DSP对CAN控制器SJA1000进行写操作时,数据流是由DSP流向SJA1000。DSP是数据流源端,SJA1000是数据流的目的端,并且源端(DSP)的写时序是确定的。进一步分析图4可知,DSP的写信号XWE#和XD[0:15]上的有效数据DOUT的时序是已知的。首先根据XD[0:15]上的有效数据DOUT开始有效的时刻,确定对SJA1000进行写操作时的数据使能信号WR_DOE#从Active阶段的第3拍开始时有效;然后根据DSP的写信号XWE#的撤销时刻,确定WR_DOE#信号在Active阶段结束后立刻撤销。

根据图2中SJA_ALE信号的结束时刻和刚刚确定的WR_DOE#的时序,确定SJA1000的写信号SJA_WR#可以和WR_DOE#信号同时开始有效,而SJA_WR#信号必须比WR_DOE#信号提早1拍撤销。

在确定了SJA1000的读信号SJA_RD#和写信号SJA_WR#后,由图1和图2可知,SJA1000的片选信号SJA_CS#在已经确定的中间信号CAN_CS#的基础上,SJA_CS#信号必须“包住”SJA_RD#和SJA_WR#即可。

4 结 语

本文详细分析了TMS320F2812 DSP处理器和 CAN控制器 SJA1000的接口信号和访问时序,提供一种基于复杂可编程逻辑器件 CPLD来解决两者之间的接口逻辑的匹配问题的方法,设计了DSP处理器和 CAN控制器之间的接口电路,给出了逻辑译码时序图,并详细分析了时序转换的整个过程。实践表明,该设计稳定可靠,同时对于其他系列 DSP处理器与SJA1000之间的接口逻辑的转换也具有很强的借鉴意义。

参考文献

[1] 饶运涛,邹继军.现场总线CAN原理与应用技术[M].2版.北京:北京航空航天大学出版社,2007.

[2] 宁改娣,曾翔君.DSP控制器原理及应用[M].北京:科学出版社,2009.

[3] PHILIPS Semiconductors. SJA1000 stand?alone CAN controller [M]. [S.l.]: PHILIPS Semiconductors, 1999.

[4] Texas Instruments. TMS320F2812 digital signal processors data manual [M]. USA: Texas Instruments, 2007.

[5] Texas Instruments. TMS320F28xx and TMS320F28xxx DSCs hardware designing guide (ZHCA065) [R]. USA: Texas Instruments, 2008.

[6] Philips Semiconductors. SJA1000 stand?alone CAN controller application note (AN97076) [R]. [S.l.]: Philips Semiconductors,1997.

[7] 李俊萍,王静平.基于CPLD的DSP微处理器与CAN控制器接口的一种设计方法[J].现代电子技术,2007,30(9):56?58.