双四选一数据选择器74HC153的级联分析及研究

单嵛琼,单长吉

(昭通学院,云南昭通 657000)

双四选一数据选择器74HC153的级联分析及研究

单嵛琼,单长吉

(昭通学院,云南昭通 657000)

将多片双四选一数据选择器74HC153级联,再附加2线—4线译码器74HC139构成不同的数据选择器,能够灵活、有效地扩大数据选择器的使用范围。不同的74HC153进行级联时,任何时候只允许一个数据选择器工作,数据选择器的输出状态由地址输入端决定。

数据选择器;级联;译码器;地址输入端

1 74HC153简介

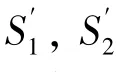

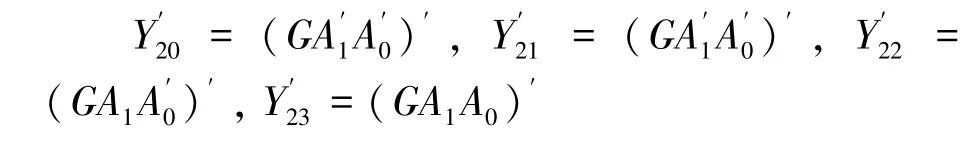

74HC153是双四选一数据选择器,一片74HC153上有两个四选一数据选择器,两个选择器的地址输入端是公用的,选通控制端和数据输入端是独立的,图1是它的逻辑符号:

图1 74HC153的逻辑符号

输入与输出之间的逻辑关系式为:

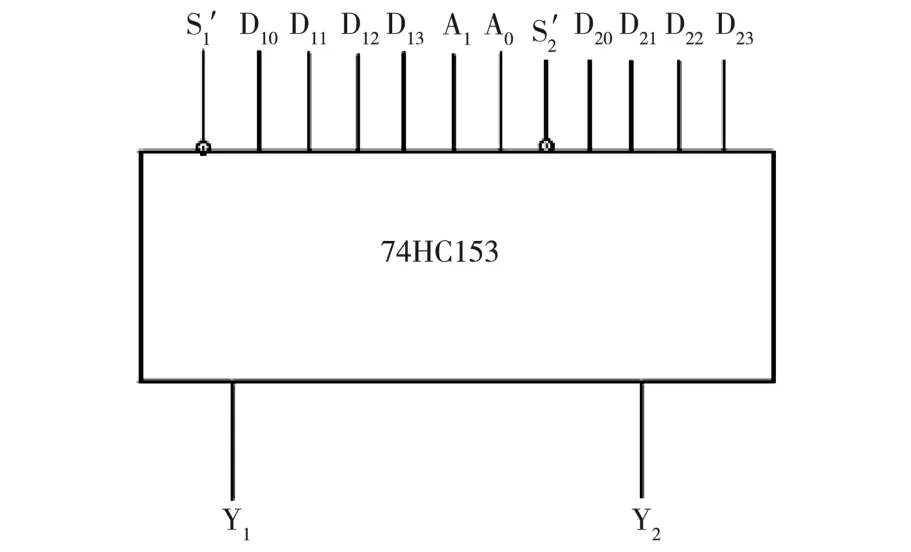

2 74HC139简介

图2 74HC139的逻辑符号

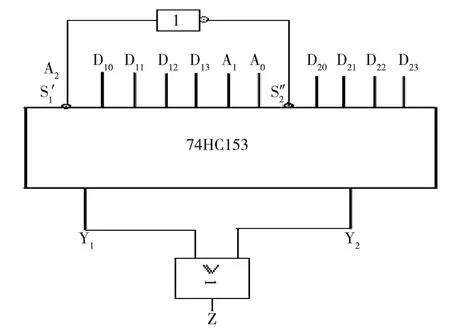

3 用74HC153中的两个四选一数据选择器组成八选一数据选择器

选择器结构图见图3。

图3 74HC153中的两个四选一数据选择器构成的八选一数据选择器的逻辑图

两个四选一数据选择器共有8个数据输入端,可构成八选一数据选择器。由于八选一数据选择器需要从8个输入数据中选择任何一个,所以输入地址必须有三位,才能给出8个不同的地址代码,而四选一数据选择器只有两个地址输入端,因而必须借用选通控制端第三位代码输入端,若把作为八选一数据选择器的A2输入端,A1作为八选一数据选择器的A1输入端,A0作为八选一数据选择器的A0输入端,通过非门接到端,Y1,Y2相或以后作为八选一数据选择器的输出端Z端。这样连接以后,可以构成八选一数据选择器。图3为74HC153中的两个四选一数据选择器构成的八选一数据选择器的逻辑图。

对图3进行工作原理分析:当A2A1A0为 000—011时,第一个四选一数据选择输入端的=0,第二个四选一数据选择输入端的,第一个四选一数据选择工作,当中的一个数据被选中后送至Y1,第二个四选一数据选择输出端的Y2=0,所以Z=Y1。当A2A1A0为100-111时,第一个四选一数据选择输入端的,第二个四选一数据选择输入端的,第二个四选一数据选择工作,当中的一个数据被选中后送至Y2。第一个四选一数据选择输出端的Y1= 0,所以Z=Y2。所以,该电路能具有8选一数据选择器的逻辑功能。

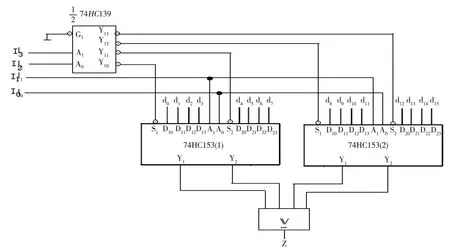

4 用两片74HC153和一片74HC139中的一个译码器构成16选一数据选择器

译码器结构图见图4。

图4 两片74HC153和一片74HC139中的一个译码器构成的十六选一数据选择器

十六选一数据选择器必须有16个数据输入端和4个地址输入端,两片74HC153中包含有4个四选一数据选择器,总共有16个数据输入端,满足对输入端数目的要求,而每片74HC153只有两个地址输入端,所以我们可以用2线—4线译码器将另外两位代码译成4个不同的低电平信号,分别去控制4个四选一数据选择器的选通控制端,这样可以构成16选一数据选择器。图四为用两片74HC153和一片74HC139中的一个译码器构成16选一数据选择器的逻辑图。

对图4进行逻辑功能分析:当I3I2I1I0为 0000—0011时,74HC139的输出为低电平,均为高电平,所以74HC153(1)的的(1)中的第一个四选一数据选择器工作,其它数据选择器均不工作,对应的输出74HC153(1)的Y1为d0—d3,Y2和74HC153(2)的Y1,Y2均为0,所以输出Z为d0—d3。当I3I2I1I0为0100—0111时,74HC139的输出为低电平,均为高电平,所以74HC153(1)的74HC153(2)的中的第二个四选一数据选择器工作,其它数据选择器均不工作,对应的输出74HC153(1)的Y2为d4—d7,Y1和74HC153(2)的Y1,Y2均为0,所以输出Z为d4—d7,同理可得当I3I2I1I0为1000—1011时,输出Z为d8—d11,当I3I2I1I0为1100—1111时,输出Z为d12—d15。所以I3I2I1I0为0000—1111时,输出Z为d0—d15。根据以上分析可知,该电路能具有16选一数据选择器的逻辑功能。

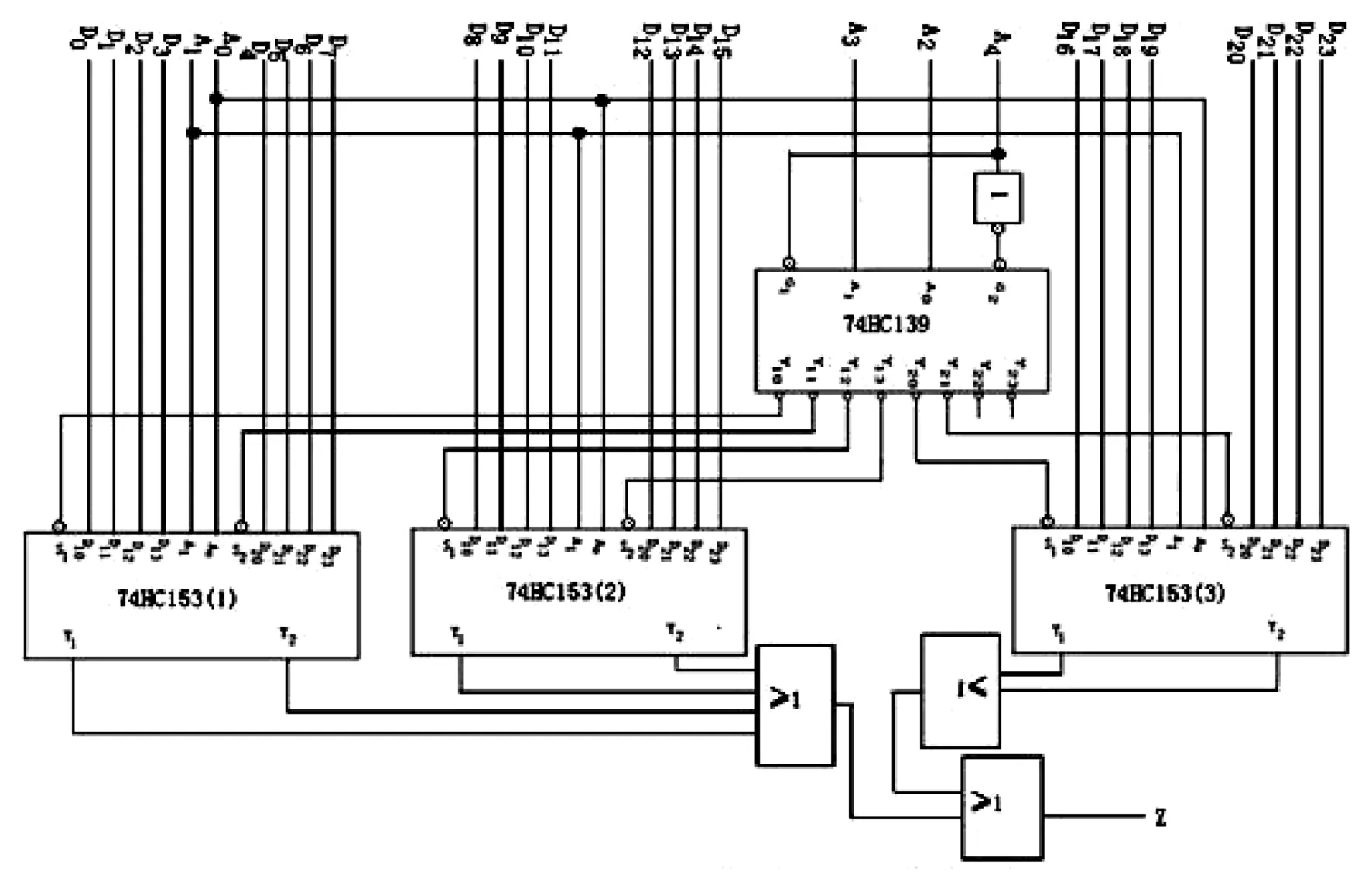

5 用三片74HC153和一片74HC139可构成24选一数据选择器

三片74HC153有24个输入端,再用一片74HC139可构成24选一数据选择器。连接时把74HC139的作为24选一数据选择器的A4端,A1端作为24选一数据选择器的A3端,A0端作为24选一数据选择器的A2端,3片74HC153的A1连起来作为24选一数据选择器的A1端,3片74HC153的A0连起来作为24选一数据选择器的A0端,74HC139的接74HC153(1)的接 74HC153(1)的接74HC153(2)的接74HC153(2)的接74HC153(3)的接74HC153(3)的悬空,这样可构成24选一数据选择器。图5是三片74HC153和一片74HC139构成的二十四选一数据选择器:

图5 三片74HC153和一片74HC139构成的二十四选一数据选择器

对图5进行逻辑功能分析:当A4A3A2A1A0为 00000—00011时,74HC139的输出为低电平,其余均为均为高电平,所以74HC153(1)的和74HC153(3)的1,74HC153(1)中的第一个四选一数据选择器工作,其它数据选择器均不工作,对应的输出74HC153(1)的Y1为d0—d3,Y2和74HC153(2)、74HC153(3)的Y1,Y2均为0,所以输出Z为d0—d3。同理可以得到,当A4A3A2A1A0为00100—00111时,输出Z为d4—d7,当A4A3A2A1A0为01000—01011时,输出Z为d8—d11,当A4A3A2A1A0为01100—01111时,输出Z为d0—d15,当A4A3A2A1A0为10000—10011时,输出Z为d16—d19,当A4A3A2A1A0为10100— 10111时,输出Z为d20—d23,当A4A3A2A1A0为11000—11111时,三片74HC153均不工作。根据以上分析可知,该电路能具有二十四选一数据选择器的逻辑功能。

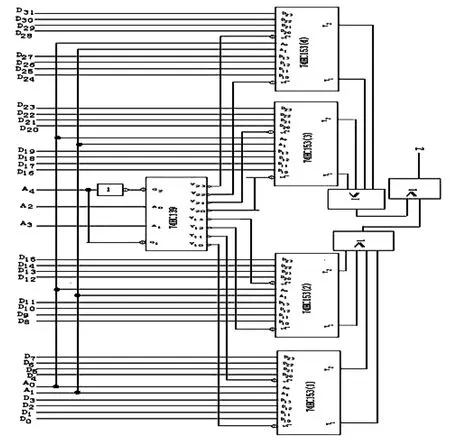

6 用四片74HC153和一片74HC139可构成32选一数据选择器

用四片74HC153和一片74HC139可构成32选一数据选择器时,只要在用三片74HC153和一片74HC139可构成24选一数据选择器的基础上,把接74HC153(4)的接74HC153(4)的即可。图6是四片74HC153和一片74HC139构成的三十二选一数据选择器。

图6 三片74HC153和一片14HC139构成的三十二选一数据选择器

其工作原理分析与3片74HC153和一片74HC139构成的24选一数据选择器的工作原理分析类似。

7 结 论

以上对四片以下74HC153级联作了介绍和分析,对于其他更多片74HC153的级联可依次类推进行设计和分析。可以看出,不同的74HC153进行级联时,任何时候只允许一个数据选择器工作,数据选择器的工作状态由其选通控制端S′决定,选择哪一个数据又由地址输入端决定。

[1] 余孟尝.数字电子技术教程[M].北京:清华大学出版社,1985:140-154.

[2] 阎石.数字电子技术教程[M].北京:清华大学出版社,2007:109-120.

[3] 黄庆元.数字电子技术教程[M].西安:陕西师范大学出版社,1995:82-95.

[4] 曲伟等.电子技术教程[M].北京:人民邮电出版社出版社,2013:182-190

[5] 司淑梅.电子技术基础[M].上海:复旦大学大学出版社,2008:164-174

[6] 阎石.数字电子技术基本教程习题解答[M].北京:清华大学出版社,2009:55-58.

The Analysis and Research of Cascadein the Data Selector 74HC153 from Double/Four Choose One

SHAN Yu-qiong,SHANG Chang-ji

(Zhao Tong University,Yunnan Zhaotong 657000)

It takes multiple pairs of data selectors 74HC153 from double/four choose one to cascade,which constitutes different data selector with additional to 2-4 lines decoder 74HC139,it can be flexibility,effectively enlarge the using range of the data selector.Different 74 hc153 cascade,at any time only allows a data selector to work,the data selector output state is determined by the address input.

data selector;cascade;decoder address input

O453

A

10.14139/j.cnki.cn22-1228.2015.02.012

1007-2934(2015)02-0044-05

2014-11-04