基于FPGA的LFSR异步加解密系统

潘必韬,聂小龙,王祖强

(山东大学 信息科学与工程学院,山东 济南 250100)

基于FPGA的LFSR异步加解密系统

潘必韬,聂小龙,王祖强

(山东大学 信息科学与工程学院,山东 济南 250100)

线性反馈移位寄存器(LFSR)伪随机序列作为流密码的一种,具有原理清晰、不可预测性强的特点,被广泛应用于各种加解密场合。针对目前基于 LFSR的加解密系统只能应用于同步工作模式的局限性,设计了一种可配置的LFSR异步加解密系统,并对其进行了基于FPGA的硬件实现。实验结果显示,其既具备LFSR序列的优秀性能,又可以实现异步加解密,具有一定的实际应用价值。

LFSR;FPGA;异步加解密

0 引言

随着信息技术的不断发展,信息安全已成为全世界的热门研究课题,而数据的有效加解密则显得尤为重要。虽然国内外研究者在软件加密层面上做了大量的工作,但仍存在着信息易被窃取等问题。相对而言,硬件加密因为其加解密过程在硬件中执行,加解密信息均存储于专用硬件之中[1],使得其更具安全性。因此,研究加解密系统的硬件实现更具有现实意义。

LFSR伪随机序列作为一种成熟流密码,其优点突出,且非常适合于硬件高速实现[2]。FPGA采用流水线和并行运算,在数据处理中具有灵活高效的特点,很适合于硬件加解密系统的设计与实现[3]。

虽然利用LFSR序列进行加解密的硬件实现已有大量实例,但其均为同步加解密,具有很大的局限性。本文所提出的异步LFSR加解密系统即是针对这一问题而作出的改进。首先对LFSR伪随机序列产生的基本原理进行了阐述;然后分析了一种基于LFSR伪随机序列的同步加解密系统;在此基础之上,提出了可配置的LFSR异步加解密系统的设计及其利用FPGA的实现,最后对全文进行了总结。

1 LFSR原理简介

一个m位的线性移位寄存器(LFSR)可以由 m个寄存器以及决定序列状态转换的反馈结构组成。用于硬件实现的LFSR的拓扑结构如图1所示。

该拓扑结构中gm代表反馈系数,其值为1表示连接,0表示未连接。每一时刻的各位寄存器的输出则为当前的序列输出值,下一时刻的输出由当前状态和反馈支路决定。其数学抽象形式可以表示为GF(2m)上的一个多项式,反馈系数则抽象成为其多项式的系数。如果反馈系数选取得当,使得其抽象多项式为GF(2m)上的本原多项式时,由m个寄存器组成的序列发生器可以有2m-1个不同状态[4]。所以,当 m的值增大时,该伪随机序列发生器的周期增长是非常可观的,在一个周期之内,其序列输出值不可预测,保证了其安全性,从而确保了加密效果。

2 现有的同步LFSR加解密系统

现有的这方面的一个典型系统工作原理[5]如图2所示。该系统设计用LFSR伪随机序列来加解密输入模拟信号。其基本原理是将输入待加密的明文信号与 LFSR序列进行两次异或来加解密,用 m、k、c分别来表示明文、密钥、密文,则由于:

所以第一次异或将明文信息加密,而第二次异或则将密文解密,得出明文信号。整个过程的关键在于时序的控制使其达到严格同步。该系统结构清晰,原理明确。但有几点缺陷:

(1)系统只在同步时可以进行工作,然而大多数情况之下这种即时加解密的方法不能满足需求。而需要先加密,传输,之后再解密。

(2)由于系统的加解密结构,使得一帧数据加解密工作要在一个LFSR序列信号周期内完成,将限制时钟频率、降低效率。

(3)由于该系统需要加解密序列严格同步,所以容错率低,且只要出现一位的偏移将影响整个系统。

对于以上问题,本文提出了一种可配置LFSR序列异步加解密系统,将在下文讨论。

图2 一种同步LFSR加解密系统

3 可配置的LFSR序列加解密系统

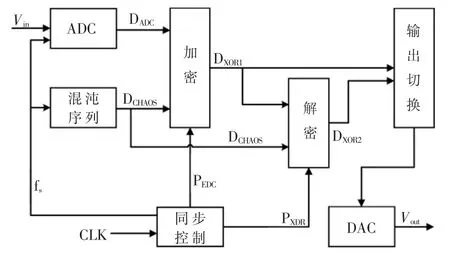

针对现有LFSR同步加解密系统所存在的问题,设计了一种异步加解密系统。该系统将在加密之前对LFSR进行配置,设置其初值和反馈结构。传输数据时将初值信号与反馈的配置信息封装于密文之前,解密时再根据其接收到的密文中的配置信息进行解密端配置,然后进行解密。整个过程将实现异步加解密,其结构如图3所示。

图3 异步LFSR加解密系统

其中最关键的部分为可配置 LFSR序列发生器,其总体结构如图4所示。为m个单个配置结构的并联。单个寄存器的配置器如图5所示。其中初值赋值部分为寄存器赋初值,而反馈系数赋值部分则用来配置反馈网络。

图4 可配置LFSR序列发生器

对于m位的LFSR序列产生器,其整体的配置模块

图5 单个寄存器配置示意图

其中初值配置模块如图6所示。它接收初值信号,当初值为1,即 input为1时,prn输出 0,clrn输出1,完成寄存器的置1设置。反之,当初值为0时,clrn输出 0,prn输出1,完成寄存器的置0设置。

其中反馈结构配置模块如图7所示。其接收到的输入信号为Qm与 gi,且当 gi为1时,表示连接,output输出Qm的值,当 gi为0时,表示未连接,则 output输出为0,因为x⊕0=x,与无连接的效果一样。

图6 初值配置示意图

图7 反馈信息配置示意图

4 加解密系统控制流程

基于前文所述的硬件结构,设计了整个加解密系统的工作流程,其加密与解密流程相对称,分别如图8和图9所示。

5 系统仿真及测试结果

5.1 系统仿真时序图

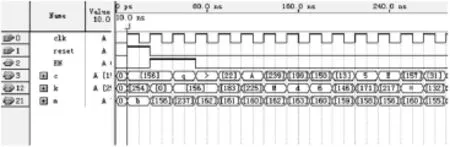

图10为可配置 LFSR加解密装置的加密过程仿真时序图。仿真所用的 LFSR生成器为8位,其最大周期为255。选用的反馈系数为g(8)=01110001(由于 g0默认为1,故从 g1开始配置)。

Reset信号触发之后,EN为初始配置信号变为有效,其占用 2个时钟周期,完成的工作为将初始的配置信息中的 Q0=10011100(156)与g(8)=01110001(q的ASCII码)存入输出信号 cout,并配置 LFSR生成器。当配置结束后,加密工作开始进行。输出密文c为明文m与LFSR输出密钥k的异或,最终输出 cout为加入配置信息的密文。相应地,其解密过程的仿真时序图如图11所示。

图8 加密流程图

图9 解密流程图

图10 加密过程的FPGA仿真图示

图11 解密过程的FPGA仿真图示

Reset信号触发之后,初始配置信号 EN变为有效,其占用2个时钟周期,完成的工作为将接收到密文c中的前两帧数据读出,并配置LFSR生成器。当配置结束后,解密工作开始进行,解密输出的明文从EN无效后开始。由图10、图11所示,其加解密过程都可以完美运行。

5.2 实际加解密测试结果

用上述加解密装置对一幅 512×512的灰度图像进行加密、解密可得其结果分别如图12、图13所示。可见加解密效果完美,可以实际使用。

图12 加密前原始图像

图13 解密后的图像

6 结语

本文设计了一种可配置的LFSR序列生成器以及其所应用的异步加解密装置。在对原始 LFSR加解密系统进行了阐述与分析后,提出了一种可配置的LFSR异步加解密系统,并对其进行了基于 FPGA的硬件实现。观察实验结果可知,其不仅具有异步加解密的实用性,又具有LFSR序列的可靠性。

[1]贾立恺,黄国庆,赵敬,等.基于 FPGA的PCI硬件加解密卡设计[J].电子设计工程,2010,18(5):142-145.

[2]胡向东.应用密码学[M].北京:电子工业出版社,2011.

[3]刘景亚,季晓勇.基于FPGA的CPRS混沌加解密算法高效实现[J].电子测量技术,2008,31(11):175-177.

[4]WADE TRAPPE(美).密码学与编码理论(第2版)[M].北京:人民邮电出版社,2008.

[5]刘卫玲,常晓明,王云才.基于FPGA和PSoC的混沌音频加解密系统[J].电子技术应用,2014,40(7):54-57.

Asynchronous LFSR encryption system based on FPGA

Pan Bitao,Nie Xiaolong,Wang Zuqiang

(School of Information Science and Engineering,Shandong University,Jinan 250100,China)

As a kind of stream cipher,linear feedback shift register(LFSR)pseudo random binary sequence(PRBS)has widely applied in many encryption occasions with characters like succinct principle and strong unpredictability,to solve the limitation that encryption system based on LFSR can only work in synchronous condition,this paper proposed a asynchronous configurable LFSR encryption system,and has implemented the system in hardware based on FPGA.The experiment results shows it not only applied the LFSR sequence′s outstanding performance but also implemented asynchronous encryption.It has a certain value of practical application.

LFSR;FPGA;asynchronous encryption

TN918

:ADOI:10.16157/j.issn.0258-7998.2016.06.015

潘必韬,聂小龙,王祖强.基于 FPGA的 LFSR异步加解密系统[J].电子技术应用,2016,42(6):56-58.

英文引用格式:Pan Bitao,Nie Xiaolong,Wang Zuqiang.Asynchronous LFSR encryption system based on FPGA[J].Application of Electronic Technique,2016,42(6):56-58.

2016-01-18)

潘必韬(1992-),男,硕士研究生,主要研究方向:FPGA在数字加密中的应用。

聂小龙(1992-),男,硕士研究生,主要研究方向:FPGA视频在视频编码器中的应用。

王祖强(1957-),男,硕士生导师,教授,主要研究方向:电子设计自动化及 ASIC设计。