PCI及USB 3.0在高速数据传输系统中的应用研究

石永亮 秦丽 张会新 刘文怡 樊刘华

摘 要: 设计一种USB 3.0+PCI的双接口数据传输系统,系统采用FPGA作为核心控制器,CYUSB3014和PCI9054作为USB 3.0与PCI接口芯片,实现上位机下发指令给远端采编存储设备,及存储设备的数据回传。设计中PCI接口采用单次访问结合突发访问的数据传输模式,USB通信高速稳定,且两个接口互为备用,相较于单一接口具有更高的可靠性。实践表明,该系统数据传输速率达到176 MB/s,保证可靠性的同时,相较于单一USB 2.0接口的12 MB/s有了大幅提高。

关键词: 高速数据传输; 双接口; PCI; USB 3.0

中图分类号: TN911?34; TP274 文献标识码: A 文章编号: 1004?373X(2016)08?0096?04

Application of PCI and USB3.0 in high?speed data transmission system

SHI Yongliang, QIN Li, ZHANG Huixin, LIU Wenyi, FAN Liuhua

(National Key Laboratory for Electronic Measurement Technology, MOE Key Laboratory of Instrumentation Science & Dynamic Measurement,

North University of China, Taiyuan 030051, China)

Abstract: A USB 3.0 and PCI dual?interface data transmission system was designed. A FPGA is used as the core controller in the system. CYUSB3014 and PCI9054 are adopted as interface chips of USB and PCI to achieve the functions that the host computer issued instructions to the remote storage devices, and collect the data returned from storage devices. The data transmission mode combining the single access with burst access is adopted in the design for PCI interface. USB communication is fast and stable, and the two interfaces are mutual backups of the two. Compared with the system with a single interface USB 2.0, whose data transmission rate is 12 MB/s, it has higher reliability. The practice shows that the data transmission rate of the system can reach up to 176 MB/s, while ensuring its reliability.

Keywords: high?speed data transmission; dual?interface; PCI; USB 3.0

0 引 言

飞行器的研制工作量大、系统复杂、成本昂贵,为了有效降低研制经费、加快研制进程,同时确保飞行试验的工作参数可靠有效,本文设计了一种地面高速数据传输系统。该系统旨在实现远距离控制采编存储设备的工作状态,同时能够远距离可靠并实时传输采编设备的数据,实现数据的回传分析[1]。本系统将PCI9054作为“桥接”芯片,采用单次访问结合突发访问的数据传输模式,实现主控芯片FPGA和PCI接口的数据传输。由于USB接口占用资源少,易于开发和集成,支持热插拔功能,串行接口选用了USB 3.0接口。本系统设置了自检功能,一旦其中一个接口出现问题就选择使用另外一个接口,即PCI和USB接口互为备用接口,保证了系统的可靠性,两种典型的串并接口,使得本系统在保证高速、可靠的同时也增强了该系统的通用性。

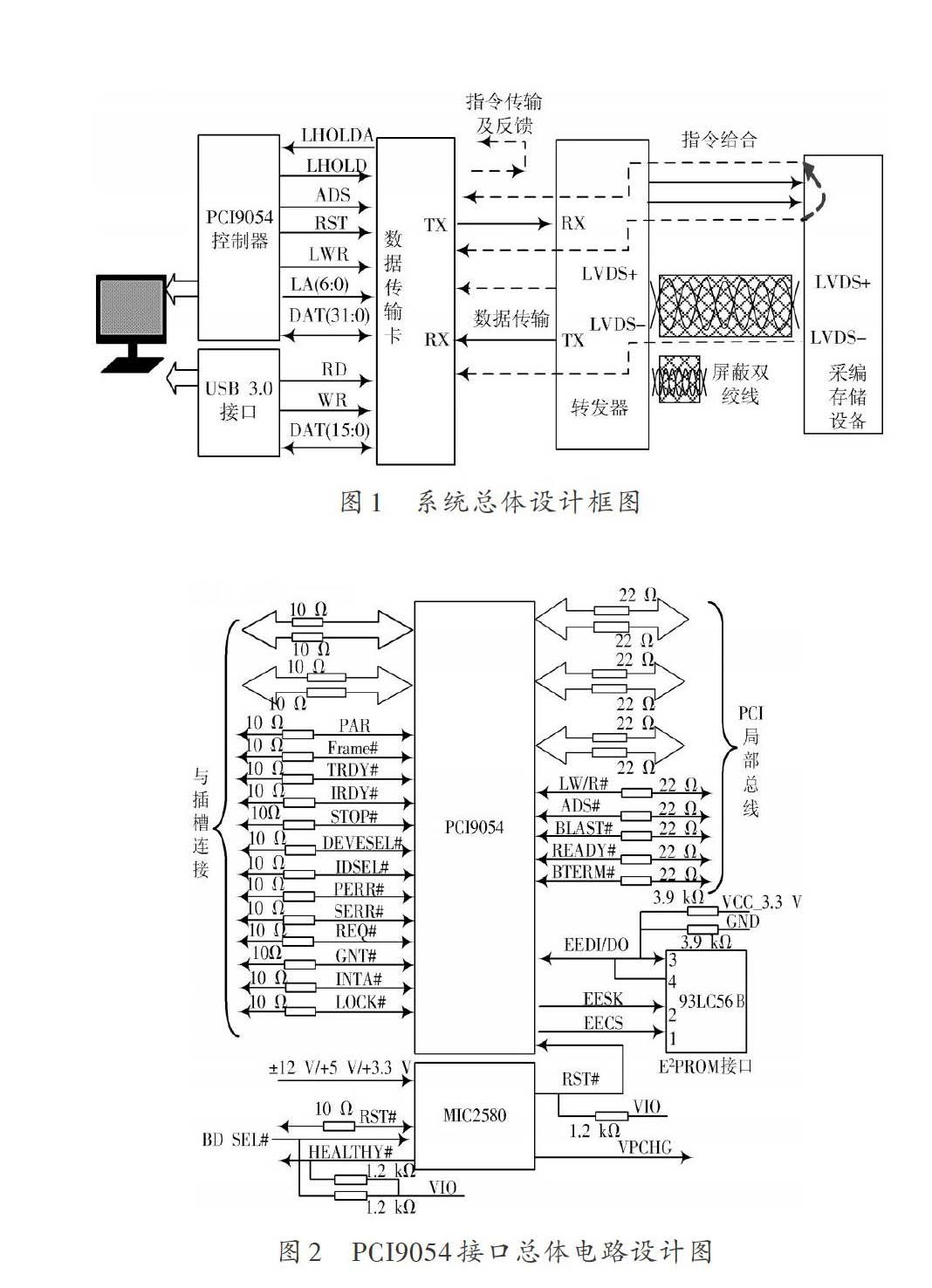

1 系统总体设计

本系统通过PCI或USB与上位机实现指令接收与数据回传,为了保证系统的工作可靠性,正常工作模式下,两接口互为对方的备用通信接口。系统接收上位机下发的命令后,通过数据传输卡转发到LVDS转发器,采用LVDS传输协议实现系统与远程采编存储设备的通信。系统总体设计如图1所示。

USB 3.0通信采用CYUSB3014芯片,相比于早期的USB接口,USB 3.0在物理层上增加了支持并行传输的线路,实现了超高速传输。USB 3.0的全双工数据传输模式,并兼容USB 2.0,双向并发的工作模式减少了在USB 2.0协议传输中的等待时间。由于PCI总线协议复杂,PCI总线接口开发一般采用通用PCI接口芯片FPGA方式实现PCI总线接口通信,通用接口芯片可以实现PCI目标和主控模块的接口功能,将复杂的PCI总线接口协议转化为比较简单的用户接口,这样保证了系统的可靠性。

2 硬件电路设计

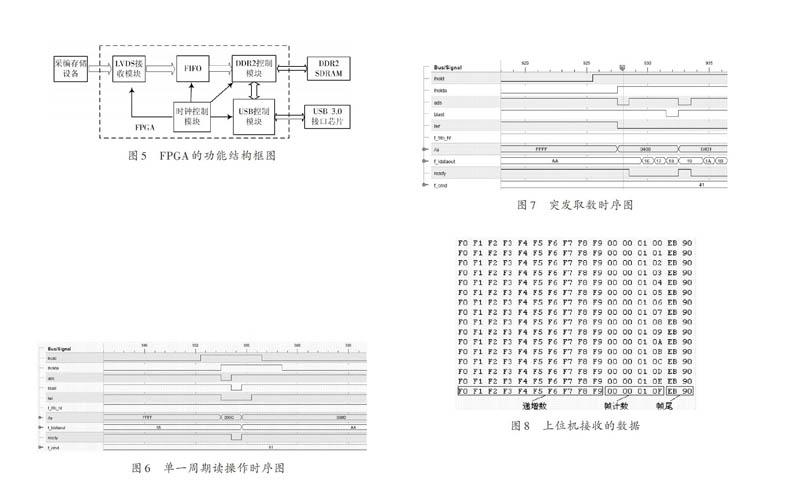

2.1 PCI接口电路设计

在PCI系统中,能够获取总线控制权的设备称之为主设备,被主设备控制的设备称为目标设备或从设备。本系统中的PCI传输设备为主设备,其接口电路总体设计框图如图2所示。

PCI总线信号是直接与PCI插槽相连接的地址/数据信号和PCI协议控制信号,这类信号包括系统信号CLK(时钟信号)、RST#(复位信号),地址/数据复用信号AD[31:00]、协议控制信号PAR(奇偶校验信号)、STOP#(停止信号)、FRAME#(帧周期信号)、DEVSEL#(设备选择信号)、IRDY#(主设备准备好信号)、TRDY#(目标设备),初始化设备选择信号IDSEL(初始化设备选择信号)、PERR#(数据奇偶校验错误报告信号)、SERR#(系统错误报告信号)。由于较高的背板阻抗会加剧瞬态干扰,为减小信号线上的分支对总线的影响,需要对总线信号进行串联匹配,匹配电阻为10 Ω,由于本地总线过冲比较严重,故本系统设计时串联22 Ω,以减小总线的过冲影响[2]。

PCI9054内部提供一个串行的E2PROM配置接口,为PCI总线和局部总线存储寄存器提供配置信息,设计中常选用93LC56B作为外接E2PROM。PCI9054上电后首先会自动读取E2PROM中的数据,若检测到第一个长字为非全0或非全1时,说明存在已经烧写好的E2PROM,上电后该芯片会为PCI9054的寄存器配置初始化参数[3],图2中,93LC56B的3、4引脚和EEDI/DO连接,并通过3.9 kΩ电阻分别接3.3 V和地,此处设计方便根据实际需求选择电路连接方式,当不需要E2PROM对PCI9054进行配置时选择下拉电阻接地,否则选择上拉电阻接3.3 V。

2.2 USB接口电路设计

USB 3.0控制芯片采用CYUSB3014,该芯片具有高度集成的灵活特性,并向下兼容USB 2.0协议。在实际应用中,USB接口经常接触人体,且频繁进行热插拔,为了加强接口的静电防护性能,本系统增加了外置ESD防护芯片,芯片采用Semtech公司的RCLAMP0524J芯片作为ESD防护器件[4],电路见图3。另外,将PMODE[2:0]配置成Z1Z模式,系统上电时USB3014选择I2C的引导方式,只需将配置好的固件程序通过I2C烧录进外部E2PROM,这样在重新上电时不需要重复下载固件。USB3014和FPGA的硬件通信实现只需要将USB3014的控制总线和数据总线分别连接到FPGA的I/O引脚上即可。在实际工作时,FPGA通过控制片选引脚SLCS#、中断控制引脚PKTEND#、写选通控制引脚SLWR#、读选通控制引脚SLRD#、输出使能控制引脚SLOE、时钟输入引脚PCLK以及缓存选择引脚A[1:0]等引脚来控制USB3014芯片的数据缓冲区的读写时序;而USB3014芯片通过状态标志引脚FLAGB和FLAGA引脚为FPGA提供数据缓冲区的空满状态;通过双向数据总线DQ[15:0],FPGA的高速I/O口与USB3014的数据传输接口进行16位的并行高速传输。

3 软件设计

FPGA控制单元选用XILINX公司的XC6SLX75作为主控芯片,以ISE14.7为开发环境,使用VHDL语言进行FPGA与PCI接口及USB接口通信协议的逻辑时序控制。

3.1 PCI接口软件设计

3.1.1 PCI通信协议

本地总线和PCI总线之间的数据传输有三种方式:PCI Initiator模式、PCI Target模式和DMA模式[5]。对于本系统,主要目的是将数据快速地上传至上位机,在DMA和PCI Target的突发模式皆满足速度要求的前提下,考虑到易操作性,选择上传数据采用突发模式,而下发命令采用DMA的单一周期访问模式。

图3 USB 3.0接口电路

本系统通过类似握手协议的方式来对指令确认反馈,以确保正确下发指令。工作模式具体是:上位机给地址0x0010下发一个指令,FPGA通过改地址获取指令,之后进行两种操作:一是通过将指令写入地址0x0020反馈给上位机;二是将指令发送给下一级设备。当指令反馈给上位机之后,上位机判断该指令是否与前一次发的一致,一致说明上位机下发指令成功,若不一致上位机自动重新下发指令,如果确认三次都不一致,则上位机显示发送失败,保证指令的及时性和准确性。本系统协议中上位机与功能板卡之间的指令约定为8 b,并约定4个地址用于交互指令和数据,地址分配如表1所示。

表1 地址分配关系表

3.1.2 读写程序设计

FPGA与PCI通过专用接口控制器PCI9054进行通信,实现单一周期和突发访问,需要的本地信号主要有:Lhold(本地申请总线信号)、LW/R#(读有效为低,写有效为高)、ADS#(有效地址和新总线的开始)、Blast#(决定一个单周期被执行或突发周期被执行)、Ready#(有效时表示总线上读的数据有效或者一次写数据传输结束)[6]。为了同时满足单一周期总线访问和突发方式传输数据的要求,FPGA程序采用了状态及方式,读写程序流程如图4所示。

FPGA内部逻辑从S0状态开始,判断ADS#是否为低电平。当上位机没有下发指令时,ADS#信号处于高电平,PCI总线一直处于空闲状态;当有指令下发时ADS#拉低,新的总线传输启动,进入S1状态进行单一周期访问。FPGA判断LW/R#信号状态,当LW/R#为高时执行写操作,即FPGA从本地数据端接收上位机下发的命令,一次单周期访问以Ready#、Blast#信号拉低结束。结束单周期访问后,状态机又跳回S0状态,根据协议,LW/R#信号为PCI Target读操作,传输的本地地址为指令确认地址,将前一次刚接收 的命令写入约定好的地址,并再一次结束单周期访问,跳回S0状态。同时上位机从0x0020获取指令与前一次下发的指令作对比,对指令进行确认反馈。

当通过单周期访问完成下发指令后,若指令中有上传数据指令,PCI总线会再一次启动单周期PCI Target读操作,将是否能获取数据的标志写入固定地址,传送给上位机进行判断,若是半满信号,说明FPGA准备好数据,状态机进入突发访问周期,上位机可以突发获取数据。

3.2 USB接口软件设计

USB3014的工作模式为同步Slave FIFO,将USB3014的GPIF端口配置为16位以匹配DDR2的位宽。GPIF接口作为双向通道,它既可以将计算机的命令等内容存入缓冲区以被FPGA读取,也可以从FPGA内部接收数据存入缓冲区回传至计算机。FPGA作为Master对从属器件USB3014的内部缓冲区进行突发或单周期数据存取,FPGA通过改变逻辑状态来选择对USB3014执行读写操作, USB3014给FPGA提供FLAGA/FLAGB信号作为缓冲区的空/满标志,FPGA中的控制模块就会根据空/满标志的状态来决定是否暂停其读或写的行为[7?8]。本传输系统USB 3.0模块的程序功能主要为:时钟管理模块通过CMT对外部输入的50 MHz进行分频倍频处理,产生FPGA的工作时钟以及与其他芯片诸如DDR2以及USB3014的通信时钟; FIFO管理模块将通过LVDS接收的数据进行缓存,来解决不同模块间数据传输的跨时钟域及位宽不同的问题,将数据写入DDR2;DDR2控制模块是调用IP核来实现FPGA对DDR2的控制,对其进行充电、激活等操作[9];USB 3.0控制模块是对USB3014进行控制,并识别其标志信号,最终实现把DDR2 SDRAM中的数据通过USB 3.0接口批量回传给上位机。FPGA的功能结构框图如图5所示。

4 测量结果与分析

4.1 PCI接口仿真测试

接口测试过程中用Chipscope进行在线仿真调试,下发指令采用单一周期访问模式,各信号时序如图6所示,回传数据采用突发传输模式,测试时序如图7所示,仿真结果与本文中第3.1.1节PCI通信协议完全相符。

4.2 数据分析

通过搭建地面测试平台对该传输系统进行测试,测试过程中为便于分析,采编存储设备中存储的数据是带有帧标志的递增数,采编存储设备接收到指令后从FLASH中读取数据并通过LVDS发送给本文中的高速数据传输系统,本系统通过USB 3.0及PCI接口分别接收数据回传给上位机,数据解析如图8所示,分析结果:数据传输稳定可靠,没有丢帧及误码现象,下发指令正常。

5 结 语

本文主要介绍了一种基于PCI+USB 3.0的双接口高速、高可靠性数据传输系统,从硬件电路设计及软件通信协议入手,详细阐述了PCI和USB两个接口在高速数据传输系统中的关键技术应用,并搭建平台进行数据测试分析,验证了该系统的性能,满足任务需求提出的远距离高速可靠性传输,实现速率176 MB/s的数据传输。

参考文献

[1] 曹赛男.基于FPGA的PCI接口控制器的设计与应用[D].南京:南京航空航天大学,2012.

[2] 董海兰,康怀祺,钟午.基于FPGA的多接口高速PCI传输系统设计[J].火控雷达技术,2012(4):43?47.

[3] 张丹红,张孝勇,刘文.基于PCI9054的数据通信接口卡设计[J].武汉理工大学学报(信息与管理工程版),2013,35(3):49?54.

[4] 薛圆圆,赵建领.USB应用开发宝典[M].北京:人民邮电出版社,2011.

[5] 王骐,王青萍.基于PCI9054的DMA和突发数据传输实现[J].物联网技术,2011,1(3):86?88.

[6] 郭柳柳,储成君,甄国涌,等.基于PXI总线高速数据传输卡的设计[J].计算机测量与控制,2014,22(6):1899?1901.

[7] 李泽明.基于USB 3.0接口的高速数据传输电路设计与实现[D].太原:中北大学,2013.

[8] LIN Mushan, TSAI Chien?Chun, CHANG Chih?Hsien. A 5Gb/s low?power PCI express/USB3.0 ready PHY in 40 nm CMOS technology with high?jitter immunity [C]// IEEE Asian Solid?State Circuits Conference. [S.l.]: IEEE, 2009: 16?18.

[9] 黄万伟,董永吉,伊鹏,等.Xilinx FPGA应用进阶[M].北京:电子工业出版社,2014.