基于CPCI的动态可重构系统设计与实现

熊璐

摘 要: 近年来航天测控任务出现了测控目标多,信息传输量大,工作模式多样化等特点,为了满足实际测控任务中对设备的处理能力和灵活性的更高要求,该文实现了一种基于CPCI的动态可重构系统设计。在基带设备中通过应用程序将配置文件由CPCI总线根据需要实时写入到信号处理板上,并由主控FPGA将配置数据加载到核心处理器件FPGA和DSP中。与传统的FPGA和DSP加载方式相比,这种方法可以在极短的时间实现基带设备不同功能和模式的快速切换,不仅节约了硬件资源同时也使系统具有较大扩展性和灵活性,能够满足不同应用需求。该文给出这种可重构系统的详细设计和工程中的典型应用,该设计已经在实际中应用并取得理想的效果。

关键词: FPGA; DSP; 动态配置; CPCI

中图分类号: TN911?34 文献标识码: A 文章编号: 1004?373X(2016)08?0104?04

Design and implementation of dynamic reconfigurable system based on CPCI

XIONG Lu

(The 10th Research Institute of CETC, Chengdu 610036, China)

Abstract: In recent years, many features of multi?target, large amount of information transmission, and diversification of work mode have appeared in aerospace tracking and control tasks. In order to meet the higher requirements of the device processing capacity and flexibility in actual observation and control tasks, the design of dynamic reconfigurable system based on CPCI is realized in this paper. In the baseband device, the configuration files are written on the signal processing board through CPCI bus in real time according to requirements, and then the layout data is loaded to FPGA and DSP by main?control FPGA. Compared with traditional loading modes of FPGA and DSP, this method can realize the fast switch of different functions and modes of base band equipment in very short time. It not only saves the resources of system, but also make the system have greater expansibility and flexibility. The design of this kind of reconfigurable system is discussed in detail and the typical application in practical project is given in this paper, which has achieved an ideal effect in practical work.

Keywords: FPGA; DSP; dynamic configuration; CPCI

近年来随着航天事业的发展,测控任务出现了测控目标多,信息传输量大,工作模式多样化等特点,因此对设备的处理能力和灵活性提出了更高要求。通过动态实时的重构基带设备,使其具有不同的测控功能,不仅能够满足多种场合的任务需求还节约了硬件资源和设备成本,具有灵活、高效等特点。

1 CPCI总线概述

CPCI(Compact Peripheral Component Interconnect)总线是一种高性能局部总线,数据总线为32位,可扩展为64位,数据传输速率[1]为128~528 MB/s。由于CPCI 局部总线独立于处理器的独特设计和其高性能、低成本、开放性等方面的优势,它在航天领域的应用相当广泛。在本设计中通过CPCI总线进行配置数据流的传输,相对于传统的电缆和网络下载具有速度快、延时小、可靠性高等特点。

2 硬件实现

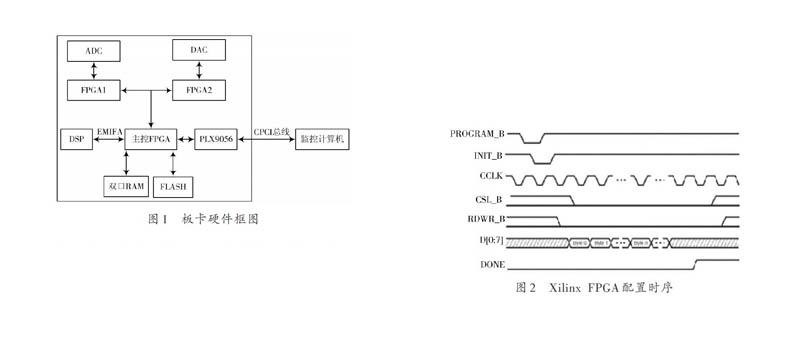

图1为应用于某航天地面测控基带设备中CPCI信号处理板卡硬件框图。FPGA1和FPGA2为Xilinx 公司VIRTEX 6系列FPGA,对ADC采样中频输入信号的数据进行功率调整,数字滤波,载波恢复,信息提取,位同步,帧同步,信息提取,调制等处理。DSP为 TI公司的TMS320C6455,实现参数计算,频率捕获,传输控制等功能。主控FPGA是采用Xilinx公司的VIRTEX 5 FPGA实现,完成板上V6 FPGA和DSP程序的加载,电源管理与各芯片之间的接口控制等功能。双口RAM用于缓存上报监控计算机的数据和DSP的配置数据。PLX9056为CPCI总线接口芯片,实现PCI协议到本地总线的转换。监控计算机通过CPCI总线将数据读取后进行后续处理,同时监控计算机还可以通过CPCI总线把需要调制的数据注入到FPGA和DSP中,调制后由DAC转换成模拟中频信号。通过监控计算机的人机交互界面可实现对板卡的参数控制、状态监视、信息存储等功能。

为了实现动态重构,以监控计算机为主设备,通过CPCI总线将配置数据送到底层板卡上,并控制整个配置流程。主控FPGA作为配置数据的通道,与板卡FPGA1,FPGA2,DSP接口,并且设计了配置状态机用于实现FPGA的配置时序。将不同模式的硬件配置文件存放在监控计算机硬盘中,通过监控软件实时加载不同的模式配置文件,即可实现系统重构,完成测控功能切换。

3 FPGA动态配置

3.1 Xilinx VIRTEX 6系列FPGA配置方式介绍

现场可编程门阵列(Field Programmable Gate Array,FPGA)以其高度的灵活性以及丰富的I/O资源与内嵌模块等优势,在航天领域越来越广泛的应用[2]。Xilinx公司根据FPGA是否能够自己主动加载配置数据分为主模式、JTAG模式以及从模式[3]。主模式根据配置数据位宽和控制时序的不同又分为Master Serial,Master SPI,Master BPI?Up,Master BPI?Down,Master SelectMap等几种接口。

主模式加载片外非易失性存储器中的配置比特流,配置所需的时钟信号由FPGA内部产生,且FPGA控制整个配置过程。在主模式下,FPGA上电后,自动将配置数据从相应的外存储器读入到FPGA内部SRAM中,实现内部结构映射。JTAG 模式主要用于调试,可将PC 中的比特文件流下载到FPGA中,断电后丢失。

在JTAG模式下,配置时钟为JTAG接口的TCLK,数据直接从TDI进入FPGA,完成相应功能的配置。从模式需要外部的主控设备(如处理器、微控制器或者DSP等)将数据下载到FPGA中,其最大的优点在于FPGA的配置数据可以放在系统的任何存储部位,如:硬盘、FLASH、网络等。

从模式根据配置数据的位宽不同又分为Slave SelectMap和Slave Serial两种模式。在从模式下,FPGA 作为从属器件,由相应主控设备器配置所需的时序,实现配置数据的下载。

通过设置FPGA的MODE引脚的值,可以改变FPGA的配置模式。在本设计中选用了并行从模式即Slave SelectMap来实现FPGA的动态配置。

3.2 FPGA动态配置设计实现

该模式的配置主要由以下信号进行控制:

PROGRAM_B:为低时复位芯片,复位后INIT_B变成低表示FPGA正在初始化配置存储,当采样到MODE引脚的值后,如果没有发生CRC错误INIT_B将拉高,若发生CRC错误,则INIT_B为低。

RDWR_B:控制配置数据的方向,为高时从FPGA读取配置数据,为低时向FPGA写入配置数据。

CSI_B:片选信号为低时,使能SelectMap总线。在只有一片FPGA的情况下,可以将此引脚直接接地。

CCLK:配置时钟。在VIRTEX 6系列FPGA中,CCLK最高[4]可以达到105 MHz。但由于受到PCB工艺布线等因素影响,过高的时钟往往会受到信号过冲,建立保持时间等的影响,导致配置失败。因此为了保证配置的可靠性在本设计中采用主控FPGA产生50 MHz时钟输出给待配置FPGA。

D[0∶7]:8 b配置数据信号。在Xilinx的ISE开发环境中,对FPGA的工程进行编译,可以生成配置所需的不同二进制文件。FPGA 的配置文件有多种不同的格式,例如BIT,BRT,BIN,MCS,EXO,TEK,HEX等[5]。ISE软件调用 Bit Gen 程序可直接生产BIT和BIN文件。由于BIN文件仅有配置数据无其他多余信息,因此在本设计中采用了BIN文件进行配置。

DONE:高有效,表示配置成功。

如图3所示为主控FPGA中用户逻辑的模块划分框图及与片外FPGA的配置信号连接图。地址译码及数据通路模块实现与PCI9656的接口,对PCI总线的地址进行译码和数据传输控制。FIFO用于缓存配置数据。配置控制模块实现动态配置的控制逻辑状态机。配置状态模块把FPGA1和FPGA2的状态上报到计算机。FPGA1和FPGA2所有需要配置的信号连接到主控FPGA的I/O引脚上。

当需要动态改变FPGA配置内容时,计算机将配置数据通过CPCI总线按字节把配置文件数据经过PCI9656写入FIFO中。主控FPGA中的配置控制逻辑检测到FIFO非空后,并判断配置哪一块FPGA后,读取FIFO中的数据,并按照图 2中配置模式的时序把配置数据连续写入FPGA1或FPGA2中。配置成功后,被配置的FPGA将自动拉高DONE信号电平,此时计算机可通过读取该信号的值来监测被配置FPGA的状态,判断是否配置成功。

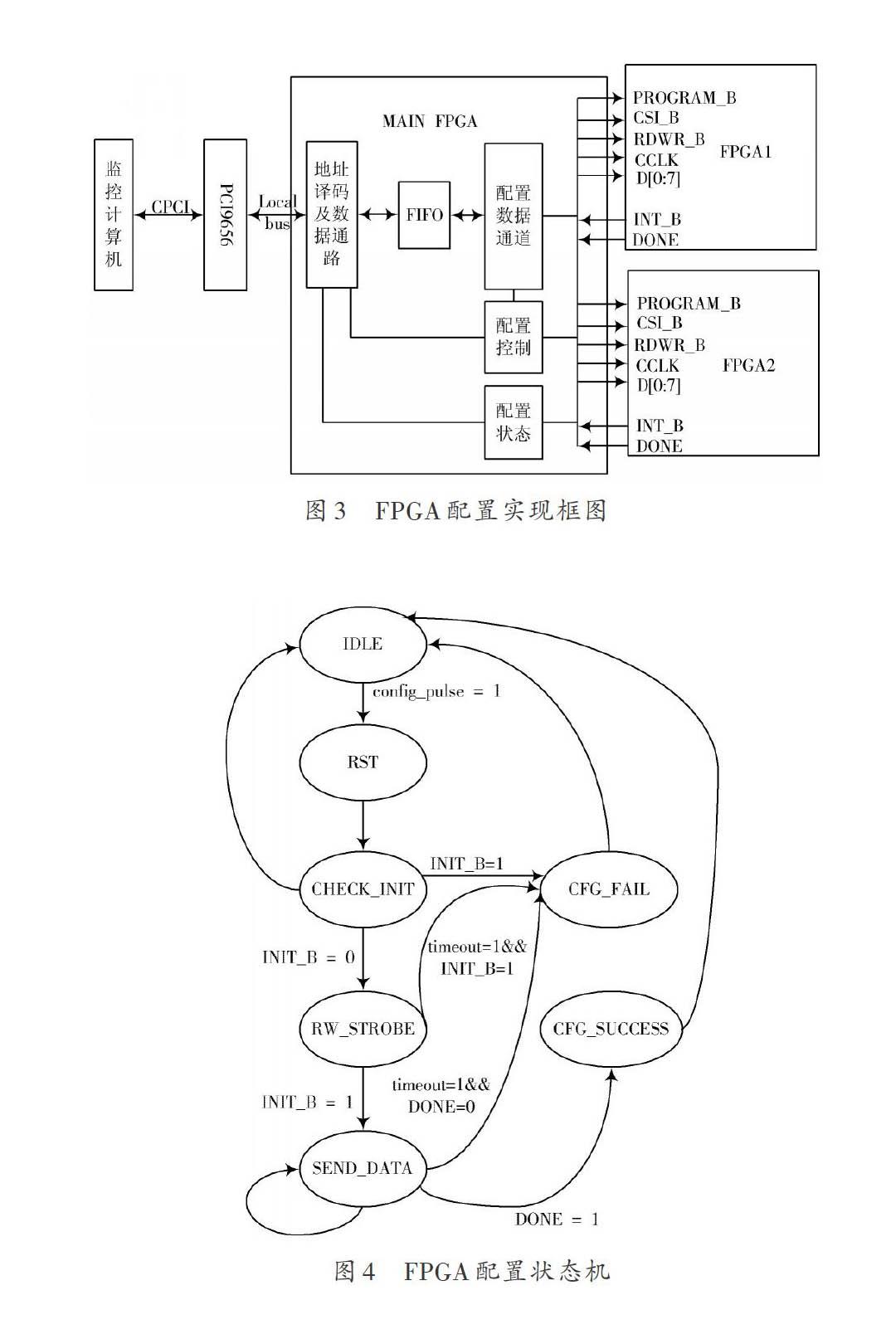

为了实现图2配置时序,在主控FPGA配置控制模块中通过Verilog HDL代码设计了具有图4状态转换图的状态机[6]。

IDLE状态:该状态为初始状态,等待总线配置命令。当需要进行模式切换时,监控计算机向映射到内存空间的CPCI指定地址写入0,1,0产生开始配置的脉冲config_pulse。状态机检测到总线的开始配置脉冲后,进入RST状态。

RST状态:在该状态下,主控FPGA拉低PROGRAM_B,被配置FPGA进入复位状态。为了保证复位的有效性,复位时间[5]至少不低于250 ns。被配置FPGA复位以后,拉高PROGRAM_B,状态机进入CHECK_INIT状态。

CHECK_INIT状态:在该状态下通过检测INIT_B信号判断是否进行状态转换。若复位成功,被配置FPGA将清除用于配置的内部存储,并拉低INIT_B。当状态机检测到INIT_B为低后,状态进入RW_STROBE状态。如果该状态下INIT_B仍为高,表示配置失败,进入CFG_FAIL状态,结束配置。

RW_STROBE状态:在该状态下,判断被配置FPGA的内部SRAM是否完成初始化,为下一步写入配置数据做准备。当FPGA内部SRAM初始化完成并且没有发生CRC错误时,INIT_B信号将变高。一旦状态机检测到INIT_B为高,主控FPGA拉低RDWR_B信号,进入SEND_DATA状态。当内部计时器超过设定时间1 s,INIT_B还未变高,则进入CFG_FAIL状态,结束配置。

SEND_DATA状态:在该状态下,主控FPGA完成将配置数据送入待配置FPGA的功能。若FIFO不为空,读取FIFO中的配置数据,并将数据送入FPGA中。FIFO作为配置数据的通道需要被上层应用和配置逻辑监测空满状态。上层应用通过CPCI总线读取FIFO的状态,若FIFO数据半满则需要向FIFO中写入一部分配置数据块。监控计算机由于在实际应用中有多个线程同时运行并且受到CPCI总线传输效率不高的因素影响,虽然采用了DMA传输方式,写入FIFO的数据速率仍会低于50 MB/s的配置速率,因此会出现FIFO空的情况。若出现FIFO空,则需要拉高CSI_B信号,当FIFO中有配置数据之后才拉低CSI_B,保证配置数据的连续性。若监控计算机发生异常导致FIFO数据中断,将进行超时判断,超时后进入CFG_FAIL状态,并结束配置。写完配置数据后,检测DONE信号,若为高则表示配置成功,进入CFG_SUCCESS状态,结束配置。若检测到DONE信号一直为低,则进入CFG_FAIL状态,并结束配置。

CFG_SUCCESS状态:前一状态若检测到DONE信号为高,则进入该状态,表示本次配置成功,并在下一个时钟周期,进入初始IDLE状态。

CFG_FAIL状态:配置超时或者数据传输异常,DONE信号无法拉高等情况下,都进入该状态,表示配置失败。

4 TMS320C6455DSP动态加载

4.1 TMS320C6455 DSP概述

TMS320C6455 DSP是TI公司的一款高性能DSP,不仅具有高速的数据运算能力,还有丰富的外部接口,如外部存储器EMIF接口,高速串行接口Serial RapidIO,PCI接口,三速以太网MAC控制器等[7]。

TMS320C6455 DSP内部有丰富的存储资源,它的L2级RAM存储容量达4 Mb/s,分配的内存地址范围为0x00800000~0x009FFFFF。为了满足更多应用对内存的需求,可以通过DDR2控制接口或EMIFA接口扩展系统的内存。

4.2 基于EMIFA接口的启动过程

DSP的启动是将程序和数据段加载到其内部存储空间,并且初始化内部寄存器的过程。通常启动模式主要有:NOBOOT模式、主机(HPI/PCI接口)模式、EMIFA模式、主I2C模式、从I2C模式、SRIO模式等模式。本设计中采用了EMIFA片外ROM启动模式。TMS320C6455 DSP的EMIFA接口能与各种外部设备接口,如SRAM,FIFO,ROM,FLASH等。EMIFA对应的DSP的地址空间分为4片空间,分别对应的片选信号CE2~CE5,可扩展的地址空间达1 GB。

上电复位后,DSP通过DMA/EDMA控制器,自动将存有程序代码的片外存储器中1 KB数据搬移到起始地址为0x800000的内存中[8]。搬移完成后,DSP将从该地址执行程序。通常在这段1 KB程序里存放为Bootloader程序,Bootloader程序将保存在片外存储器中的其他程序数据搬移到DSP L2 RAM空间中,并在搬移完成后让DSP跳转到程序起始处开始执行,此时DSP完成整个启动过程。

4.3 DSP动态配置的实现

如图1所示,DSP的EMIFA CE3的地址数据等控制信号通过主控FPGA与双口RAM和FLASH连接。在板卡上电的初始状态下,DSP的EMIFA的CE3信号线通过MAIN FPGA与FLASH连接。当需要进行功能切换时,计算机首先通过CPCI总线将DSP的程序二进制文件写入双口RAM中。然后控制主控FPGA将EMIFA CE3的数据、地址、控制等信号切换到双口RAM上。为了让DSP重新启动,监控软件向主控FPGA中复位寄存器写入1,产生复位DSP的脉冲。DSP复位之后,重新开始启动过程,但通过EMIFA CE3地址空间访问的内存将不再是FLASH,而是片外双口RAM。DSP加载双口RAM中的程序数据后,实现DSP功能的切换。由于片外双口RAM比FLASH具有更高的工作时钟,这种DSP的启动方式,相对于FLASH加载的方式,不仅可以减少烧写FLASH的环节,缩短DSP的启动时间,而且可通过监控软件的人机界面随时更改DSP加载的程序内容,具有很大的灵活性。

5 结 语

本系统利用CPCI总线传输不同的配置文件实现系统的可重构,具有简单,易于开发的特点。通过应用软件实际测试,整板(包括2片FPGA,1片DSP)的重构时间不超过2 s。CPCI总线结构动态重构系统具有很大的优越性,不仅数据传输速率高,资源利用率高,减小了系统规模功耗,而且可以对不断变化的环境迅速适配。本设计已应用于实际工程中,并取得了良好的效果。

参考文献

[1] BUDRUK Ravi, SHANLEY Tom, ANDERSON Don. PCI Express系统体系结构[M].北京:电子工业出版社,2005.

[2] 王文华,韩双丽,张宇.航天应用FPGA配置可靠性研究[J].空间科学学报,2011,31(1):106?111.

[3] Xilinx Technology Inc. Virtex?6 FPGA configuration user guide [EB/OL]. (2012?09?11) [2015?04?20]. http://www. xilinx.com/support/documentation/user_guides/ug360.pdf.

[4] Xilinx Technology Inc. Virtex?6 FPGA data sheet: DC and switching characteristics DS152 [EB/OL]. (2011?04?01) [2015?04?20]. http://www.xilinx.com/support/documentation/data_

sheets/ds152.pdf.

[5] 孟龙,郄志鹏,朱江,等.基于CPCI总线的FPGA加载设计[J].通信技术,2013,46(5):127?129.

[6] Xilinx Technology Inc. A CPLD?based configuration and revision manger for Xilinx platform flash PROMS and FPGAs [EB/OL]. (2005?01?19) [2015?04?22]. http://www.xilinx.com/support/documentation/application_notes/xapp693.pdf.

[7] Texas Instruments Inc. TMS320C6455 fixed?point digital signal processor [EB/OL]. (2012?03?23) [2015?04?10]. http://www.ti.com/lit/ds/symlink/tms320c6455.pdf

[8] Texas Instruments Inc. TMS320C6000 tools: vector table and boot ROM creation[EB/OL]. (2004?04?20) [2015?04?11]. http://www.ti.com/lit/an/spra544d/spra544d.pdf