40nm工艺32x32b双端口SRAM的设计与优化

摘 要 这篇文章主要论述了在具体的工程实践中,由于6TSRAM在40nm工艺下的集成电路设计中表现出的性能和功耗均达不到设计要求,而在物理设计当中由寄存器组成的存储体的面积和功耗更难以胜任,所以需要定制设计一款32X32双端口8TSRAM。在先进工艺下8TSRAM所表现的性能和功耗均胜于前两者,在FT-X的芯片上运用该结构有效优化了时序和功耗。

【关键词】SRAM 定制设计 性能 功耗

1 引言

Cache的设计是芯片集成电路设计重要的一部分。高效、快速的SRAM一直以来都是集成电路设计者始终追求的目标。

对于SRAM存储单元来说,它第一个必须具备的优点就是高稳定性,这样才能保证存储体进行正确的读、写操作。在0.18u工艺、0.13u工艺,6T单元具有很好的稳定性,而且由于它面积小的特点,一直备受设计者的青睐。但是,随着CMOS工艺尺寸的发展,在进入65nm、45nm、32nm甚至22nm之后,6管SRAM由于其存储结构的特点,数据输出皆是通过敏感放大器检测位线电压差,并将电压差进行放大输出。但是随着工艺尺寸的缩小和电源电压的降低,6管存储单元的稳定性越来越差,抗噪声能力越来越弱,使得敏感器的开启与关断时间很难控制,而且时常会发生位线的一个噪声电压被敏感放大器放大输出的错误操作。由寄存器组合成的存储模块其面积和功耗是所有低功耗设计者的噩梦。

本文通过实际工程项目中出现的问题,由于6TSRAM和寄存器组成的SRAM在后端物理设计当中出现面积、功耗和时序的问题制约了芯片性能的提升,用8TSRAM进行全定制设计替代芯片中的部分存储模块,最后进行数据对比证明了8TSRAM在纳米级工艺下的重要作用。

2 电路设计

2.1 写路径

写IO模块由32个1倍的DFF和64个4倍的反相器组成,写数据在写门控时钟WCLK控制下,产生WBL<31:0>以及WBLB<31:0>,在写字线WWL<31:0>控制下写入存储单元。

2.2 读路径

IO读出电路分为全局与局部两级电路进行读出,每根局部读位线上挂8个cell,一个局部读出单元电路对两根局部位线进行预充,局部IO电路是16选1。

2.3 时钟模块

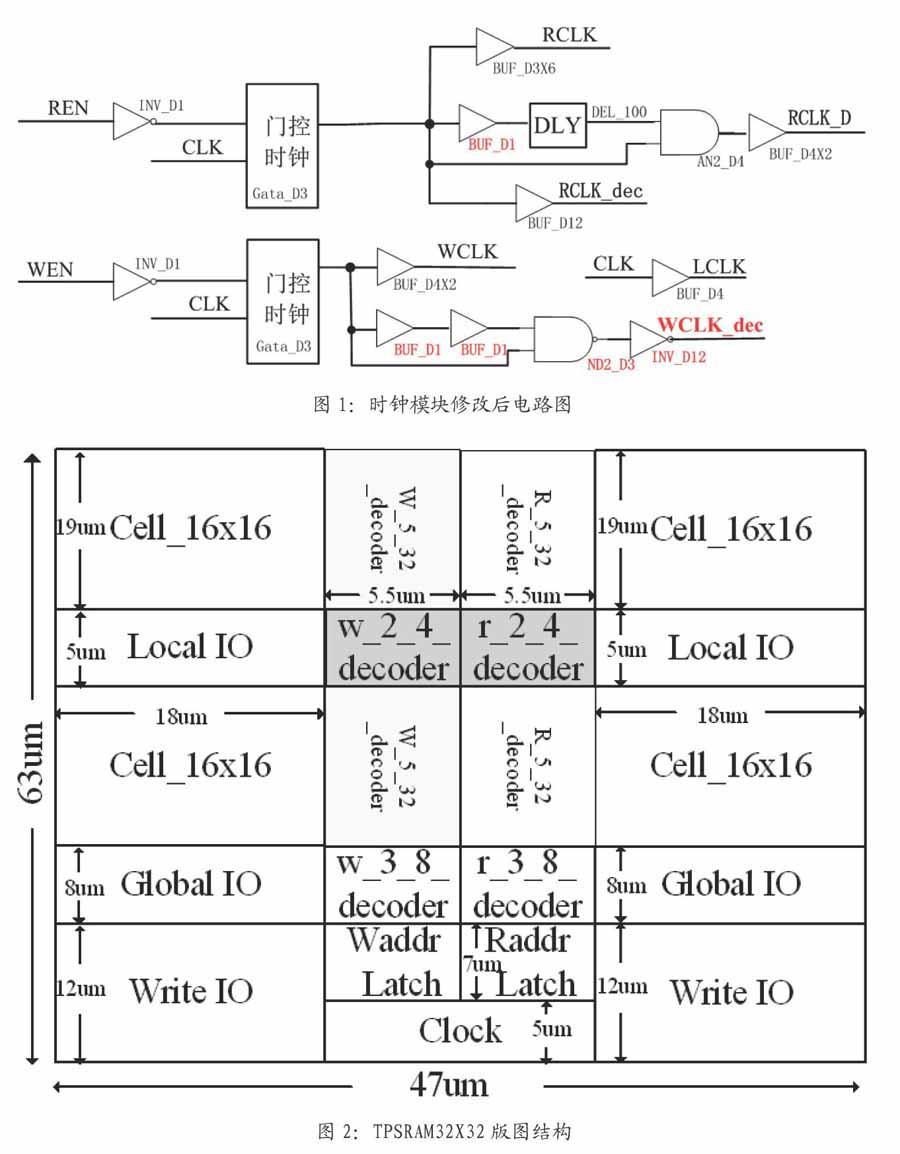

图1为时钟模块修改后电路图。为解决写时序中写字线先于写数据稳定的问题,适当推迟写译码时钟WCLK_DEC(推迟约90ps)的开启时间,且不推迟写译码时钟的关断时间(防止字线产生毛刺);为解决读时序中读出数据存在毛刺的问题,适当推迟求值时钟RCLK_D(推迟约20ps)的开启时间。

3 版图设计

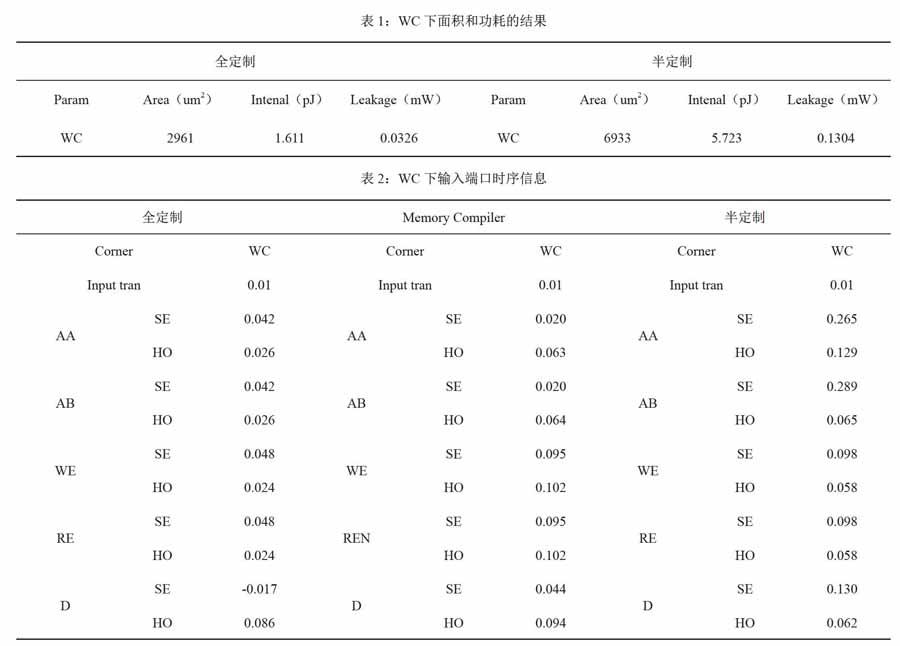

版图结构按功能进行划分,主要包括以下几个部分:中间部分从上至下依次为读写地址二级译码、读写地址预译码、读写地址锁存器、时钟模块;左右两侧为阵列模块,阵列cell中间为Local IO模块,阵列下面依次为Global IO模块、Write IO模块。

整个版图左右两边为阵列,中间为译码及时钟,左右两边距离边界阱不小于1.3um;整个版图上下各加一行DCAP单元,高度为1.68um。图2是存储器的版图布局规划图,下面分别对这几个部分进行说明:

3.1 阵列模块

阵列位于整个存储器的左右两边,由32个32位cell单元组成,阵列左边和右边各有32×16个cell单元,其中上下各有16×16个。

3.2 时钟模块

为减缓电路电压的波动,时钟模块被DCAP单元包围;为减小时钟线上电流密度,时钟线线宽加宽至0.08um;为降低时钟线的耦合串扰,时钟线尽量不与除电源地线外的长线互连线并行走线或者加大与信号线间的间距,尽量被电源线或者地线包围。

4 面积、时序和功耗

TPSRAM32X32的版图面47um×63um,在TSMC40G的WC和WCL工艺拐角下频率可达到1.8GHz,时钟信号的最小脉冲宽度为200ps,在TSMC40G的TC和LT工艺拐角下时钟信号的最小脉冲宽度为130ps。

5 结论

在40nm工艺下,由于电源电压的降低,6T结构SRAM为了保证读操作的正确性,每一代工艺迁移晶体管尺寸的减小都有限,尤其是从45nm工艺迁移到32nm工艺,6T结构的下拉N管尺寸几乎没改变,所以面积也会大于8T结构。

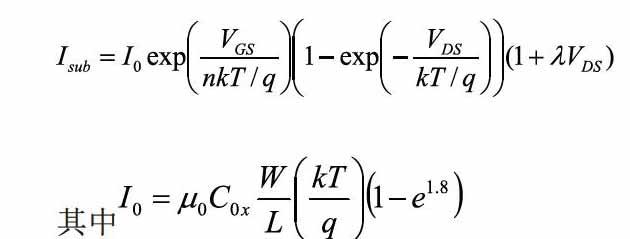

在功耗方面亚阈值漏电流的计算公式如下:

可知,亚阈值漏电流与尺寸大小关,在40nm下8T结构可以选用更小尺寸的下拉管接地,从而有效减少漏电流。

最终的数据结果比对可以查看表1、表2。

参考文献

[1]E.J.Marinisen,B.Prince,D.Ketel-Schulz,etal.Challenges in Embedded Memory Design and Test[C].Proceedings of Desgin.Automation and Test in Europe,2005:722-727.

[2]S.Kundu,etal.Test Challenges in Nanometer Technologies[J].J.ElectronicTesting:Theory and Applications,2001,17(3/4):209-218.

[3]賽普拉斯36-Mbit和18Mbit容量的四倍速和双倍速SRAM[EB/OL].

[4]Y.Morita et al.An Area-Conscious Low-Voltage-Oriented 8T-SRAM Design under DVS Environment[J].Digest of Tech.Papers,Symp.VLSI Circuits,2007:256-257.

[5]M.A.Turi,J.G.Delgado-Frias et al.High-Performance Low-Power SelectivPrecharge Schemes for Address Decoders[J].IEEE Transactions on Circuits and Systems,2008,55(9).

[6]K.Zhang et al.A 3-GHz 70-Mb SRAM in 65nm CMOS technology with integrated column-based dynamic power supply[J].EEE J.Solid-State Circuits,2006:146-151.

[7]C.T.Chuang,S.Mukhopadhyay,J.J.Kim,K.Kim.High-Performance SRAM in NanoscaleCMOS:Design Challenges and Techniques[J].EEE JSSCC,2007:4-12.

作者简介

唐骏(1990-),男。现为国防科学技术大学计算机学院硕士研究生在读。主要研究方向为集成电路设计。

作者单位

国防科学技术大学计算机学院 湖南省长沙市 410073