12位100MHz流水线型ADC行为级建模与仿真

王月海 刘红岩

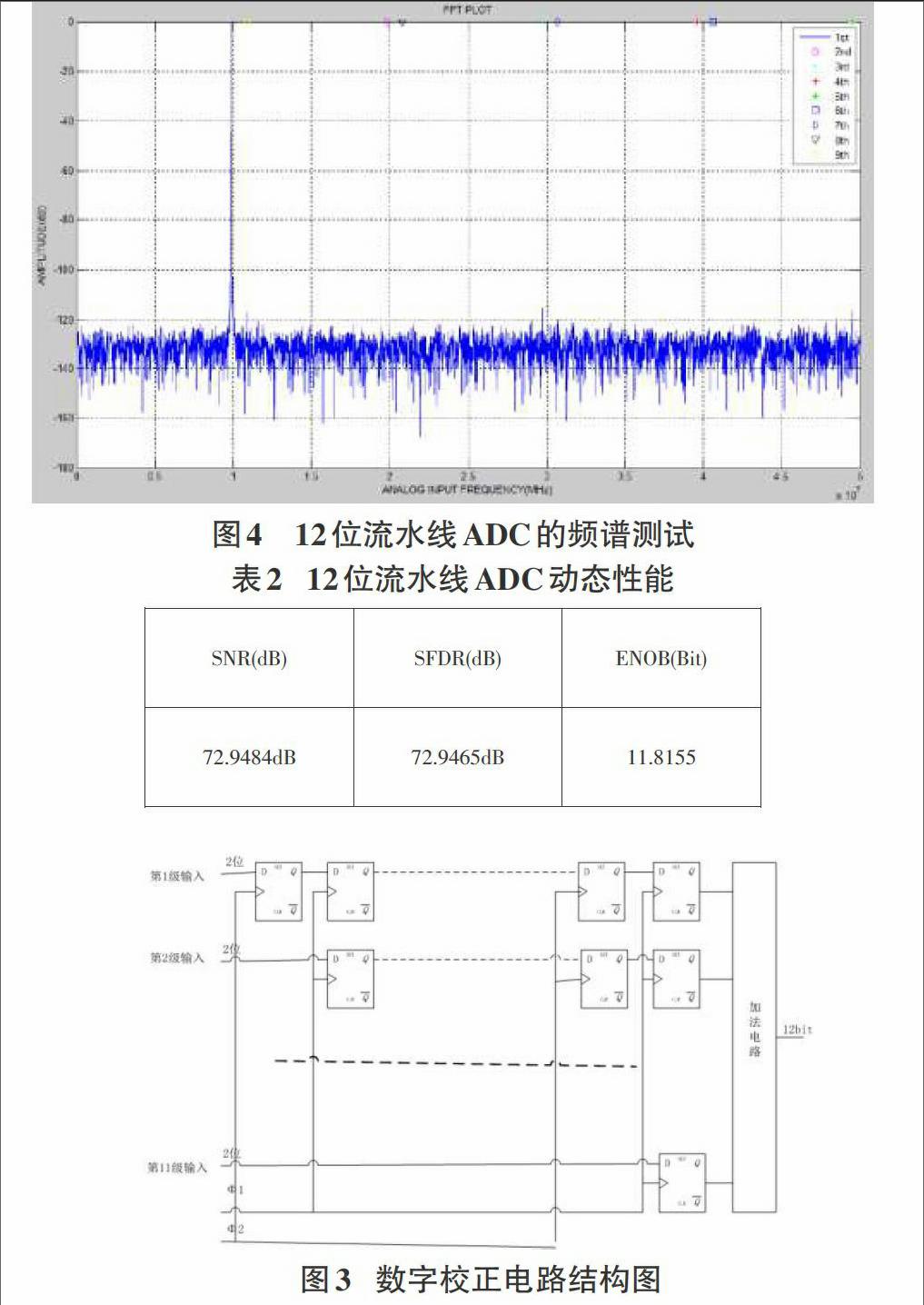

摘要:为了提高大规模集成电路的设计效率,该文通过Verilog-A对子ADC、MADC电路、数字校正电路等关键单元进行建模,最后得到12比特100MHZ的流水线型ADC模型,采用Cadence的Spectre仿真器进行仿真验证。通过仿真结果验证得到SNDR为72.9465dB,SNR为72.9484dB距离理想的12比特ADC模型的SNR只差1.0516dB,ENOD为11.8155距离理想的12比特ADC的ENOD只差0.1845, 以此验证了本文的ADC是高速有效的ADC模型。

关键词: Verilog-A;行为级建模;流水线型ADC

中图分类号:TP311 文献标识码:A 文章编号:1009-3044(2016)24-0236-03

行为级建模的方法有很多,Matlab/Simulink建模 [1],模型通用性和可移植性差。采用VHDL-AMS(VHDL Analog and Mixed-Signal Extensions)建模[2],但并没有创建出针对流水线的实际非理想因素进行特定的流水线结构ADC模型。利用Pspice和Simulink进行联合仿真[3],但是普通用户无法得知系统内部详细的电路结构和参数。

基于Verilog-A对多位每级流水线ADC做行为级建模,Verilog-A可以使用电路仿真工具Spectre仿真,而且可以精确描述模拟电路中的各种性能参数,Verilog-A主要通过基尔霍夫电流定律和基尔霍夫电压定律,描述输入输出信号之间的电路行为,verilog-A可以描述时钟抖动、运放增益等非理想因素。

本文通过Verilog-A对子ADC、MADC电路、数字校正电路等关键单元进行建模,最后得到12比特100MHZ的流水线型ADC模型,采用Cadence的Spectre仿真器进行仿真验证。通过仿真结果验证得到SNDR为72.9465dB,SNR为72.9484dB距离理想的12比特ADC模型的SNR只差1.0516dB,ENOD为11.8155距离理想的12比特ADC的ENOD只差0.1845, 以此验证了本文的ADC是高速有效的ADC模型。

1 ADC总体设计方案

本文的12比特流水线型ADC 采用1.5bit/stage的10级流水线,最后一级采用2bit闪存模数转换器,还有数字校正电路[4],流水线型ADC的核心是1.5bit/stage的流水线结构,每级的流水线包括一个MDAC(Multiplying Digital-to-Analog Converter)和子ADC,子ADC对采样信号进行模数变换得到1.5bit数字输出,MDAC的作用包括数模转换,减法器 和放大倍数为2的SHA(sample-hold amplifier),图1为流水线结构ADC结构框图。

工作原理如下,首先模拟信号第一级的SH(sample-hold),完成采样保持功能,采样信号送到本级的1.5bit子ADC和下一级MDAC,1.5bit子ADC得到1.5bit数字输出码,同时送到本级数字逻辑电路和下一级MDAC; MDAC中包含1.5bit子DAC,减法器和放大倍数为2的放大器,子DAC将第一级的1.5bit数字码变换得到模拟信号,再送入减法器和第一级的采样保持的输出信号相减,所得余量由放大器放大两倍作为下一级MDAC的输入信号,同样本级的SH采样信号送到本级的1.5bit子ADC和下级MDAC;第3-10级结构与第2级完全相同,第11级唯一不同的该级是一个2bit比较器,最后送到数字校正电路进行校正,得到12bit的数字输出。

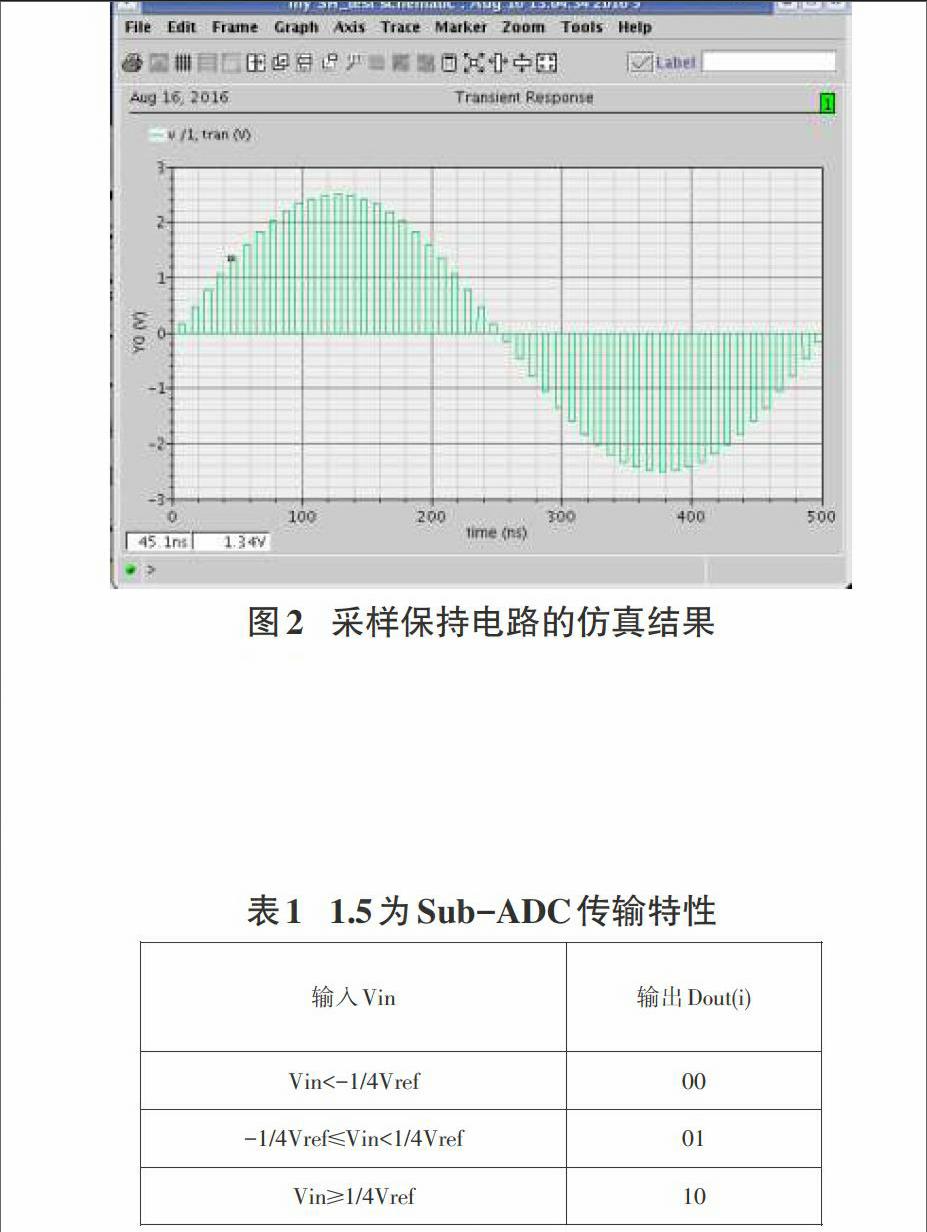

2 SH(Sample-Hold)的建模

SH电路是流水线ADC的重要组成部分,其作用是对输入的模拟信号进行采样,得到离散的模拟信号,供本级的子ADC对该信号进行模数转换得到数字码,因为子ADC对采样信号的转换需要时间,所以SH还需要对采样信号保持一段时间,所以SH电路的作用就是对模拟信号进行采样和保持。

3 Sub-ADC建模

子ADC对SH的采样信号进行模数转换,采用1.5bit子ADC的原因是:只需要两个比较器,可以降低功耗关于1.5位Sub-ADC的参考电压和输出码之间的关系见表1。

4 MDAC(Multiplying Digital-to-Analog Converter)建模

MDAC电路包括1.5bit子DAC、减法和级间增益三部分,1.5bit子DAC将前面的子ADC电路转换的数字码经过数模转换为模拟信号,经过减法器被上一级S/H的保持的模拟信号减去后得到的余量Vres(i),经过级间增益发达2倍后作为下一级的输入信号。

在采样阶段,根据Sub-DAC的输出实现减法的功能,在保持阶段,用余量放大器实现余量的放大,并作为下一级电路的输入。

5 Flash ADC的建模

Falsh ADC 作为代码产生电路的最后一级直接输出两位的数字代码。由三个比较器构成,他们的阈值电压分别是Vref/2,0,-Vref/2,三个阈值将区间分为四段,在-Vref到Vref之间对应的数字码输出依次是00,01,10,11。

6 数字校正电路的建模

流水线ADC相邻子级之间是串行工作的,相邻两级之间具有1/2个时钟周期的延迟,为了能够同步输出,12级的数字输出码经过延迟对准寄存器才能输出,D触发器可以实现寄存数据,因此延迟对准寄存器用D触发器实现,由于采用1.5bit/stage的结构,输出码字存在冗余,采用重叠相加的方式消除冗余,最后产生12位的输出码字。

7 仿真及验证

动态性能最能反映流水线ADC模型工作的性能状态[5], 其中主要包括信噪比SNR(Signal to Noise Ratio),信噪比是输入信号和噪声的功率比,是定义器件内部噪声大小的基本参数,SNR定义的详细描述如下所示:

8 结束语

基于Verilog-A对多位每级流水线ADC做行为级建模,Verilog-A可以使用电路仿真工具Spectre仿真,而且可以精确描述模拟电路中的各种性能参数,Verilog-A主要通过基尔霍夫电流定律和基尔霍夫电压定律,描述输入输出信号之间的电路行为,verilog-A可以描述时钟抖动、运放增益等非理想因素。

本文通过Verilog-A对子ADC、MADC电路、数字校正电路等关键单元进行建模,最后得到12比特100MHZ的流水线型ADC模型,采用Cadence的Spectre仿真器进行仿真验证。通过仿真结果验证得到SNDR为72.9465dB,SNR为72.9484dB距离理想的12比特ADC模型的SNR只差1.0516dB,ENOD为11.8155距离理想的12比特ADC的ENOD只差0.1845, 以此验证了本文的ADC是高速有效的ADC模型。

参考文献:

[1] Lan D,Liu X D.Behavioral model based on simulink for 14-bit 200MS/s pipelined ADC[C]//International Conference on Control Engineering and Communication Technology.Shenyang:IEEE,2012:79-82.

[2] 申振胜.基于VHDL-AMS的ADC建模及仿真[D].西安:西安电子科技大学,2014.