FPGA控制的反激式开关电源的设计

王磊++陈凤腾++高君楠

摘要:针对开关电源的特点和现有数字化控制方案,设计了一种以 FPGA为控制核心的反激式开关稳压电源。文中详细论述了该系统的硬件组成结构和实现方法,通过改变PWM脉冲宽度实现5-24V输出电压可调,具有按键设定、电压显示、过压过流保护等功能。以Altera公司的CycloneII系列芯片EP2C5T144C8N为主控芯片,采用Verilog硬件描述语言对PWM信号产生模块、数字PID模块、ADC接口逻辑等进行了设计,并在Modelsim仿真软件上完成了验证,证明了设计方法的可行性和正确性。

关键词:FPGA;反激式;PWM; PID;Verilog

中图分类号:TN86 文献标识码:A 文章编号:1009-3044(2016)26-0240-03

The Design of Flyback Switching Power Supply Using FPGA Controlled

WANG Lei, CHEN Feng-teng, GAO Jun-nan

(Department of Mechanical and Electrical Engineering,Xuzhou Institute of Technology, Xuzhou 221111, China)

Abstract: According to the characteristics and the existing digital control scheme of switch power supply, a flyback switch power supply with the FPGA as the control core was designed. The hardware structure and the realization method of the system was discussed in detail. Through changing the duty ratio of PWM pulse, it realized voltage range 5~24v;it also has many function such as setting keys, voltage display, over-voltage and over-current protection.The chip EP2C5T144C8N of the Cyclone II series that launched by Altera was the control chip. Verilog HDL language was used in the design of the PWM signal generating module, digital PID module and the ADC interface logic; and then, through simulating on Modelsim software, the correctness and feasibility of the design method was proved.

Key words: FPGA; flyback ; PWM; PID; Verilog

1 引言

变压器耦合反激式开关稳压电源,结构简单,省去了一个和变压器体积相当的大电感,同时变压器绕组间相互隔离,“热地”与“冷地”是绝缘的,其绝缘耐压强度很大,因而反激式电源在各种强调安全的中小功率电源中得到广泛的应用[1]。

常规的可调式开关稳压电源一般采用电位器结合专用的PWM调制芯片TL494、UC3842等,来实现输出电压的平缓调节。但是电位器的精度不高,在使用过程中又存在磨损、老化等问题就进一步导致控制精度的下降。数字电位器的出现虽然解决了机械磨损的问题,但受位数及分辨力限制,精度仍不能做到很高[1]。本文采用数控调压方式,由FPGA逻辑电路产生PWM波控制MOSFET管通断,进而改变输出电压的大小,通过闭环反馈对电压进行实时精确调整,较好的克服了传统可调式开关稳压电源的缺点。此外FPGA器件采用硬件描述语言设计,具有良好的并行处理能力,有效避免了单片机等微控制器运行时程序跑飞的发生,因此系统具有较好的抗干扰能力。

2 硬件电路设计

2.1 系统组成结构与方案

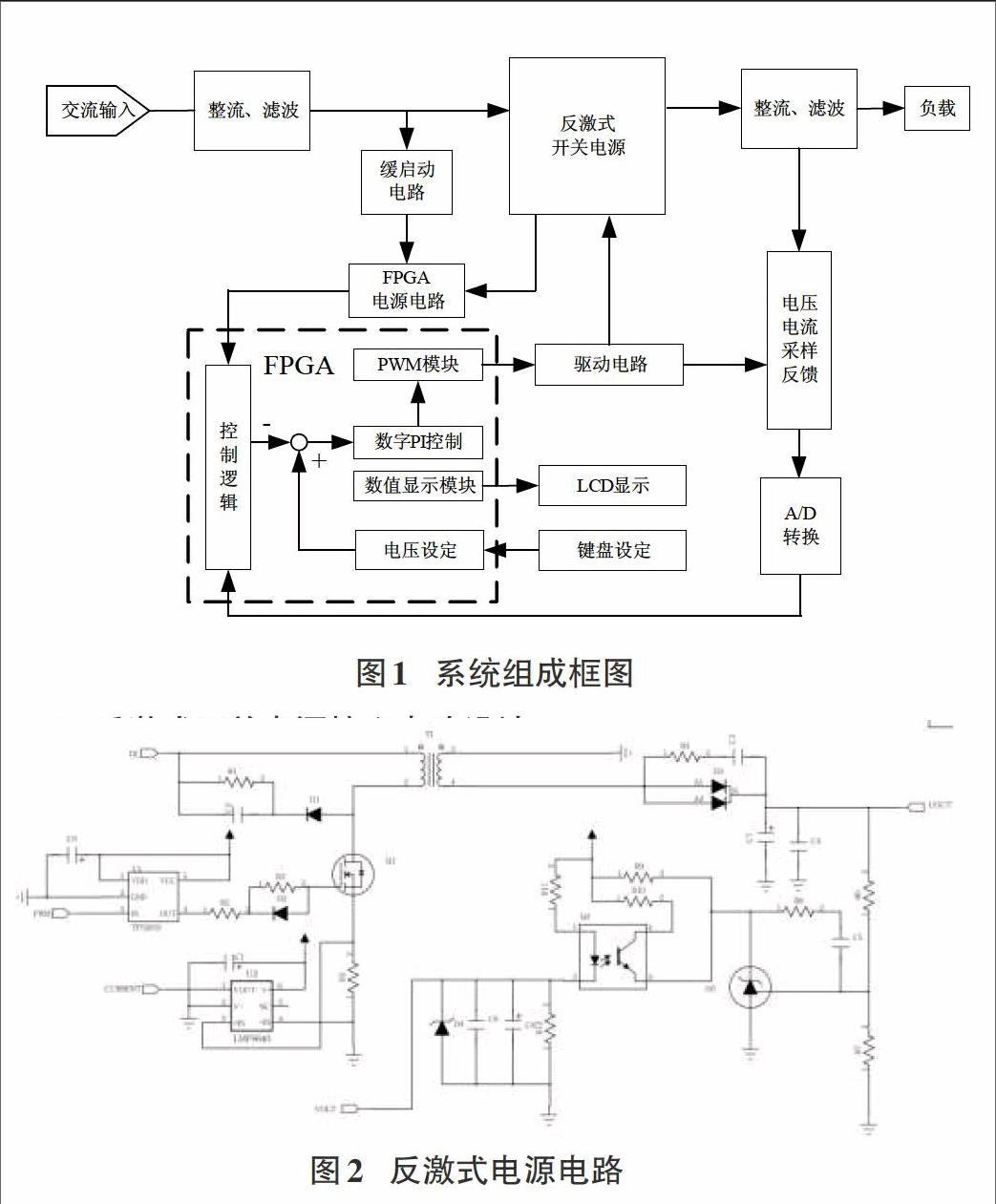

整个系统主要由反激式电源电路与逻辑控制电路两部分组成,其结构框图如图1所示。反激式开关电源的控制核心采用Altera公司的Cyclone II系列FPGA芯片EP2C5T144C8N,完成PWM信号产生、数字PI调节、SPI总线接口、按键输入与数值显示等控制功能。系统采用闭环设计,根据反馈电压的AD采样结果与设定值比较,得到偏差信号在数字PID控制器的作用下对自身PWM产生模块的占空比进行实时调节,经驱动芯片放大后控制开关管的通断,从而实现对输出电压的精确控制。系统的电压设定值由FPGA片外按键输入,AD采样结果一方面提供给误差分析模块,另一方面送给数值显示模块在LCD上进行实时显示。

2.2 反激式开关电源核心电路设计

核心电路中,为了提高MOSFET的驱动能力,和开关速率,PWM模块的输出信号经过TPS2819芯片后驱动MOSFET管工作[2]。TPS2819为TI公司单路高速MOSFET 驱动器芯片[6],与分立元件驱动电路相比可进一步提高电路的开关速率和可靠性。核心电路如图2所示,在CCM模式下[3,4],其电压变比为D/[N(1-D)]。当Q1关断时磁场储能在T1次级感应出4正3负的感应电压使二极管导通,为C7充电。但由于T1漏感的存在,Q1关断瞬间漏感电流不能突变,此时会产生很高的感应电压。当输入电压为30V时,UDS的尖峰电压可达265V,该电压有可能超过Q1的耐压值。因此在T1的一次绕组增加由R1、D1、C2组成的RCD电路[3],吸收漏感电流抑制感应电压。

2.3 电流电压采样电路设计

电流检测电路采用TI公司的高速、电压输出电流感测放大器芯片LMP8640,将监控电阻R3上的电流IS的变化转换成电压信号输出到模数ADC采样[7],当增益为20V/V时输出电压和监测电流的关系为:VOUT=40R3*IS。当电流超标时,FPGA将控制内部PWM模块调整占空比,防止MOS管电流过大[5]。Q2、D5(TL431)、R6、R7构成电压反馈电路,输出电压经过光电耦合形成闭环回路,同样在ADC采样后反馈给FPGA。ADC采样电路如图3所示,AD7887是低功耗12位模数转换器,支持两路信号输入,可通过对片上控制寄存器设置使其工作在双通道或者单通道模式,本系统需要采集反馈电压和开关管电流两个模拟信号,因此需要把AD7887设定在双路输入模式。CURRENT为LMP8640输出的电流采样结果,VOLT为光耦输出的电压采样信号,管脚6~8接FPGA的SPI总线控制逻辑。

3 FPGA设计与仿真

本文的内部电路设计采用Verilog硬件描述语言编写,主要包括ADC芯片接口逻辑、PWM脉冲生成模块、按键检测模块[5]、占空比PID控制模块。其控制过程如图4所示,FPGA上电配置完成后,各模块就绪并通过内部信号联络。没有按键设定时FPGA输出默认占空比脉冲,同时采样ADC结果,数据处理后驱动LCD显示。当有按键输入时,内部控制逻辑将根据该设置值调整脉宽大小,该值不是固定的是通过PID控制算法,根据偏差量实时调节的。如果电流值超标,PWM模块将立即调整占空比使电压输出降至最小默认值。

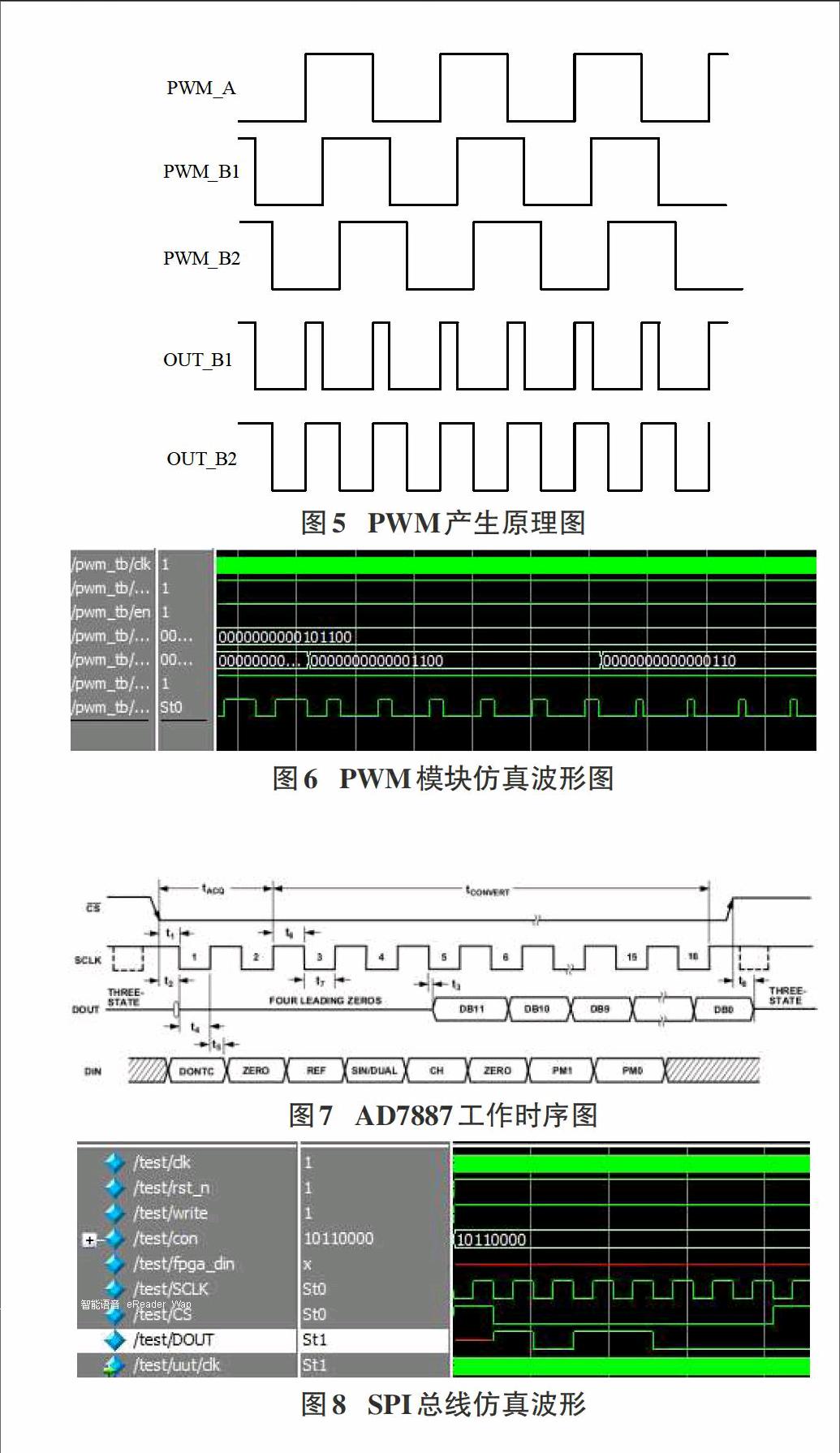

3.1 PWM脉冲产生

PWM信号的产生方式有很多,本设计采用移相法实现。同步PWM信号和相移后的信号进行异或运算实现占空比0~1之间可调。其原理如图5所示,PWM_A为同步信号,PWM_B1、PWM_B1为不同相位下移相后的信号,可以看到在图5中,OUT_B1为同步信号和PWM_B1异或后的结果占空比为25%;OUT_B2为同步信号和PWM_B2异或后的结果占空比为50%。PWM_Bn信号的延迟相位由FPGA中的延迟网络产生,延迟参数受到数字PID模块的输出结果控制。图6为PWM产生模块的Modelsim仿真波形,在图中可以清楚的看到输出波形的脉宽变化。

3.2 采集时序设计

AD7887芯片的控制信号有

图7 AD7887工作时序图

图8 SPI总线仿真波形

3.3 数字PI算法设计

PID控制算法因其具有算法简单、鲁棒性好、可靠性高等特点目前得到了广泛应用。本文将该算法应用在对PWM占空比的控制中,以改善占空比调节的响应速度和控制精度。PID控制算法的时域模型为[10]:

[u(t)=KP[e(t)+1Ti0te(τ)dt+Tdde(t)dt]] (1)

其中:

[u(k)=KP{TSTij=0ke(j)+TdTS[e(k)-e(k-1)]}] (2)

将(2)式中两次采样结果作差,得到数字PID增量控制式:

[Δu(k)=Kp[e(k)-e(k-1)]+Kie(k)+Kd[e(k)-2e(k-1)+e(k-2)]] (3)

进一步整理得到:

[u(k)=u(k-1)+(Kp+Ki+Kd)e(k)+[-(Kp+2Kd)]e(k-1)+Kde(k-2)] (4)

(4)式和(2)式相比没有了求和项,在实现上更加简单,FPGA并行实现结构如图9所示。

该并行结构的实现采用Verilog硬件描述语言设计,其仿真波形如图10所示。由于FPGA的高速并行运算和硬件支持,使其控制性能比汇编或C语言实现的效果要好,并且系统的稳定性也得到了进一步的提升。

4 结论

开关稳压电源目前已成为电源发展的主流方向,在航空航天、电子通讯等领域得到了广泛的应用[10]。本文采用FPGA芯片EP2C5T144C8N做数字控制核心,MOS管驱动、电流采样等模块均采用集成电路以提高设计的可靠性。在PWM产生部分引入数字PID算法实现对反激式开关稳压电源的闭环控制具有反应速度快、电压调节方便、稳定性好等优点。该电源系统具有较好的抗干扰能力和较高的精度,并且FPGA程序升级维护方便,稳定性方面与单片机等控制器相比具有明显优势也便于实现自动化控制。

参考文献:

[1](美)RaymondA.Mack,Jr著.开关电源入门[M].谢运祥,译.北京:人民邮电出版社,2007.

[2] 刘雪,赵柏树,杨维明.单片机控制的精密可调开关稳压电源设计[J].电源技术,2014.3(38):535-537.

[3] 王晓雷,昊必瑞,蒋群. 基于MSP430单片机的开关稳压电源设计[J].现代电子技术,2008.12(3):186-188.

[4] 郭键,朱杰,董萍萍.一种基于MSP430单片机的开关电源设计[J].电子设计工程,2012,20(19):134-138.

[5] 李跃. 反激式开关电源箝位电路优化设计[D].中南大学,2013.

[6] http://www.ti.com.cn/cn/lit/ds/symlink/tps2818.pdf

[7] http://www.ti.com.cn/cn/lit/ds/symlink/lmp8640.pdf

[8] http://www.analog.com/cn/products/analog-to-digital-converters/ad-converters/ad7887.html

[9] 乔庐峰. VerilogHDL数字系统设计与验证[M].北京:电子工业出版社,2009.

[10] 李垂君.基于FPGA的PID控制器研究与实现[D].大连理工大学,2007.