基于FPGA与ARM的智能合并单元设计

郭艳平

近年来,随着社会经济的快速发展和科学技术的日益进步,智能电网在一定程度上已经成为电力系统发展的主要方向,普遍受到世界各国的关注与研究,其所涵盖的工程领域众多,如变电、输电以及配电等。同时,智能变电站作为智能电网必不可少的组成部分,利用智能化设备有助于实现全站信息的数字化、通信网络平台的网络化以及信息共享的标准化。然而,基于FPGA与ARM的智能合并单元在一定程度上可以为智能变电站的实现提供坚实的基础。

【关键词】FPGA ARM 智能合并 单元设计

1 智能合并单元的意义

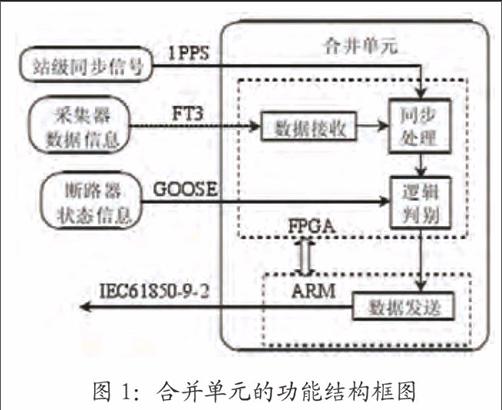

所谓的合并单元在2002年所颁布的IEC标准中最早将其定义为能够对二次转换器的电流或者电压利用时间能够同时进行转换的一种物理单元,其在一定程度上是电子式互感器中的一个重要组件,并且还是一个相对独立的单元,对其输入的通道、编码的方式等都能够利用通信對点的方式进行准确而又详细的描述。本文基于FPGA与ARM进行了智能合并单元设计,功能具体的原理如图1所示,智能化合并单元设计较之前相比具有非常显著的意义。

(1)在进行太网接口的过程中能够充分利用和发挥ARM本身对处理数据的能力,在一定程度上有助于操作的简化,同时FPGA的I/O异常丰富,能够使得并行处理的速度显著加快,基于FPGA与ARM本身的功能可以极大的满足合并单元的多种需求,如同时处理多个任务、实时性和可靠性等。

(2)ARM作为主处理器能够有效的延时补偿、标定、发送采样的信息,并且还能够实现对FPGA的配置;而FPGA作为辅处理器能够实现对数据的同步接收以及逻辑上的判断,通过双口RAM的利用可以直接向ARM提供一定的采样值等各方面的数据信息。

2 数据接收模块设计

所谓的数据接收模块主要通过采集器所发出的多路异步串行数据在经过冗余循环的有效性校验之后,按照先后顺序将数据并行发送到后续模块中。鉴于IEC 61850对于采集器和合并单元之间的通信数据进一步做出明确的规定,因此为保证电子式互感器闭锁告警供功能的正常启动,便可以在通信数据在电流和电压数字量进行串行传输的过程中将一次设备的状态量添加进去。同时,由于数据传输在不同通道内保持着一定的相对独立性,所到达合并单元的先后关系是不固定的,而利用FPGA不仅有助于同时接收和校验多路数据,并且还能凭借其本身的FIFO功能对多路数据进行正确的排序。此外,在排序数据的过程中还可以将最大等待的时间设置下来,若某路的数据不能正常的传输到目的地时,便可以通过FIFO将该路数据借助状态信息位将故障告知二次设备。

3 数据处理模块设计

3.1 同步模块的处理

同步处理在一定程度上可以将对多路电量的模拟与采样时刻同步,具体的包括不同采集器和合并单元之间的同步,从而有助于二次设备供给电流和电压在时序上能够保持一致性。不同采集器之间的同步是借助站级内的同步信号进行相应的插值算法,有助于不同采集器在相同时刻进行数据的采样,若一旦发生站级同步信号失效的情,FPGA内的晶振分频便会立即启动相应的还会产生一定的采脉冲,并且还能将报警信号及时的发送至二次设备。不同合并单元之间的同步是在进行延时测算的基础上将不同合并单元内的采集时刻归算到实际时刻,其所输出的采样值的模拟报文中的时间标签信息实际上就已经为同一合并单元SAV输出的同步性,因此不同SAV实际采样时刻可以利用当前的时刻减去不同合并单元的固有延时。

3.2 逻辑判别模块

无论是单母分段还是双母线,就接线方式而言每段母线的并行既可以是并列也可以是分列,不同母线之前的出线在一定程度上可以为负荷的不间断供电提供重要的保障。逻辑判别模式在一定程度上可以借助相关逻辑判别的机制软件并列和切换母线的电压。同时合并单元通过总的过程线经相关断路器和刀闸等方面的状态信息,根据事先就已经设置好的机制软件并列或者切换电压,对母线电子式电压互感器进行科学的选择,从而有助于将一定的电压传送至智能化电子设备当中,如保护、测控以及计量等,并且在故障发生时还可以将相关的告警信息及时的发送出去。

4 数据发送模块设计

数据发送模块主要对定前端已经处理好的信息进行负责,在此基础上按照相关的标准对通信进行约束,然后利用太网实时的将已经组帧好的数据单元发布出去。IEC 61850-9-2对串行链接上的采样值进行了科学的规范,使其能够支持ACSI的一系列服务,如传输采样值的报文,控制采样值的块读和块写。一方面,同采样值报文的传输可以在一定的标准约束下对相关的数据链接层进行科学的映射;另一方面,控制采样值的块读和块写可以及时有效的控制采样值的传输属性,如数据集、采样的频率和使能,从而可以最大限度的对采样值的传输模块进行灵活的配置。本文通过采用一种事前就已经配置好的采样值控制模块,进而有助于灵活的采样值传输模型的相关映射方案进行灵活的定义,并且根据工程的实际需要完成了对采样值数据集的提前配置,灵活的配置工程的实际间隔,在一定程度上极大的避免了MMS在映射时所面临的各种困难。

5 总结

综上所述,本文通过对智能合并单元意义的简单介绍,从数据接收模块设计、数据处理模块设计、数据发送模块设计等方面对基于FPGA与ARM的智能合并单元设计进行了系统化的分析,从而一定程度上为智能变电站的实现提供了坚实的基础。

参考文献

[1]朱利鹏,彭晓涛,杨军.多ARM协同架构的智能合并单元设计[J].中国电力,2015(01):146-152.

[2]何小庆.基于FPGA的数字化牵引变电所合并单元研究与设计[D].成都:西南交通大学,2014.

作者单位

南京航空航天大学金城学院自动化系 江苏省南京市 211156