基于FPGA的多路隔离信号存储系统设计

倪震明

摘 要:文中设计了以FPGA为控制核心,以Flash K9WBG08U1M为存储介质的存储系统。系统上电工作后开始接收PCM码流,并在起飞信号唤醒后接收3路隔离模拟量,数据存储完成后,通过RS 422将存储数据回读进行分析。文中介绍了系统整体组成、各模块功能设计和系统逻辑设计。测试结果表明,该存储系统存储数据可靠稳定,满足任务要求。

关键词:FPGA;信号存储;Flash;RS 422

中图分类号:TN431.2;TP39 文献标识码:A 文章编号:2095-1302(2017)05-00-03

0 引 言

在航天测控系统中,遥测参数的测试对于验证飞行器的设计参数、判断试验中的故障等具有重要意义[1]。本文研制的采集存储系统作为遥测系统的组成部分,用于实时存储飞行器在飞行中的动态参数。存储系统以FPGA作为控制核心,以Flash作为数据的存储介质,以接收到起飞信号作为启动模拟量数据采集的起点,实现1路5 Mb/s的PCM码流和3路模拟量的接收。试验完成后,将存储数据回读,对其进行分析和回放,以验证接收的数据是否正确、完整。

1 存储系统组成

存储系统组成框图如图1所示。主控单元FPGA上电进行初始化后,等待并解析RS 422接收器接收的命令,当接收到启动记录命令时,开始接收PCM码流,直到存储系统被断电。当判断接收的起飞信号有效时,采集并存储3.2 s模拟量。其中,3路模拟量之间要求互相隔离,模拟量与PCM码流也互相隔离。记录完成后,通过RS 422发送器将接收的数据传至地面设备进行事后分析。

2 系统各模块设计

2.1 RS 422接口电路

存储系统的RS 422接口电路包括PCM码流接收电路、与地面设备通信时命令接收和数据发送电路。RS 422接口在传输数据时使用双绞线传输。

RS 422命令接收模块和数据发送模块采用异步串行方式,包括1位起始位、8位数据位、1位校验位和1位停止位。存储系统在接收命令时,先判断起始位,当起始位有效时开始接收8位数据,接收完8位数据后进行校验,校验为有效数据时才对其解析,执行相应命令。

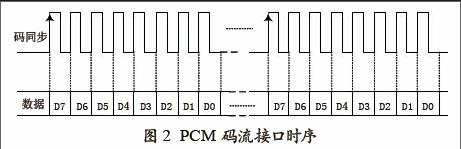

根据要求,存储系统需要接收1路5 Mb/s的PCM数字量。按照发送端接口要求,硬件采用DS26C32作为RS 422接口芯片。PCM码流接口时序如图2所示。接收数据时以码同步信号作为同步信号。为保证数据传输的可靠性,发送端在码同步上升沿发送数据,存储系统在码同步下降沿接收数据,每个码同步时钟接收1位数据,每个字节按照先高位后低位的顺序依次接收。FPGA对PCM码流解码时,先将串行接收的数据转为并行数据,并对接收的并行数据进行实时判断,当判断到连续两个字节为主帧帧标志EB90或副帧标志146F后,开始接收后面完整的字节。

2.2 起飞信号接收

存储系统采用高速数字光耦HCPL-5531接收起飞信号。起飞信号的正确接收能够确保模拟量正常启动采集。为防止起飞信号误触发,FPGA在接收起飞信号时,会进行4 ms的宽度判别[2],当起飞信号变成高电平后开始计时,计时4 ms,只有起飞信号保持高电平不变,才会认为起飞信号有效。

2.3 模拟量采集

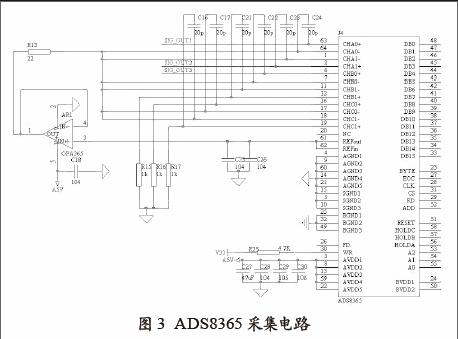

存储系统需要采集的模拟量信号最高频率为6 kHz,在设计时,将各通道模拟量采样率设置为40 kHz,以保证采样后的数字信号可以完整保留原始信号中的信息。0~5 V的输入模拟量信号通过隔离电路后进入由OPA4340搭建的电压跟随电路,以避免后续电路对信号处理时由于信号的输出阻抗过高引起损耗[3]。经调理后的模拟量由FPGA控制ADS8365采集,ADS8365是TI公司生产的高速、低功耗、6通道同步采样的高性能A/D转换器,其最高采样率为250 kHz[4]。ADS8365采集電路如图3所示。

由于只需要采集3路模拟量,FPGA控制ADS8365进行时,分别给、和一个低脉冲,ADS8365启动转换,转换完成后,设置信号为低电平,在信号的上升沿从并行接口以循环模式将数据读回。对于采集的模拟量,采用编码方式将循环一次采集的3路模拟量作为一个数据块,后面加上2字节帧计数和2字节帧标志(DAAD)进行存储。模拟量帧格式如图4所示。在后期分离和分析数据时,可以很方便地根据帧结构提取出各通道模拟量数据。

2.4 隔离电路设计

根据任务要求,为避免信号之间的相互干扰,需要将数字量和模拟量互相隔离,将各模拟量之间彼此隔离。存储系统在设计时,采用信号全隔离的思想进行电源隔离和信号隔离。设计模拟量电路和数字量电路时,电源不供地,分别对模拟量和数字量设计供电电源,以避免数模共地带来的干扰影响到传输质量。而对于3路模拟量之间的隔离,选用ISO122P隔离放大器作为模拟信号隔离芯片,模拟量隔离电路如图5所示。为保证模拟量的彻底隔离,对输入信号供电与输出信号供电、输入信号地与输出信号地也进行隔离,以保证各信号之间互不影响,同时避免某路信号发生传输故障时,对硬件其他电路造成不良影响。

2.5 Flash存储模块

存储系统存储1路5 Mb/s的PCM码流,若其速率为5/8MB/s=0.625 MB/s,记录时间为3 900 s,由此计算出PCM码流存储需要的容量为2 437.5 MB。采集3路模拟量,每路采样率为40 kHz,每次采样存储字节数为10B,存储时间为3.2 s,由此,模拟量存储所需容量为40kHz×10B×3.2s=1.25MB。固存系统所需总容量为2 437.5 MB+1.25 MB=2 438.75 MB。选用三星公司容量为4 GB的NAND型Flash K9WBG08U1M作为存储介质。从以上计算可以看出,系统数据存储总速率比较慢,Flash采用普通写入方式即可满足存储系统写入速率要求。

3 系统逻辑设计与功能实现

存储系统选用Xilinx公司Spartan-2系列的XC2S200 FPGA作为控制单元,用以实现系统的功能。采用模块化设计原则,不仅可以降低逻辑设计难度,还可以方便整体功能的调试。FPGA设计系统框图如图6所示。

存储系统的工作模式分为擦除模式、记录模式和回读模式。系统上电完成系统复位后,FPGA控制接收异步串行命令。当判断到异步串行数据起始位为低电平时,接收后面8位数据,接收完成后对照校验位判断数据是否有效,若数据有效,则对数据进行实时解析。

当解析当前指令为擦除指令时,对Flash进行擦除操作。擦除操作按块进行[5],在Flash的数据端口先写入擦除标志60 h,再写入块地址,最后写入擦除命令D0h,即可擦除该块。擦除成功后,块地址递增并循环上述操作,即可完成对整个Flash的擦除。若擦除失败,则向块中写入无效块标志。所有块擦除后,返回进行指令判断。

当解析当前指令为记录指令时,存储系统接收数据并且由FPGA控制Flash进行写操作。FPGA在时钟作用下判断码同步下降沿,在每个下降沿接收1位数据,连续接收16位数据组成2个完整的字节,实时判断这2个字节,当这两个字节为主帧标志EB90或副帧标志146F时,才将后面接收的数据存储。同时,实时判断起飞信号,当起飞信号有效时,開始采集模拟量。将外部参考时钟分频得到3 M时钟作为ADS8365的参考时钟,FPGA控制将、和拉低以启动转换,约5.5 μs后,转换完成,FPGA控制和信号将3路数据读取并进行编码。接收的数字量和模拟量采用混合编帧方式写入Flash。对Flash进行写操作时,先判断当前块是否为有效块,若当前块为无效块,则跳过该块,若当前块为有效块,则按页写入4 K数据后进行页编程,循环写并编程的过程直到写完64页才算完成了一块数据的写入,循环上述过程,直至存储系统被断电。

当解析当前指令为回读指令时,FPGA控制Flash进行读数操作。读取数据时先判断当前块是否为有效块,若为无效块则跳过该块,若为有效块,则按页将数据读出,采用异步串行的方法按照1位起始位、8位数据位、1位校验位和1位停止位的顺序,将读出的数据按字节发送至地面设备进行处理。

4 存储系统测试结果

在完成存储系统的硬件功能和软件功能调试后,对其进行综合性测试。由外部信号源发送PCM码流、直流量和起飞信号,存储系统接收信号并存储。完成测试后利用分析软件对原始数据进行解包,拆分出模拟量数据和数字量数据。

图7所示为拆分后的模拟量数据。前6列中,每两列代表1路数据,按照第1路到第3路的顺序。第7、8列为帧计数,从图中可以看出,帧计数连续递增,最后两列DAAD是帧标志。可以看出,采集结果与设计值完全一致。图8所示为模拟量第1路数据绘图,其中信号源第1路模拟量发送的是1 V直流量,图7的x轴表示采集的时间,y轴表示采集的电压,可见采集的时间符合设计值,采集的电压值与实际发送电压值相同。

图9所示为PCM码流接收片段。最后两列为数据中的主帧标志EB90,将数据与信号源发送的PCM码流对比可知,存储系统接收的PCM数字量帧结构正确,通过分析软件分析,接收PCM数字量过程中没有出现丢数或误码的情况。

5 结 语

根据全信号隔离数据采集的思想要求,设计了基于FPGA的数据存储系统,可以接收1路PCM数字量和3路模拟量,数字量与模拟量之间互相隔离,3路模拟量之间也互相隔离。该存储系统已成功应用于某飞行试验,通过各项试验验证,存储系统性能稳定可靠,各项指标满足任务要求。

参考文献

[1]郑永秋.某飞行器遥测数据记录器的优化设计[D].太原:中北大学,2012.

[2]丁海飞.基于双平面技术的固态存储器的设计与实现[D].太原:中北大学,2012.

[3]塞尔吉欧.弗朗哥.基于运算放大器和模拟集成电路的电路设计[M].西安:西安交通大学出版社,2009.

[4] The Datasheet of ADS8365[Z].

[5] The Datasheet of K9WBG08U1M[Z].

[6]朱海平,任坤.基于FPGA的双极化信号的采集板设计[J].物联网技术,2016,6(11):51-53.

[7]唐文龙,田茂,吴志强,等.基于SoC FPGA异步通信接口的实现[J].物联网技术,2015,5(12):38-39.

[8]刘欣,翟成瑞,张会新.多路隔离信号采集存储系统设计[J].自动化仪表,2014(8):27-30.