一种新型消除失调电压的高速高精度比较器

郭潘杰

一种新型消除失调电压的高速高精度比较器

郭潘杰

(中国空空导弹研究院,河南 洛阳 471000)

本文提出一种新型消除失调电压的高速高精度CMOS比较器。该比较器克服传统消除失调技术在信号通路引入电容的缺陷,具有更快的速度。设计的比较器采用TSMC 0.35μm 2P4M工艺。采用CADENCE软件SPECTRE仿真器仿真,该比较器在64MHz的时钟频率下,失调电压减小了92.6%,其延时时间仅为2.68ns,最小分辨率为33μV。

比较器;前置放大器;消除失调技术

1 介绍

在现代通信和信息处理系统中,高性能A/D转换器作为连接模拟和数字世界的重要通道被广泛应用于医学图像、高速数据变换等重要设计领域。比较器是模数转换器的核心单元,其精度、速度、失调电压和回馈噪声等因素直接影响系统模块的整体性能。

在比较器的设计中,为了满足整个电路精度和速度的要求,往往采用前置放大器和锁存器组合的方式[1]。由于失调电压的影响,比较器的精度受到限制,因此需要采用失调消除技术。

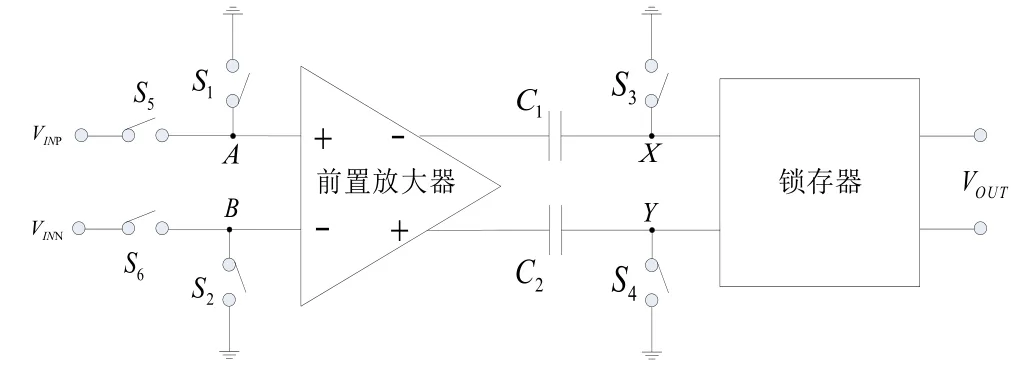

传统的比较器消除失调技术如图1所示[2],在前置放大器和锁存器之间,加入了输出失调存储电路。该方案在信号通路上引入了存储电容C1和C2,使前置放大器的主极点频率降低、带宽变窄,从而降低了比较器的动作速度。

本文在该结构上进行了修改,提出一种新型失调电压消除方案。本方案达到了既可消除失调电压又可避免在信号通路中引入电容的目的。本文提出的新型消除失调比较器电路具有高速、高精度的特点,可应用于高速高精度比较器和模数转换器电路中。

2 电路结构及原理

本文采用的失调消除技术,是以输出失调存储技术为主,在此基础上进行改进。如图2所示,比较器主体是由前置放大器和锁存器两部分组成。前置放大器包括两级全差分放大器。改进的地方在于前置放大器的第一级失调存储电容。

整个比较器等效输入失调电压为:

其中,VOS是整个比较器的失调电压,VOS1是第一级前置放大器的失调电压,VOS2是第二级前置放大器的失调电压,VOS3是锁存器的失调电压,AV1是第一级前置放大器的增益,AV2是第二级前置放大器的增益。通过整个比较器等效输入失调电压的表达式可以清晰看出,前置放大器中第一级是整个比较器设计的重点,降低VOS1是降低整个比较器失调电压的关键,其决定了整个比较器的失调电压。

图1 现有技术消除失调电压的比较器电路

图2 改进的消除失调电压比较器

接下来,重点介绍改进的前置放大器第一级电路。如图2所示,两个NMOS管MN1和MN2作为差分输入对管;两个PMOS管MP1和MP2作为负载,电容C1和C2作为失调存储电容,NMOS管MN0作为尾电流源。

其工作时序分为失调电压存储阶段和信号放大阶段。在失调电压存储阶段,开关S1和S2以及S3和S4闭合,差分输入对管MN1和MN2的栅极均接到共模电平VCM上,此时MP1和MP2以二极管连接的形式作为差分输入对管MN1和MN2的负载,因此正、负输出端的失调电压被分别存储到电容C2和C1上。在信号放大阶段,S1和S2以及S3和S4断开,差分输入对管MN1和MN2的栅极分别输入差分信号VINP和VINN,负载管MP1和MP2由电容C1和C2提供偏置电压,该偏置电压中包含前面存储的输出失调电压。

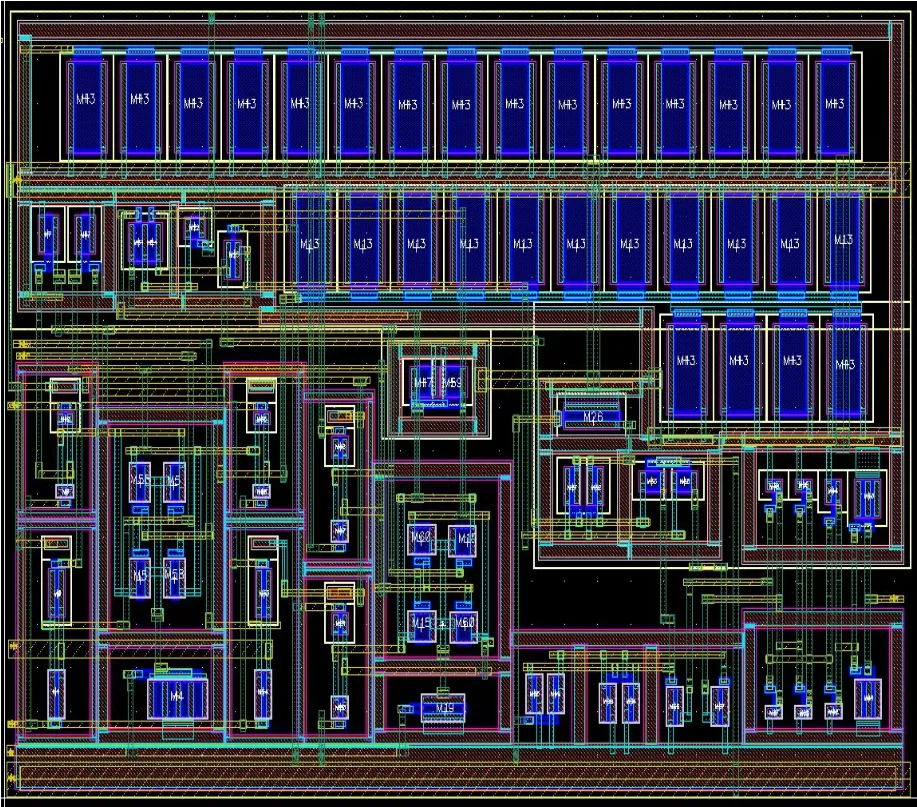

第一级前置放大器是差分对称结构,所以可分析单边情况。图3所示为单边失调电压存储阶段的失调电压等效模型。假设差分输入对管MN1的输入失调电压为VOSI,则其输出端VON的失调电压VOSO可表示为:

该输出失调电压被存储在电容C1上。

图4为信号放大阶段的单边失调电压等效模型。差分输入对管MN1的输入失调电压依然为VOSI,负载管MP1的栅极和地之间的输入信号为存储在电容上的失调电压VOSO,它们共同作用产生输出端的失调电压,因此可采用叠加原理对输出端VON的失调电压进行分析计算。

图3 失调电压存储阶段的等效模型

图4 信号放大比较阶段的等效模型

首先考虑输入失调电压VOSI单独作用时产生的输出失调电压,此时负载管MP1作为MN1的电流源负载(电容C1为其提供直流偏置电压,使其工作在饱和区),故VOSI单独作用时产生的输出失调电压VON1可表示为:

其次考虑MP1的栅极和地之间存储的失调电压VOSO单独作用时产生的输出失调电压,此时MP1作为放大管,MN1作为MP1的电流源负载(输入共模电压VCM保证MN1工作在饱和区),故VOSO单独作用时产生的输出失调电压VON2可表示为:

最后,可以根据叠加原理求出输出端的总失调电压VON为:

由(5)式可知,输出端的总失调电压为0,达到消除第一级失调电压的目的。存储电容不出现在信号放大阶段的信号通路上,对前置放大器的输出端极点和带宽不产生任何影响。

3 版图及仿真结果

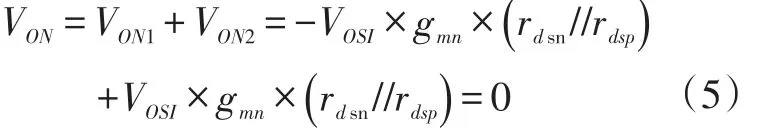

图5为整个比较器的版图。比较器的尺寸为136.3μm×89.8μm。

图5 改进的消除失调电压比较器版图

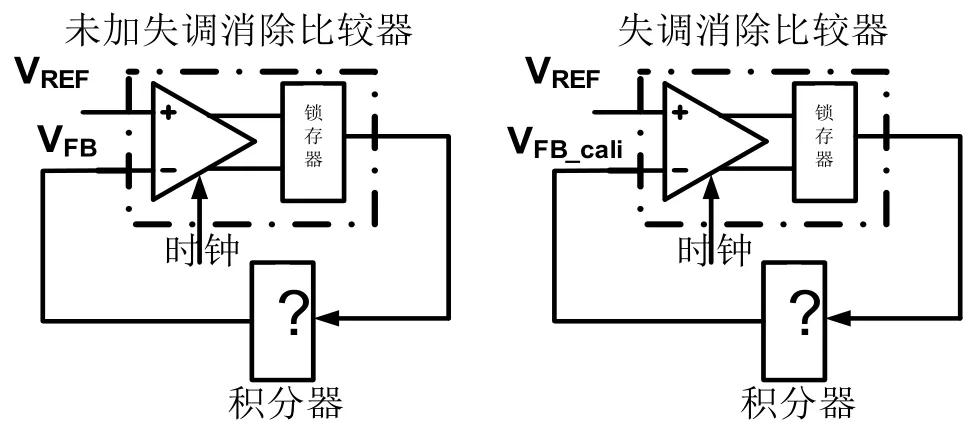

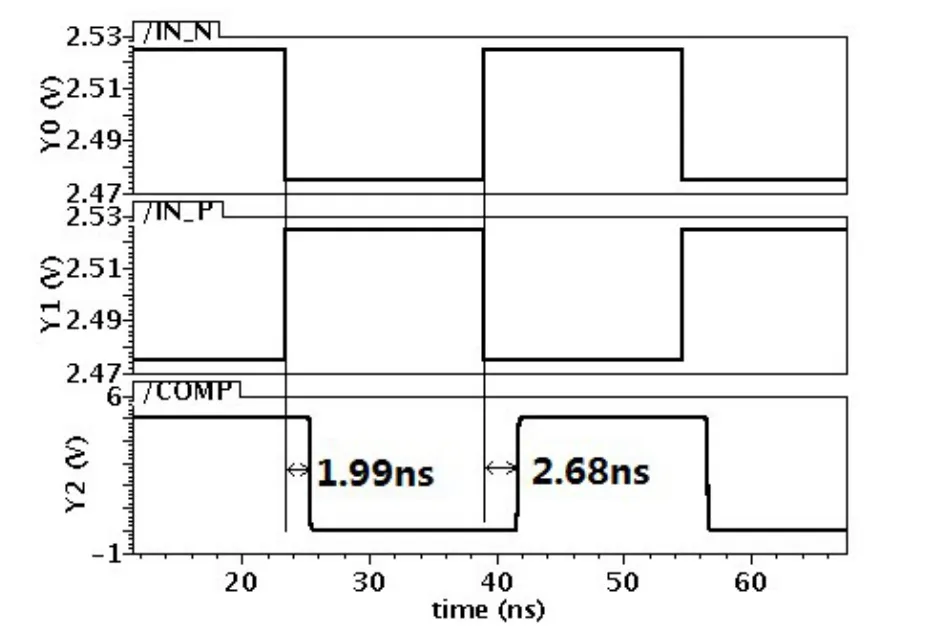

电路仿真采用CANDECE-EDA工具的SPECTRE仿真器,基于TSMC 0.35μmCMOS工艺模型,时钟频率是64MHz,电源电压为5V。比较器失调的测试方法如图6所示[3],在消除失调比较器和未消除失调比较器的负输入端均加入一个10mV的输入失调电压,通过积分器提高VFB和VFB_cali的电压值,最终得到比较器的失调电压。仿真结果表明:加入失调消除后,比较器的输入失调电压为740μV,减小了92.6%。图7和图8分别是比较器的传输延时测试结果和最小分辨率的测试结果,由图可知当差分信号变化1mV(1LSB)时,比较器的延时仅为2.68ns,比较器的最小分辨率可达33μV。

4 结论

本文提出了一种改进型CMOS消除失调比较器电路。该电路将失调存储电容加在前置放大器负载管的栅极-源极之间,而在信号比较阶段不引入该失调储存电容,因此不影响比较器整体的速度。本文提出的改进型消除失调放大器与传统的消除失调比较器相比,具有延时小、速度快的特点,故可应用于高速高精度比较器电路中。该电路已成功应用于一款12位逐次逼近型模数转换器中。

图6 比较器失调测试方法

图7 比较器传输延时测试结果

图8 比较器分辨率测试结果

[1]杨文荣,王加东.流水线ADC中高速比较器的设计和分析[J].微计算机信息(嵌入式与SOC),2007(14):271-272,298.

[2]Behzad Razavi.Principles of Data Convention System Design[M].New York:IEEE Press,1995.

[3]孟昊,吴武臣.一种18位SAR ADC的设计实现[J].中国集成电路,2008(104):45-62.

A Novel Design of Offset Calibrating High-speed High-resolution CMOS Comparator

Guo Panjie

(China Airborne Missile Academy,Luoyang Henan 471000)

This paper presented a novel design of offset calibrating high-speed high-resolution CMOS comparator,which is consisting of pre-amplifier and latch.The proposed comparator can deal with the shortage that traditional offset calibrating may introduce the capacitor on the access of signal.So comparing to the traditional one,the proposed new designed comparator can work with much more speed.Proposed comparator circuit is implemented in TSMC 0.35um CMOS 2P4M technology.It is adopted by the SPECTRE simulator of CADENCE software.From the result of 64MHz clock frequency simulation,it can be seen that the offset is reduced by 92.6%and the delay is only 2.68ns and the resolution is 33μV.

comparator;pre-amplifier;offset calibrating

TN792

A

1003-5168(2017)09-0045-03

2017-08-03

郭潘杰(1989-),男,硕士,研究方向:模数转换、中国空空导弹研究院元器件中心。