一种用于逐次逼近模数转换器的时域比较器

岑远军,伍钰涵,樊 华

(1.成都华微电子科技有限公司,四川 成都 610041;2.成都市第七中学高新校区,四川 成都 610041;3.电子科技大学 电子科学与工程学院,四川 成都 610054 )

随着便携式医学仪器、通信产业、安防安检系统、高性能计算、生物医学、数字信号处理等技术的不断发展,对模数转换器(ADC)的要求也在不断提高,推动着ADC 向高速、高精度和低功耗的方向发展。

ADC一般分为全并行模数转换器(flash ADC)、流水线模数转换器(pipeline ADC)、过采样模数转换器(∑Δ ADC)以及逐次逼近模数转换器(SAR ADC)。品质因数(FOM)表示ADC 每步转换需要的能量,是衡量ADC设计水平的重要指标。国外针对高精度ADC的研发较早,投入的人力、物力较大,众多欧美的高校和科研机构都开始研发高精度的ADC芯片。近年来,国内也开始对ADC进行了大量深入的研究,ADC已成为近年来国内外的研究热点[1-8]。

1 逐次逼近模数转换器基本原理

逐次逼近模数转换器的基本结构如图1所示,由采样保持、数模转换器DAC、比较器和数字控制四个模块构成,所以面积小、功耗低。比较器是逐次逼近模数转换器中唯一的模拟元件,所以逐次逼近模数转换器是所有模数转换器中模拟元件最少、数字化程度最高、随工艺进步占优势最明显的模数转换器。

图1 逐次逼近模数转换器基本结构

图2 二进制搜索算法

逐次逼近模数转换器中唯一的模拟元件是比较器,传统的比较器一般由多级前置预放大器与锁存器组成,如图3所示,也是逐次逼近模数转换器中唯一消耗静态电流的模块。如果将这唯一的模拟元件变为数字元件,则整个逐次逼近模数转换器进入数字域。数字化的时域比较器[9]顺应了工艺进步的需求,取代了模拟的电压比较器,因此,时间域逐次逼近模数转换器全部由数字电路构成,能更好地利用工艺进步带来的优势,从工艺的不断进步中获益。

图3 传统的电压比较器

2 时间域逐次逼近模数转换器基本原理

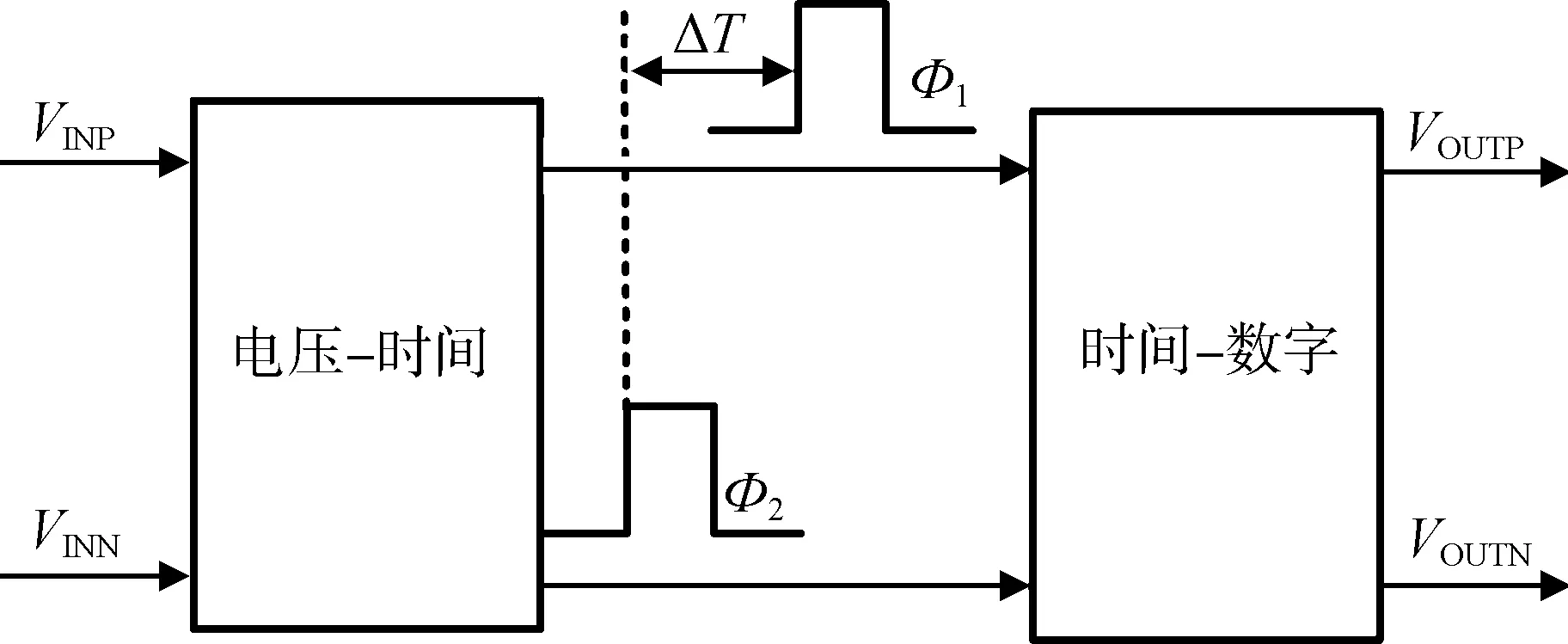

随着CMOS工艺器件尺寸、电压余度和晶体管的本征增益的不断减小,很多原有的模拟电路单元也许不再适用,因此需要设计适应CMOS工艺进步的新电路模块[10]。但是随着工艺进步,晶体管速度越来越快,而电源电压越来越低,意味着时间精度随工艺进步不断提高,而电压精度却不断降低,因此,时间信号处理作为一种新的信号处理方式不断兴起,为突破原有的模拟电路技术瓶颈带来了希望。如图4所示,体现了时间域逐次逼近模数转换器的基本思想。因为模数转换器需要处理的是电压信号,所以首先利用电压-时间转换器将输入电压信号VINP和VINN转换为时间信号Ф1和Ф2,时间-数字转换器根据Ф1和Ф2的时间间隔ΔT输出相应的数字信号[11]。

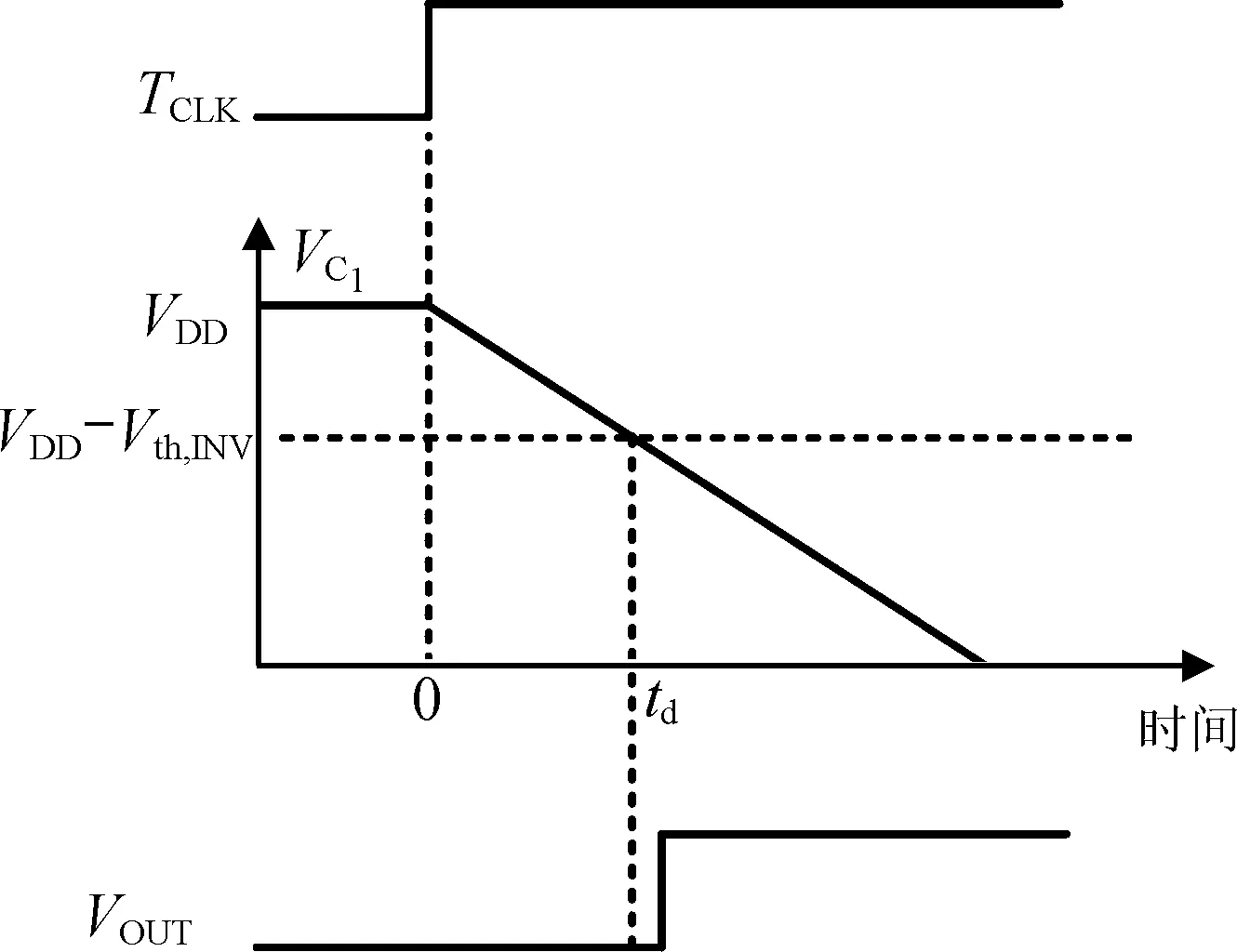

电压-时间转换器一般是将输入信号V(t)首先转换为电压控制的电流信号I(t),再将电流信号I(t)转换为时间脉冲,如图5所示。当TCLK为低电平时,电容C1通过M5被充电至电源电压VDD,输出端TOUT输出低电平。当TCLK从低电平变为高电平时,NMOS管M4导通,电容C1通过M4放电,电容C1上的电压VC1开始下降,下降至M2、M3组成的反相器的阈值电压Vth,INV时,反相器输出发生翻转,输出端VOUT由低电平变为高电平,产生脉冲输出,其传输特性如图6所示。

图4 时间模式信号处理

图5 电压-时间转换器

图6 电压-时间转换器输入、输出特性曲线

3 高速数字化的时域比较器

如图7所示,是Agnes发明的时域比较器[9]。TCLK为时钟信号,VIN和VB为输入电压,VOUT为比较器的输出电压。 Agnes采用一个简单的负边沿触发的触发器来完成时间信号到数字信号的转换。如图8所示,当时钟信号TCLK为低电平时,VOUTP和VOUTN均重置,输出高电平。当时钟信号TCLK从低电平变为高电平时,电容C1和C2开始放电,放电电流与输入电压VIN和VB的大小有关。VOUTN作为触发器的时钟,当VOUTN下降至触发器的触发电平时,触发器输出判决结果。若VIN>VB,则VOUTP下降速度比VOUTN快,触发器输出低电平;反之,若VIN< VB,则VOUTP下降速度慢,触发器输出高电平。

Agnes发明的时域比较器采用触发器作为时间-数字转换器来判断两个脉冲之间的快慢虽然简单,其缺点在于,只能用于单端逐次逼近模数转换器,不能用于差分逐次逼近模数转换器。此外,该时域比较器的另一缺陷在于,该时域比较器依靠电容充放电将输入电压差转换成时间差,再在时间域进行比较,使得ADC最高采样率只有100 kS/s,只能用于低速的逐次逼近模数转换器中。

图7 Agnes发明的时域比较器

图8 Agnes发明的时间-数字转换器输入输出波形

本文提出一种基于电压控制延迟单元的高速时域比较器,能用于高速模数转换器中,并且该时域比较器既适用于单端逐次逼近模数转换器,也适用于全差分逐次逼近模数转换器。

如图9所示,是本文提出的高精度数字化的时域比较器,它由电压-时间转换器和时间-数字转换器两部分构成,其中,电压-时间转换器由若干级电流限制的反相器串联构成。在复位模式时,时钟信号TCLK为低电平,电压-时间转换器的输出VTIP和VTIN重置为低电平。在比较模式,时钟信号TCLK为高电平,VTIP和VTIN也从低电平变为高电平,它们从低电平变为高电平的速度与输入电压VINP和VINN的大小有关,输入电压越大,VTIP和VTIN从低电平变为高电平的时间越短,时间-数字转换器[12]根据VTIP和VTIN从低电平变为高电平的时间差输出判决结果。假设VINP大于VINN,比较器输出VOUTP为高电平,VOUTN为低电平;反之,若VINP小于VINN,比较器输出VOUTN为高电平,VOUTP为低电平。

(a) 电压-时间转换器

(b) 时间-数字转换器

图9 基于电压控制延迟单元(VCDL)的比较器

HJTC 0.18 μm工艺仿真结果表明,本文提出的基于电压控制延迟线的时域比较器的分辨率为5 mV,最高工作速度可达到200 MHz,输入电压范围为-1~1 V,本文提出的比较器与Agnes 提出的比较器的性能对比如表1所示,可知本文提出的比较器在工作速度、精度和电压输入范围方面都优于传统Agnes 提出的比较器。

表1比较器性能对比

Agnes比较器本文提出的比较器工艺(μm)0.180.18单端/差分单端单端、差分最高工作速度/MHz5200分辨率/μV1005输入信号范围/V0~1-1~1

[1]FAN Hua,HAN Xue,KOBENGE S B,et al.Design considerations for low-power time-mode SAR ADC[J].International Journal of Circuit Theory and Applications,2014,42(7):707-730.

[2]CHEN Z,JIANG Y,CAI C,et al.A 22.4 μW 80 dB SNDR ∑Δ modulator with passive analog adder and SAR quantizer for EMG application[C]//in IEEE Asian Solid State Circuits Conference(A-SSCC).[S.l.]:IEEE,2012,257-260.

[3]DONADKAR D N,BHANDARI S U.Review on comparator design for high speed ADCs[C]//in 2015 International Conference on Computing Communication Control and Automation(ICCUBEA).[S.l.]:IEEE,2015,974-978.

[4]FURUTA M,NOZAWA M,ITAKURA T.A 10 bit,40MS/s,1.21 mW pipelined SAR ADC using single-ended 1.5-bit/cycle conversion[J].IEEE Journal of Solid-state Circuits,2011,46(6):1360-1370.

[5]PLAS G,DECOUTERE S,DONNAY S.A 0.16 pJ/conversion-step 2.5 mW 1.25 GS/s 4b ADC in a 90 nm digital CMOS process[C]// Proceedings of Digest of Technical Papers of IEEE International Solid-State Circuits Conference(ISSCC).[S.l.]:IEEE,2006.

[6]NGUYEN A T,XU J,YANG Z.A 14 bit 0.17 mm2SAR ADC in 0.13 μm CMOS for high precision nerve recording[C]//in Proceedings of IEEE CICC,[S.l.]:IEEE,2015,1-4.

[7]ZHOU Y,XU B,CHIU Y.A 12 bit 160 MS/s two-Sincerely yours,tep SAR ADC with background bit-weight calibration using a time-domain proximity detector[J].IEEE Journal of Solid-State Circuits,2015,50(4),920-931.

[8]CICCARELLA P,CARMINATI M,SAMPIETRO M,et al.Multichannel 65 zF rms resolution CMOS monolithic capacitive sensor for counting single micrometer-sized airborne particles on chip[J].IEEE Journal of Solid-State Circuits,2016,51(11):2545-2553.

[9]AGNES A,BONIZZONI E,MALCOVATI P,et al.A 9.4-ENOB 1V 3.8 W 100 kS/s SAR ADC with time-domain comparator[C]//IEEE International Solid-State Circuits Conference(ISSCC).[S.l.]:IEEE,2008,246-247.

[10]KOBENGE S.Circuit techniques for low-voltage low-power successive approximation register analog-to-digital converter[D].Beijing:Tsinghua University,2010.

[11]Christopher Taillefer.Analog-to-digital conversion via time-mode signal processing[D].Canada:thesis of McGill University 2003.

[12]SCHINKEL D,MENSINK E,KLUMPERINK E,et al.A double-tail latch-type voltage sense amplifier with 18ps setup+ hold time[C]// Proceedings of Digest of Technical Papers of IEEE International Solid-State Circuits Conference(ISSCC).[S.l.]:IEEE,2007:314-605.