软件无线电的通信系统实验平台研制(1)

——硬件资源

戴 伏 生

(哈尔滨工业大学(威海) 信息与电气工程学院,山东 威海 264209)

0 引 言

从系统级角度开展有实效的无线电通信实验,是通信或者电子信息类专业的一个比较难解决问题。若采用无线电通信设备开展实验,因受限于设备采用的技术,只能进行固定和单一的验证性实验,无法按意愿开展设计性和创新性实验;若单纯利用仿真软件开展系统级无线电通信实验,虽然可以开展设计性实验,但是仿真环境所假设的无线电通信工作条件往往与实际情况相差甚远,得到的仿真结果往往不够真实。如果利用开源软件无线电GNU Radio研制半实物半仿真的无线电通信系统教学实验平台装备实验室,不仅成本低廉,而且完全能够满足从系统级角度开展各种层次的具有实际效果的无线电通信实验教学。虽然一些电子设备生产商推出了通用软件无线电外设(Universal Software Radio Peripheral,USRP)产品如USRP N210,但是检索国内外文献及论坛、网站等,能够找到的资料都是如何在电脑使用等内容[1-9],并没有系统介绍USRP内部核心技术方面资料。若使用USRP产品却不掌握其软硬件工作原理,所能做的也仅限于用现有产品对信号处理功能软件进行初级验证,难以满足在教学实践中开展创新性实验。若打算开展真正意义上的系统级无线电技术创新实验和开发,只有全面掌握实验设备的软硬件工作原理才能做到,因此有必要参考USRP功能,设计一款物美价廉且核心工作原理和技术公开,以及能兼容USRP产的软件无线电通信系统教学实验平台。为利于与同行经验交流,拟对所研制的实验平台按所涉及的技术与功能划分为6个专题介绍。本文为第一个专题,阐述实验平台的系统总体思想、硬件资源、FPGA安全配置模式下片上系统结构及工作方式。

1 实验平台总体设计思想

1.1 软件无线电与研制的实验平台关系

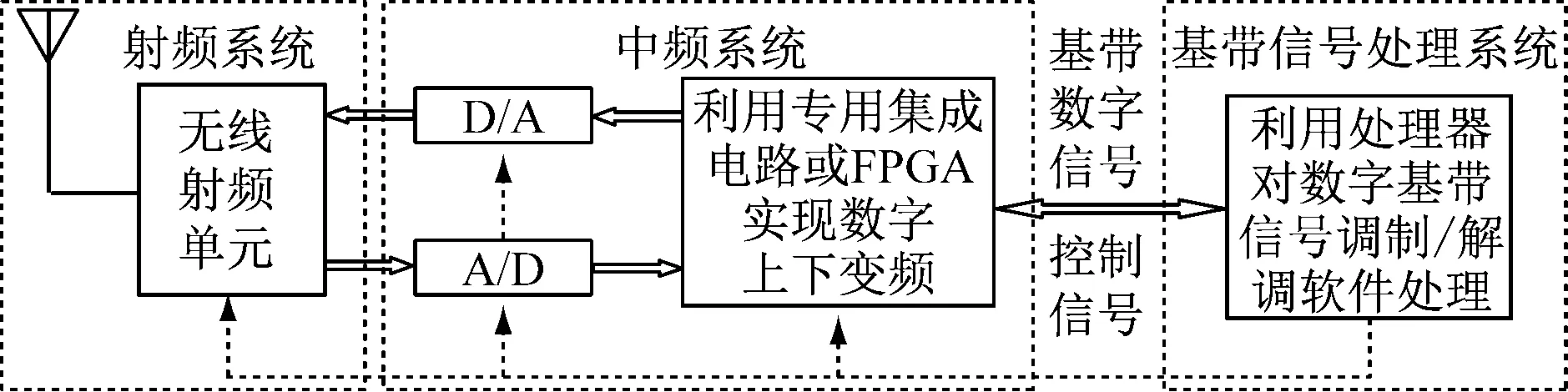

理想的软件无线电是:希望在一个开放的公共硬件平台上,利用不同可编程的软件方法实现所需要的无线电系统。但是,在目前技术条件下,软件无线电系统尚达不到全部可编程的要求,结果是产生了软件定义的无线电(Software Defined Radio,SDR)[10]。SDR的结构如图1所示,SDR的多模适应性要求宽带的射频前端,包括多频段和宽带天线、可配置的射频带通滤波器和放大器、上下变频等。SDR期望将尽可能多的通信功能用软件实现,这就要将ADC和DAC尽可能的靠近射频天线端,即由现在的基带移到中频。ADC后的所有处理都用可编程数字处理器件,依靠软件编程来实现。

图1软件定义的无线电SDR基本组成原理框图

实验平台是根据SDR思想而设计的,分为主板和射频子板。主板是指图1中的中频系统,主板中A/D后的所有处理都是用由FPGA可编程实现的,且A/D和D/A工作方式也是通过编程设置的。在设计上若要完成无线设备功能必须有射频子板配合,可认为射频子板是实验平台的配套附件。射频子板对应图1的射频系统。射频子板按照积木式思想配置,既可以为固定频率的单频点射频子板,又有可软件编程任意设置射频工作频点的宽带射频子板,实验时可根据射频应用场合和工作频率需要选择射频子板。图1中基带信号处理系统并不是实验平台组成部分,但若要使实验平台能真正工作须有电脑才行,所以电脑充当了软件无线电中的基带信号处理及核心控制系统角色。

1.2 实验平台主板功能及承担任务

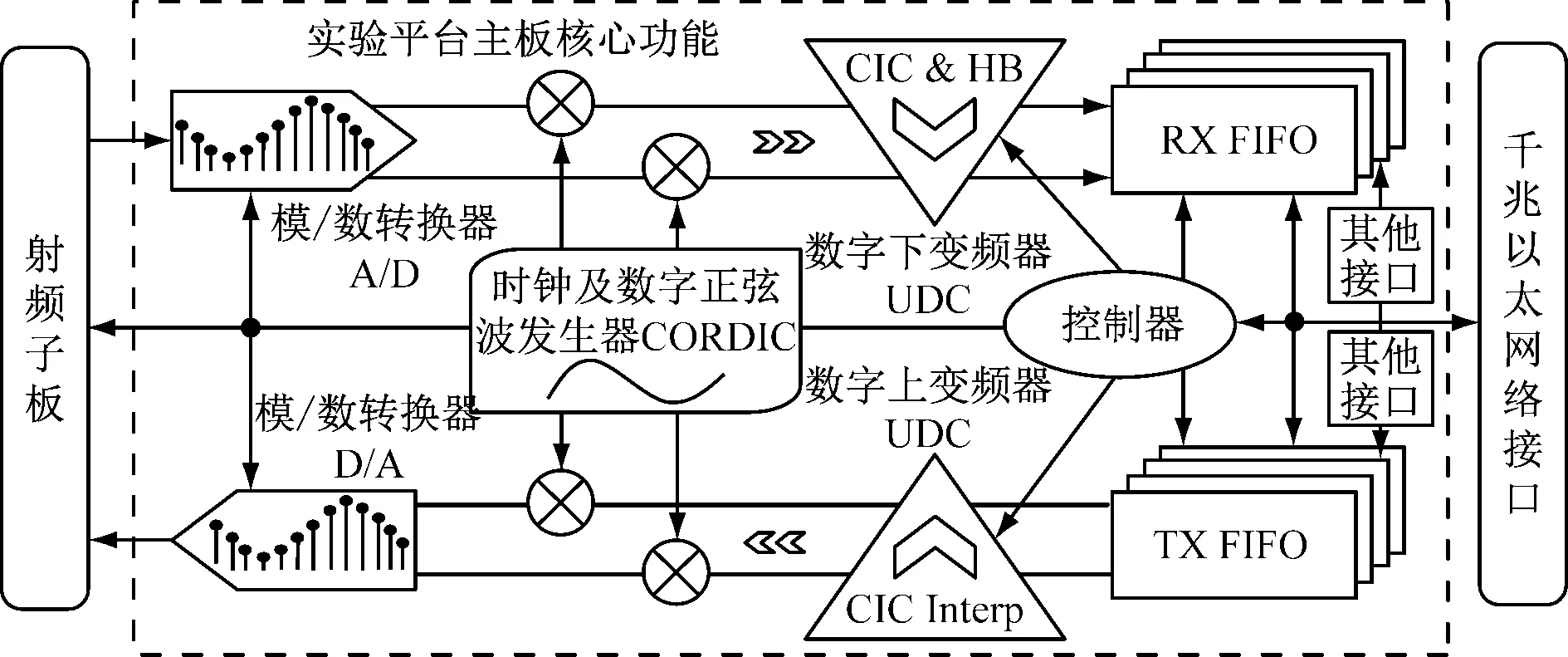

实验平台主板在软件无线电系统中担负着承上启下信息处理作用,它既是一个无线电通信系统的中频部分处理系统,又是射频信号和数字基带信号的传输系统,设计理念是,在主机CPU上完成所有波形相关方面的处理,比如数字基带调制和解调等任务。所有诸如数字上下变频、抽样和内插等任务都在主板上完成。射频信号收发任务则交由射频子板去完成,而射频子板管理和控制由主板负责。图2为实验平台主板设计理念功能框图。

图2实验平台设计理念功能框图

为适应射频通用性及兼容USRP N210的需要,实验平台采用双通道A/D及双通道D/A,与无线前端系统的射频子板采用模块化接口设计方式,可适应多种射频子板。同时,为适应多功能和扩展性的需要,实验平台考虑设计了扩展端口,可以将多个设备以同步方式组成MIMO系统。为适应高速数据流传输的需要,实验平台采用千兆以太网接口就是考虑基带信息能够实现与主机进行高速交换,这才能使得应用程序可以通过实验平台同时发送或接收能够满足50MHz的射频带宽。实验平台须借助主机对其管理和控制。主机即上位机主要是利用运行在Linux系统上免许可的GNU Radio,开展用户应用级别的软件无线电建模、仿真、代码开发、基带信号处理、对实验平台的管理与控制以及实验运行等。

2 实验平台主板硬件资源

2.1 实验平台主板硬件组成

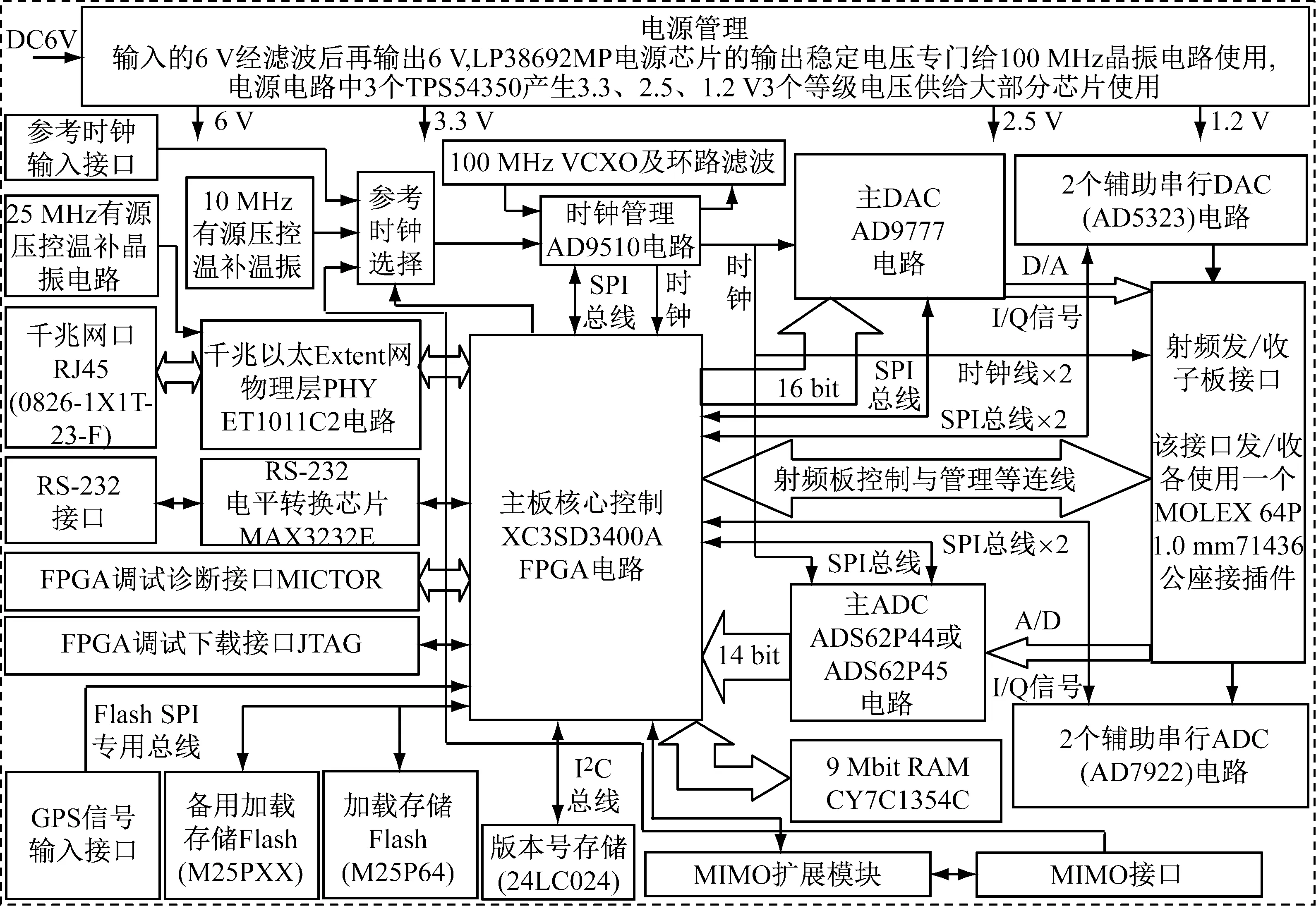

为兼容USRP N210所研制的实验平台主板组成模块如图3所示[11]。主板采用以XC3SD3400A为核心控制模块的FPGA电路,处理器及控制程序固件、数字上下变频UDC/DDC、算法实现等,都在FPGA中实现。高速D/A转换模块AD9777和A/D转换模块ADS62P45是软件无线电系统设计中最重要的一步,其中D/A用于将数字域的离散时间信号电压映射为连续的时间信号,A/D是将模拟域的连续时间信号转换为数字域的离散时间信号。RAM模块CY7C1354C用于高速采样数据的缓存。加载存储设置M25P64为Flash模块,开机时通过SPI总线实现对FPGA的加载工作。再有,实验平台一些芯片通过调试而获得的偏执矫正参考值,主要由串行A/D模块AD7922和串行D/A模块AD5623实现,也是通过SPI总线进行设置。以太网Extent物理层PHY模块ET1011C2,用于实验平台主板与电脑通过网线实现信号传输。LP38692MP和TPS54350为电源模块,用于给实验平台主板中各个芯片和模块提供稳定电源。时钟管理模块AD9510,为实验平台主板和子板提供各种稳定的时钟信号。射频发/收子板接口为DIN型64针接插件,是连接实验平台主板和射频子板的重要部分。串行储模块24LC024,通过I2C总线与FPGA的控制单元连接,主要存储实验平台主板的版本信息。MIMO扩展模块及其接口,主要是考虑多机级联使用,进而组成MIMO系统的并行高速接口,采用高速率标准的K码体制。

2.2 核心硬件电路的主要性能简介

(1) 核心控制电路XC3SD3400A。XC3SD3400A是Xilinx Spartan-3A DSP系列中的FPGA芯片[12],该芯片的系统门数3400K,等效逻辑单元53712,CLB阵列共5968,差分I/O最多213对。为了具有信号处理的功能增加了最大容量2268K块RAM和126个DSP48A模块,块RAM和DSP48A模块可运行在250MHz,DSP48A核包含18位×18位乘法器、18位预加法器、48位加法器/减法器、级联功能,能实现各种信号处理的应用。8个数字时钟管理器DCMs,拥有自校正全数字解决方案,可以对时钟信号进行分配、延时、倍频、分频和相移操作。输入/输出块IOBs,支持双向数据流和三状态操作,支持各种信号标准,包括一些高性能差分标准,包括双数据速率DDR寄存器等。多电平标准的引脚接口可选择LVCMOS、LVTTL、HSTL和SSTL单端型I/O,信号可选择3.3、2.5、1.8、1.5和1.2 V等。每个功能元素拥有相关的可编程开关矩阵,拥有功能丰富的路由功能,可任意连接所有功能模块。配置接口符合RROMs行业标准,SPI串行Flash配置接口具备CRC校验功能。利用XC3SD3400A作为实验平台主板逻辑核心控制器件,目前被使用的资源约占芯片总资源的37%,还有极大的资源给留给学生继续深入开发或者功能升级使用。

(2) 数字/模拟和模拟/数字转换器。实验平台主板的数字/模拟转换器采用了可编程控制的AD9777,通过标准的SPI串行控制接口可实现对芯片的工作方式进行编程控制。AD9777支持最高160 MHz时钟输入[13],在实验平台主板中输入的时钟为100 MHz,AD9777具有内部锁相环时钟倍频器,通过编程控制可使系统最高时钟可达fs=400 MHz,进而实现400MSPS的最高采样率。能适应复数正交调信号的I、Q方式应用的双通道16位D/A。设计有编程可选的2×、4×、8×内插滤波器,以及编程可选的fs/2、fs/4、fs/8正交变频调制和镜像抑制功能。可编程多功能输入数据接口,能适应双端口或者采用单端口交错输入,输入信号既可以用二进制补码也可以用标准二进制码。具有镜像抑制功能以及可编程的通道增益和偏置调整。

实验平台主板的模拟/数字转换器采用了可编程控制的ADS62P44/P45,通过标准的SPI串行控制接口可实现对芯片的工作方式进行编程控制。ADS62P4X是一个双通道14位A/D转换[14],使用一个内部采样保持和低时钟抖动缓冲区,ADC支持高信噪比、高输入频率下的高SFDR。带有步进3.5 dB和0.5 dB的粗及细增益控制模块,通过编程在0~6 dB增益可调,目的是提高SFDR性能以全面适应较低信号输入范围。两个通道最大采样率均为125×106S/s(SPS)。ADS62P4X包括一个数字处理模块,它包含几种有用的和常用的数字功能,例如:ADC偏移校正,每间隔0.05 dB的细调增益校正。可编程的÷2、÷4、÷8倍降采样抽取和内置自定义滤波器,内嵌一个最大抽头系数为24的FIR滤波器,可进行低通、带通、高通滤波。数字输出接口支持LVCMOS和LVDS两种电平,通过编程选项可按照并行LVCMOS方式或者双倍数据速率DDR LVDS输出转换后数字。

(3) 时钟管理AD9510电路。AD9510输入参考时钟通过低压差分多路选择开关SY98545经过编程选择,可选择的参考时钟有:外部GPS时钟、MIMO接口时钟、主板上通过有源压控温补晶振VCTCXO产生的精准时钟。实验平台主板默认选择的参考时钟是主板VCTCXO产生的10MHz精准时钟。AD9510具有完整的片上PLL内核[15],仅需外部环路滤波器和VCO/VCXO的配合,实验平台主板中AD9510利用PLL和VCO/VCXO及环路滤波器,产生100 MHz内部时钟。AD9510提供8路独立的时钟输出,其中4路输出最高可达1.2 GHz的低压正发射极耦合逻辑(LVPECL),另外4路输出可选择为LVDS(800 MHz)或CMOS(250 MHz)。每路输出都有一个可编程分频器,可以旁路该分频器或者设置最高32的整数分频比。一路时钟输出相对于另一路时钟输出的相位可通过分频器相位选择功能改变,用作时序粗调。2路LVDS/CMOS输出具有可编程延迟功能,其满量程范围最高为8 ns延迟,该精密调谐延迟模块具有5位分辨率,提供25种编程延迟设置。

在实验平台主板中AD9510的8路独立时钟输出,有2路输出运用了延迟模块。其中有4路通过低压正发射极耦合LVPECL逻辑电平方式输出100 MHz时钟,2路分别送给A/D、D/A模块;1路通过匹配网络送给FPGA作为主时钟;1路留给备用测试接口。再有,通过LVCMOS/LVDS逻辑电平方式分2路输出的100 MHz时钟,1路送给射频子板的接收RX时钟接口;另1路延迟设置2.12712 ns送给发射TX时钟接口。最后2路输出,1路通过低压差分逻辑电平LVDS方式输出100MHz时钟后,再经过DS90LT012为3.3 V单端输出方式后,送给与MIMO模块有关的FPGA的I/O端口,以及MIMO模块TLK2701,作为本机FPGA一些I/O端口和MIMO芯片TLK2701的工作时钟;另1路延迟设置2.12712 ns的10 MHz时钟通过低压差分逻辑电平LVDS方式送给MIMO接口,作为实验平台级联时给其他设备的参考时钟。

再有,实验平台主板中XC3SD3400A FPGA内部的数字时钟管理模块DCM[12],用于产生FPGA内部模块需要的各种时钟。DCM模块输出3路不同的时钟DSP_CLK、WB_CLK、CLK270。其中,DSP_CLK主要用于信号处理部分,作为FPGA中的数据分流、通用可编程I/O接口GPIO、状态设置寄存器、VITA-49协议状态机、数字上下变频、A/D接收及D/A发送等数字处理模块提供处理时钟;WB_CLK提供的时钟主要用于与内部Wishbone总线读写相关的模块,如Wishbone总线时钟、ZPU处理器读写Wishbone时钟、数据分流模块读写总线时钟等。CLK270时钟主要配合外部MIMO接口使用。

3 实验平台主板安全模式下的系统

3.1 FPGA安全配置启动过程

主板上XC3SD3400A的FPGA模块为核心控制电路,XC3SD3400A拥有专用的多重启动与动态配置Multi boot逻辑配置模块及其接口ICAP[12,16]。通过ICAP设置配置模块中的相关寄存器,实现在不同配置bit流文件中的切换。在启动实验平台时,若没有从上位机给M25P64Flash加载过硬件驱动(User Hardware Driver,UHD)的配置镜像文件,或者开机配置过程中检测安全启动S2开关控制的引脚为低电平时,仅加载M25P64Flash中不能改动的安全配置镜像文件,该模块为自检加载文件以及最基本的配置镜像文件。考虑到兼容USRP N210,实验平台主板安全配置步骤为:

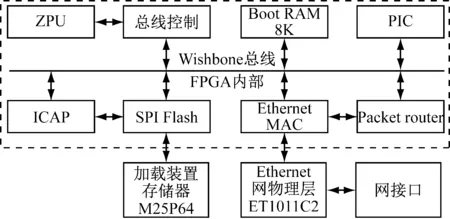

(1) 从M25P64 Flash的0x00000000地址开始读Safe_fpga_image对FPGA进行逻辑电路系统的配置,为FPGA配置一个占用很少的资源和构架很小的32位处理器ZPU(Zylin CPU)软核[17],并配置32位Wishbone总线及其总线控制器[18],以及挂接在Wishbone总线上的专用SPI接口(SPI for Flash)、双端口哈佛型(Harvard architecture)的引导程序存储器(Boot RAM)、内部配置访问端口(Internal Configuration Access Port,ICAP)、可编程中断控制器(Programmable Interrupt Controller,PIC)、数据包路由器(Packet router)、简化的以太网数据链路媒体层(Ethernet MAC)等模块。这样就构建了一个精简的片上系统(System on Programmable Chip,SoPC)。

(2) 利用状态机逻辑电路控制内部配置访问端口ICAP,从M25P64 Flash的0x003F0000地址开始读取Safe_fw_image可执行程序代码配置到Boot RAM中,即对ZPU进行可执行代码的安全配置代码。

(3) 片上系统开始工作,初始化后ZPU便能够实现对FPGA的控制,安全配置之后形成的系统如图4所示。

图4FPGA安全配置之后构建出的最小工作系统

系统中总线控制器确定ZPU处理器是Wishbone总线的主控制器,其他挂接在Wishbone总线的均为从设备。ZPU有着固定8bit的操作码,而所有操作数都是32bit,地址总线宽度为16bit。ZPU构成片上系统架构的所有部分如程序计数器PC、堆栈指针SP等,均使用一个带有双端口哈佛结构RAM作为数据和代码的存储。实验平台主板中ZPU总共使用了39条指令,可产生22种工作状态。

Ethernet MAC模块中包括Simple_gemac和Simple_gemac_wb两个模块[19],Simple_gemac模块主要完成发送,接收以及流量控制的功能;Simple_gemac_wb主要处理发送和接收来自Wishbone总线以及以太网物理层PHY传来的管理控制信息。

实验平台主板中MAC层之上定义的数据包路由模块Packet router,是利用Verilog HDL逻辑描述语言进行逻辑抽象实现的,它根据数据发送上下位机的方向,主要完成跨越IP层对UDP头部的解析或者添加,然后把数据流交给对应的模块进行处理,所有的网络数据包经由Packet_router发往FPGA中的目的模块。Packet_router采用的是一种轻量级IPv4协议LWIP(Light Weight IP)[20],LWIP实现的重点是在保持IPv4协议栈主要功能基础上减少对资源的占用,且有无操作系统的支持都可以运行,非常适合在片上系统SoPC中使用。在实验平台主板的ZPU中运行是LWIP中轻量级UDP/IP协议,其默认的IP地址是192.168.10.2。

3.2 安全模式下实验平台主板工作方式

在安全模式配置之后,ZPU将交由双端口结构的引导程序存储器(Boot RAM)执行程序代码。初始化后,通过以太网MII/GMII功能模块和接口,与上位机进行协议和速率协商和匹配,之后按照协商协议和速率通信。在安全模式工作时,与上位机的以太网通信均需要ZPU控制,且能与上位机通过UDP编号49152的端口进行通信,用来接收上位机的控制信息或实验平台主板传送应答信息。

尽管在安全模式工作下可以正常启动实验平台,但是还不能使用GNU Radio进行无线传输数据的收发,若要正常使用实验平台,必须将实验平台硬件驱动UHD配置镜像文件装入主板的M25P64 Flash中。UHD旨在为实验平台提供宿主驱动和为GNU Radio提供硬件电路的应用程序规范化访问接口API。这样用户便可独立使用UHD驱动或灵活同第三方应用软件,如Gnuradio、Labview或Simulink相配合进行实验平台的使用和开发。

考虑到实验平台对USRP N210的兼容,上位机通过UDP编号49154的端口同实验平台进行通信,实现对实验平台的用户硬件驱动配置UHD(User Hardware Driver)进行固件镜像及升级。因文章篇幅限制,关于实验平台硬件驱动UHD的配置镜像文件,以及硬件驱动UHD配置之后实验平台有关工作原理将另文介绍。

4 结 语

从实用软件无线电技术的角度,对基于软件无线电的通信系统实验平台总体设计思想,硬件系统构成及核心电路主要性能,安全模式下FPGA的配置等内容的系统介绍。通过这些介绍能够初步体会到,基于软件无线电的通信系统实验平台总体设计指导思想是:在系统结构上采用层次化和网络化,在功能设计上采用模块化和可控化,在信号适应性上采用高速化和宽带化,在推广性方面的兼容化。掌握实验平台的总体设计思想和系统资源,不仅有助于对实验平台工作过程的理解,而且为进一步掌握实验平台系统软硬件工作原理奠定了必要的基础。在安全模式下实验平台主要是构建了一个可编程片上系统SoPC,以及Ethernet网络通信功能。虽然安全模式下可以正常启动实验平台工作,但是并不能利用上位机的GNU Radio进行无线传输数据的收发。若要想充分发挥实验平台提供的资源,还需要进一步对其进行配置和驱动,进而构建出完备的无线电工作系统,因此还需要更深入地介绍实验平台工作原理。笔者将继续撰文对如何对FPGA进行在线的重构驱动和配置,进而使实验平台构建出一个功能完整系统的方法及工作原理进行阐述。

参考文献(References):

[1]杨宇红, 袁焱, 田砾,等. 基于软件无线电平台的通信实验教学[J]. 实验室研究与探索, 2015, 34(4): 186-188.

[2]葛熠, 陈为刚. 基于嵌入式USRP的无线通信实现[J]. 电子测量技术, 2016, 35(6): 167-171.

[3]孟梅梅, 李晓辉, 刘乃安, 等. 基于NI USRP的多模式自适应无线通信实验平台[J]. 现代电子技术, 2016, 39(1): 24-26.

[4]赵楠, 武明虎. 基于GNU Radio和USRP的宽频带并行感知平台设计[J]. 计算机应用研究, 2015, 32(12):3779-3781.

[5]钱建军, 陈树新. 基于USRP的GPS基带信号源设计与实现[J]. 实验室研究与探索, 2015, 34(10): 72-75.

[6]杨晋生, 李中品. 基于USRP的室内无线信道场强的仿真与测量[J]. 电子测量技术, 2015, 34(5): 131-134.

[7]余兵才, 姚明, 邓晓华, 等. 基于GNU Radio和USRP新型软件频谱分析仪[J]. 现代雷达, 2014, 36(9): 17-21.

[8]魏以民,黄葆华,高媛媛. “通信原理”课程中载波同步的教学方法研究[J]. 电气电子教学学报, 2013,35(5): 61-65.

[9]Truong N B, Yu C. Investigating latency in GNU software radio with USRP embedded series SDR platform[C]//IEEE International Conference on Broadband and Wireless Computing, Communication and Applications.2013:9-14.

[10]Grayver E. Implementing Software Defined Radio[M]. USA: Springer, 2013.

[11]Ettus Research LLC. USRP N210电路原理图[EB/OL]. http://files.ettus.com/schematics/n200/n2xx.pdf.

[12]Xilinx Inc. XtremeDSP DSP48A for Spartan-3A DSP FPGAs[DB/OL]. http://www.xilinx.com/support/ documentation/ user_guides/ug431.pdf.

[13]Analog Devices, Inc. AD9777数据手册[EB/OL]. http://www.analog.com/media/en/technical-documentation/data-sheets/AD-9777.pdf.

[14]Texas Instruments, Inc. ADS62P44/P45数据手册[EB/OL]. http://www.ti.com.cn/cn/lit/ds/symlink/ads62p44.pdf.

[15]Analog Devices, Inc. AD9510数据手册[EB/OL]. http://www.analog.com/media/en/technical-documentation/data-sheets/AD-9510.pdf.

[16]李平, 吴晓, 山寿. 基于SPI FLASH的FPGA多重配置[J]. 现代电子技术, 2013,36(22):127-130.

[17]Yvind Harboe, General Manager, Zylin AS. Zylin CPU资料[EB/OL]. http://repo.or.cz/w/zpu.git/blob/HEAD:/zpu/docs/ presentations /zpu.pdf.

[18]Richard Herveille, Open Cores Organization. Wishbone-B4资料[EB/OL]. http://opencores.org/cdn/downloads/wbspec_b4.pdf.

[19]Xilinx Inc. Ethernet MAC资料[EB/OL]. http://www.xilinx.com/support/documentation/ip_documentation/tri_mode_eth_mac/ v5_5/pg051-tri-mode-eth-mac.pdf.

[20]Adam D. Design and Implementation of the LWIP TCP/IP Stack[S]. Swedish Institute of Computer Science, 2001.