基于多核DSP的SAR数据并行访问研究

周峰 李健

摘 要: 合成孔径雷达(SAR)数据处理中的一个重要操作是分别访问存储器中的距离向和方位向数据,当前在Keystone多核DSP平台上主要使用单个核或EDMA访问SAR数据,但很多情形下无法充分利用存储器的带宽。针对该问题,结合EDMA,DDR存储器等外设的硬件特性,提出一种适用于多核DSP的SAR数据分块映射存储方法及行切换开销最优的并行访问技术,并给出应用并行访问模式的一个充分条件。测试结果表明,分块映射存储方法能均衡距离向和方位向数据的访问速度,且更能充分地利用存储器带宽,提高数据的访问效率。

关键词: 多核DSP; 并行访问; 信号处理; 矩阵转置; 合成孔径雷达; 分块映射

中图分类号: TN957.52?34 文献标识码: A 文章编号: 1004?373X(2018)15?0026?05

Research on multi?core DSP based parallel access for SAR data

ZHOU Feng, LI Jian

(The 32th Research Institute of China Electronics Technology Group Corporation, Shanghai 201808, China)

Abstract: One of the important operations during SAR (synthetic aperture radar) data processing is to access the range direction and azimuth data stored in the memory. The method of single core or EDMA is mainly used to access the SAR data on Keystone multi?core DSP platform, but the memory bandwidth couldn′t be taken full advantage in many cases. For the above problem, the hardware features of EDMA, DDR and other peripherals are combined to propose a SAR data block mapping storage method suitable for multi?core DSP, and a parallel access technology for optimal row switch overhead. A sufficient condition for parallel access mode is given. The test results show that the block mapping storage method can balance the access speed of range direction and azimuth data, utilize the memory bandwidth more effectively, and improve the data access efficiency.

Keywords: multi?core DSP; parallel access; signal processing; matrix transpose; SAR; block mapping

0 引 言

合成孔径雷达(SAR)是一种应用比较广泛的成像雷达,具有二维分辨能力,抗干扰能力强,能全天候、全天时工作,并且能够穿透云层和掩盖物。在国防和国民经济等众多领域中扮演着重要角色。目前,多核DSP的数据处理平台在SAR信号处理领域仍有着广泛的应用[1?3]。SAR采集到的原始数据为一个二维矩阵,二维矩阵中每一行的数据是对发射的线性调频脉冲进行采样的值,每一列的数据是雷达在不同空间位置处对接收到的线性调频脉冲进行采样的值。因此,二维矩阵的行方向就为距离向,列方向就为方位向。

当前SAR数据存储器主要以DDR SDRAM为主。对DDR存储器的连续地址访问时,速率可达到10 GB/s,如果矩阵按照顺序存储,则距离向数据的访问速率较高。方位向数据由于被分开存储到DDR的多个页中,故需要频繁地进行关闭页、预充电、打开页等操作,导致其访问速率降得很低,大约只能达到150 MB/s。因此,需要研究一种能提高方位向数据访问速率的方法。文献[4?6]分别研究了两页式、三页式矩阵转置方法,文献[2,7?8]研究了快速转置和原位转置方法。这些方法适合于只需要单次转置的SAR成像算法,例如距离多普勒算法。文献[9?10]研究了矩阵线性映射方法,将矩阵分块映射到DDR的页面内,能在一定程度上均衡距离向和方位向数据的访问速度。但文献[9]的映射方法会造成DDR不同行内的方位向数据的间隔过大,无法发挥Keystone上EDMA的性能。文献[10]需要设计专用的地址计算硬件单元,无法直接在DSP上使用。文献[3]提出一种交织存储方式,解交织时仅使用单路EDMA传输,没有充分利用DSP的传输带宽,而且通过使用CPU解交织得到距离向和方位向数据,不仅占用计算资源,而且访问速度也慢。

本文根据EDMA和DDR的硬件特性,提出一种适合于Keystone多核DSP的分块映射存储方式,并研究SAR数据的并行访问模式,给出应用该模式的充分条件。该方法能提高数据的实际传输带宽,加快数据的访问速度。本文提出的矩阵分块映射方法和文献[2,9]使用的方法相比更适合在DSP上使用,和文献[10]相比,更能充分发挥多核DSP的并行处理性能。

1 并行访问设计

1.1 分块映射存储

矩阵分块映射的主要方法就是将矩阵分为多个子矩阵,再分别将每个子矩阵存储到DDR的一个物理页面中。这样DDR的一个页面中既有距离向数据,也有方位向数据,因此可在一定程度上均衡距离向和方位向数据的访问。

设SAR所处理的数据矩阵是个二维矩阵,记为[Ai, j],[0≤i≤NA-1],[0≤j≤NR-1],其中,[NA]表示方位向采样点数,[NR]表示距离向采样点数,[i]表示逻辑行号,[j]表示逻辑列号,这里的[i, j]称为数据的逻辑坐标。

DDR在寻址时是按照bank、行、列的顺序进行,因此是个三维空间,记为[Bb, r, c],其中,[b]表示bank号,[r]表示行号,[c]表示列号。这里的[b, r, c]称为数据的物理坐标。

映射过程就是将数据的二维逻辑坐标映射到三维物理坐标的过程,具体方法如下:

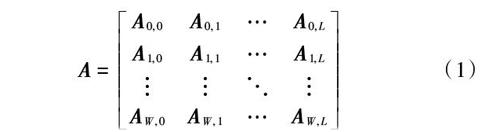

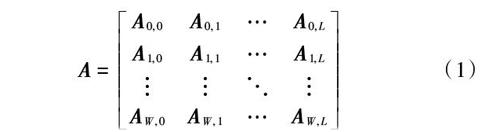

将二维矩阵[A]分成[W×L]个等大小的子矩阵,其中,[W]表示方位向上子矩阵的个数,[L]表示距离向上子矩阵的个数。子矩阵的大小为[Na×Nr],每个子矩阵用[Am,n]表示,其中,[Na=NAW],[Nr=NRL],[m∈0, W],[n∈0, L]。分块后的矩阵如下式所示:

将每个子矩阵映射到DDR的一个页面,子矩阵的大小是2 KB,包含256个复数点。子矩阵可以采用方阵形式([16×16])或其他形式([8×32],[4×64]等),为使方位向和距离向的行切换次数保持平衡,子矩阵采用方阵的形式[7]。

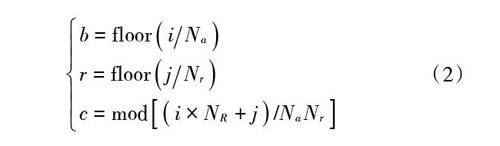

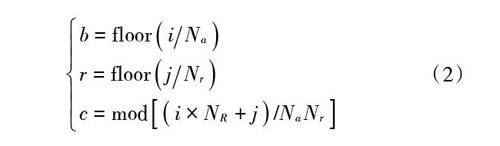

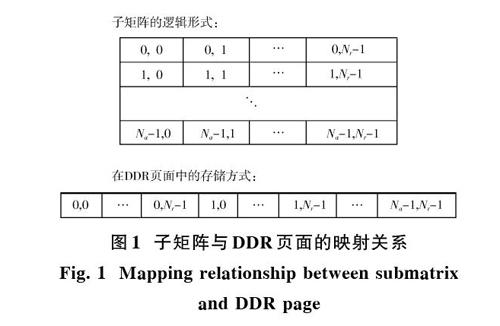

根据映射方法建立从二维逻辑坐标[i, j]到三维物理坐标[b, r, c]的映射关系:

式中:[floorx]表示对变量[x]向下取整;[modxy]表示对[xy]取余。

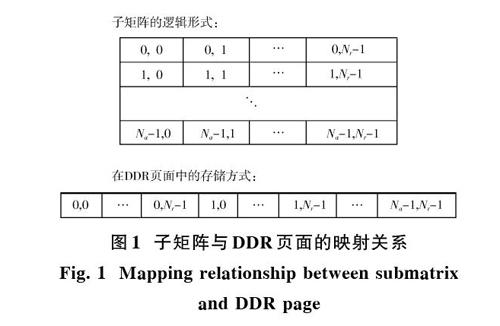

在上面的两种映射关系中,子矩阵内的数据在每个DDR页面里的排列顺序如图1所示。

在图1的存储方式中,每[Na]个距离向数据是连续存储的,方位向数据是离散存储的。

映射后的bank分布图如图2所示,图中的每个小方格表示一个子矩阵,小方格里的数字表示bank号,根据前面的映射关系,每个子矩阵行[Ai,0,Ai,1,…,Ai,L]存放在同一个bank中,接着下一个子矩阵行存放在下一个bank中。

1.2 并行访问

由文献[11]可知,对于64位1 333 MB的DDR,其最大访问带宽是10 666 MB/s,而EDMA仅CC0的一个传输控制器的最大带宽就能达到16 000 MB/s,因此,DDR沒有足够的带宽支持多个EDMA传输控制器对DDR进行并发访问,优先级相同的情况下,它们将瓜分DDR的带宽。本文之所以还使用多个EDMA同时对DDR进行访问是因为单个EDMA传输控制器实际使用带宽远远达不到其理论最大带宽。EDMA的实际传输带宽与ACNT的取值呈正相关的关系[11],ACNT的取值越大,其实际传输带宽就越大。在根据1.1节的存储方式访问距离向或方位向数据时,ACNT取值最大就是[8Nr]或[8Na],对于[16×16]的方型子矩阵,即128,对应的实际传输带宽约600 MB/s,这就给并行访问提供了改善实际传输带宽的空间。

注1:若单个EDMA访问存储器时带宽得到充分利用,使用多个EDMA反而会因为总线竞争等因素降低总的带宽利用率。因此,并行访问模式适用于单个EDMA没有充分利用存储器带宽的情形。

在使用多个EDMA并行访问数据时,会引入附加的行切换开销,例如,同时访问DDR中同一个bank中不同的页面。在访问距离向和方位向数据时需要采用一定的方式来避免并行访问带来的附加行切换开销。在使用多个EDMA访问数据前,需要合理地为每个EDMA安排待访问的DDR区域,下面针对距离向和方位向数据分别讨论。

在访问距离向数据时,可使用下面的方式:

每个EDMA访问一个bank中的数据,如图3所示,图中的细箭头表示各个EDMA的访问起始位置,首先访问G0组中的数据,访问完全部数据后,再跳转到G1组继续访问,直到访问完最后一组。这种访问方式的好处是在任意时刻多个EDMA访问的均是不同bank中的页面,因此这是访问距离向数据时行切换开销最优的方式。

由于距离向数据在每个页面内是连续存储的,可使用EDMA的AB同步传输模式进行访问,每次访问可读完一行距离向数据。

在访问方位向数据时,可使用下面的方式:

所有EDMA跨bank访问一个页面中的数据,如图3所示,图中的粗箭头表示各个EDMA的访问起始位置,首先访问[G0]组中第一列子矩阵的数据,接着跳转到[G1]组继续访问第一列子矩阵的数据,直到访问完最后一组。然后再访问[G0]中第二列的子矩阵,以此类推。这种访问方式的好处是多个EDMA要么在访问不同bank中的页面,要么在访问同一个bank中的相同页面,因此这是访问方位向数据时行切换开销最优的方式。

由于方位向数据在每个页面内是离散存储的,可使用EDMA的链式传输模式进行访问。每次访问可读完一列方位向数据。

注2:Keystone多核DSP上独立的传输控制器多于10个,由于其支持的DDR bank的数量最多为8个,使用全部的EDMA将导致在任意时刻都产生行切换开销,因此,在实际中同时使用的EDMA传输控制器的数量最好不超过8个。

1.3 应用条件

1.2节讨论了并行访问时如何避免引入附加的行切换开销。但除了行切换,并行访问时的竞争也会导致各个EDMA的访问带宽降低,当竞争过于激烈时甚至可能导致并行模式下总的访问带宽小于单个EDMA,此时并行访问将变得没有意义。这一小节讨论应用并行访问时的一个充分条件。

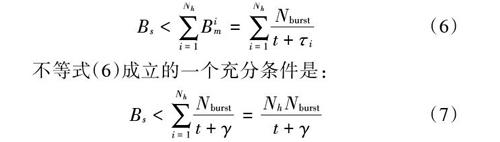

在多个EDMA同时访问DDR时,设第[i]个EDMA在访问存储器时的等待时间是[τi],其中,[i∈0,Nh],[Nh]表示EDMA的总数。Keystone上的DDR控制器有一个特点是当最早的访问请求超过预设时间后,会临时提高该请求的优先级至最高[12]。这意味着:

式中[γ]表示预设时间值,是16个DDR3CLKOUT的倍数,可通过DDR3控制器中的VBUSM寄存器进行设置。

在使用单个EDMA时,即没有竞争产生,假设对DDR进行访问的带宽是[Bs],则:

式中:[Nburst]表示DDR一次突发传输的字节数;[t]表示相应的传输时间。

在使用多个EDMA时,此时会产生竞争,假设第i个EDMA对DDR进行访问时的带宽是[Bim],则:

为让并行访问下总的访问带宽大于单个EDMA下的訪问带宽,令:

不等式(6)成立的一个充分条件是:

即并行访问时每个EDMA的等待时间均是[γ],这是并行模式下访问带宽最差的情形。

由式(4),式(7)可得:

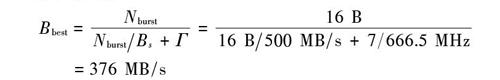

[γ 因此,在配置VBUSM寄存器时,可根据式(8)进行计算来确保并行模式下总的访问带宽大于单个EDMA的带宽。 当单个EDMA的实际传输带宽[B]已知时,还可根据式(3)~式(5)估算并行访问在最差情形下的实际传输带宽[Bworst]: [Bworst=defBim=NburstNburstBs+τi≥NburstNburstBs+γ] (9) 式(3)给出了一个EDMA访问等待时间[τi]的上界,还可根据实验的方法确定其下界。 由式(4),式(5)可得: [τi=NburstBs-BimBsBim] (10) 当多个EDMA在A同步传输模式下对DDR存储器进行高速并发访问时,此时的等待时间[τi]最小,记为[Γ],根据文献[11]的测试结果可得: [Γ=16 B10 383 MBs-1 312 MBs10 383×1 312 MB2s2=7 DDR3CLKOUT] (11) 因此,当单个EDMA的实际传输带宽[B]已知时,可根据式(11)估算并行访问在最好情形下的实际传输带宽[Bbest]: [Bbest=defNburstNburstBs+Γ] (12) 2 测试结果 当前已经根据本文所设计的方法开发了SAR数据存储库。采用德州仪器发行的TMDSEVM6678L开发板作为测试硬件平台。通过开发板上的DSP完成对片外DDR3 SDRAM的访问,并对矩阵分块映射方法和并行访问带宽进行测试。 将一个4k×8k的二维复数矩阵按照分块映射的方法存储到DDR中,然后8个核分别使用1个EDMA传输控制器,再以距离向或方位向的方式同时将数据从DDR读取到各自的LL2中,直到遍历完全部的数据,记录总时间并计算实际访问带宽。 在测试时用到的传输控制器为:CC0的TC0,TC1;CC1的TC0,TC1,TC2,TC3和CC2的TC0,TC1。首先通过核0分别使用这8个传输控制器读取DDR中的距离向或方位向数据,记录并计算实际的传输带宽,如图4中的斜线柱状图所示。接着再通过8个核同时使用8个传输控制器读取DDR中的数据,实际的传输带宽如图4中的圆点柱状图所示。 通过图4中的测试结果可以看出,在使用单个EDMA时,每个EDMA传输控制器的实际访问带宽大约是500 MB/s,在并行访问时,每个EDMA传输控制器的实际访问带宽大约是320 MB/s,与单个EDMA相比均有所下降,这是DDR存储总线的竞争引起。但并行模式下总的访问带宽大约是2 560 MB/s,与单个EDMA相比提高了大约5倍。 可根据式(9)估算并行访问时各个EDMA的最差访问带宽[Bworst]。根据文献[12]可知,DDR控制器一次突发传输的字节数是16,DDR3CLKOUT设置为666.5 MHz,则: [Bworst=NburstNburstBs+?=16 B16 B500 MBs+16666.5 MHz=286 MBs] 再根据式(12)计算并行访问时各个EDMA的最优访问带宽:

[Bbest=NburstNburstBs+Γ=16 B16 B500 MBs+7666.5 MHz=376 MBs]

实际每个EDMA的并行访问带宽是320 MB/s,正好位于区间[Bworst,Bbest]中,这与实测结果是吻合的。对方位向数据的访问测试结果和距离向的类似,不再赘述。

3 结 论

通过对Keystone上EDMA和DDR控制器的特性进行分析,提出一种适用于多核DSP的SAR数据分块映射存储方法,将二维矩阵分块存储到DDR的物理页面中。EDMA可直接从DDR存储器中访问一行距离向和方位向数据,并能以附加行切换开销最小的方式实现并行访问,并给出应用并行访问模式的充分条件。测试结果表明,该方法不仅能均衡距离向和方位向数据的访问速度,还能同时提高两个维度上数据的实际访问带宽。

参考文献

[1] 张强,冯仰松,郭朋.基于多核DSP互联架构的SAR处理研究与设计[J].电子技术应用,2016,42(1):37?39.

ZHANG Qiang, FENG Yangsong, GUO Peng. Research and design of SAR imaging based on multi?core DSP interconnection architecture [J]. Application of electronic technique, 2016, 42(1): 37?39.

[2] 张兰,秦斯奇,唐瑞.SAR成像系统快速矩阵转置算法的设计[J].科学技术与工程,2016,16(21):266?271.

ZHANG Lan, QIN Siqi, TANG Rui. Design of fast matrix transposition algorithm for SAR image systems [J]. Science technology and engineering, 2016, 16(21): 266?271.

[3] 张维陶,孙英钦,姚迪.用于合成孔径雷达实时成像的高性能虚拟单节点设计[J].信号处理,2013,29(10):1376?1382.

ZHANG Weitao, SUN Yingqin, YAO Di. High?performance virtual single?node design for synthetic aperture radar real?time imaging [J]. Journal of signal processing, 2013, 29(10): 1376?1382.

[4] 卢世祥,韩松,王岩飞.合成孔径雷达实时成像转置存储器的两页式结构与实现[J].电子与信息学报,2005,27(8):1226?1228.

LU Shixiang, HAN Song, WANG Yanfei. The structure and implementation of the two?frame corner turn memory (CTM) in real time imaging of SAR [J]. Journal of electronics & information technology, 2005, 27(8): 1226?1228.

[5] 谢应科,张涛,韩承德.实时SAR成像系统中矩阵转置的设计和实现[J].计算机研究与发展,2003,40(1):6?11.

XIE Yingke, ZHANG Tao, HAN Chengde. Design and implementation of matrix transposition unit for real?time SAR image systems [J]. Journal of computer research and development, 2003, 40(1): 6?11.

[6] 李早社,禹卫东,汪亮,等.基于SDRAM的星载SAR星上实时成像转置存储器[J].信号处理,2007,23(3):433?436.

LI Zaoshe, YU Weidong, WANG Liang, et al. Corner turning memory based on SDRAM for spaceborne SAR on?board real?time imaging [J]. Journal of signal processing, 2007, 23(3): 433?436.

[7] 林桐,谢宜壮,刘伟.实时SAR成像系统矩阵原位转置的实现[J].计算机工程,2013,39(6):319.

LIN Tong, XIE Yizhuang, LIU Wei. Implementation of matrix in?place transpose for real?time SAR imaging system [J]. Computer engineering, 2013, 39(6): 319.

[8] 鲍胜荣,周海斌.SAR实时成像高效矩阵转置研究和实现[J].现代雷达,2013,35(3):24?27.

BAO Shengrong, ZHOU Haibin. Study and implementation of high efficient matrix transpose for SAR real?time imaging system [J]. Modern radar, 2013, 35(3): 24?27.

[9] 边明明,毕福昆,汪精华.实时SAR成像系统矩阵转置方法研究与实现[J].计算机工程与应用,2011, 47(22):117?119.

BIAN Mingming, BI Fukun, WANG Jinghua. Research and implementation of matrix transpose for real?time SAR imaging system [J]. Computer engineering and applications, 2011, 47(22): 117?119.

[10] 刘小宁,谢宜壮,赵博雅,等.一种二维访问效率均衡的SAR数据矩阵转置方法[J].电子学报,2016,44(1):33?38.

LIU Xiaoning, XIE Yizhuang, ZHAO Boya, et al. A SAR data matrix transpose method of efficiency balanced two dimensional access [J]. Acta electronica sinica, 2016, 44(1): 33?38.

[11] Texas Instruments Incorporated. TMS320C6678 memory access performance [EB/OL]. [2011?03?14]. http;//www.ti.com.cn/cn/lit/er/sprz334h/sprz334h.pdf.

[12] Texas Instruments Incorporated. Keystone architecture DDR3 memory controller [EB/OL]. [2015?10?12]. http;//www.ti.com.cn/product/cn/tms320c6678.

[13] Texas Instruments Incorporated. Keystone architecture enhanced direct memory access (EDMA3) controller [EB/OL]. [2015?11?03]. http;//www.ti.com.cn/product/cn/66AK2H14/datasheet/2?ZHCSBT2G#SPRS864C_002a.