多余度飞控计算机“飞控一次”故障机理分析

崔展博,焦梅素,王德辉,汪 浩,高云红

(1.石家庄海山航空电子科技有限公司 工程技术部,石家庄 050200;2.沈阳航空航天大学 自动化学院,沈阳110136)

随着计算机技术和航电系统的快速发展,飞机的飞行控制系统大都采用数字式飞行控制系统。为了保证飞行安全,余度技术可以有效地提高飞控计算机系统的可靠性和容错能力[1],系统的可靠性要求很高,采用余度技术可以从根本上提高系统的容错性与残存能力[2]。余度技术的核心部件飞控计算机(FLCC)大都采用多余度数字飞行控制计算机,飞控系统各通道计算机之间采取交叉对比表决的方式,工作方式采用热备份[3],具有确保故障安全的能力[4],在一定条件下可实现故障工作或故障降级工作[5],从而保证了系统的安全性与可靠性[6]。另一方面,多余度数字飞控计算机可实现在线检测飞控系统功能、发现故障及隔离故障部件的功能[7]。

在系统进行余度管理时[8],飞机的控制算法对飞行安全十分重要,首先需要完成的工作就是机载多台飞控计算机(工作在同一拍中进行)之间的同步[9]。在当前国内外的FLCC中[10],计算机的工作方式有同步工作方式和异步工作方式两种。同步工作方式时多个计算机同时采集传感器数据[11],多台计算机的采样与控制不能够统一,也许A 机发送上一拍的控制程序,而C 机正在采样下一拍的数据。同时进行控制算法计算、并同时输出计算结果给飞机的作动系统[12],当多个计算机均无故障时不会有输出不一致现象,而如果多余度计算机异步工作或同步则会带来不同计算机通道逻辑运算走不同支路以及输出指令的差异较大、稳定储备降低等问题[13]。外场陆续有飞行过程中报“飞控一次”故障的某飞控计算机(地面BIT检测合格)进行返修[14]。本文讨论某型飞控计算机外场空中“飞控一次”的故障概述、故障原因、故障机理、更改方案及处理措施等。通过外场提供反馈,通讯故障及同步故障适用于与上述故障类型相同的某型飞控计算机或该系统改进型飞控计算机产品[15]。

1 余度飞控计算机同步运行方式概述

同步算法的实现,需要采取标准的同步信号总线,各通道在每一个时刻只与飞控计算机两个RT中的一个进行通讯。正在通讯的RT为“闲”状态,处于热备份的RT为“忙”状态,当正在通讯的RT出现故障可切换到另一个备份的RT,并依次完成“闲”与“忙”及“忙”与“闲”的转换,使用飞控计算机的I /O口来实现这个功能。为了解决较高速度的I /O接口影响主处理机乃至整个飞控计算机性能的问题,多余度飞控计算机采用了局部I /O控制器技术。该I /O控制器按照主处理机的命令完成所有模拟量的A /D转换、飞控计算机各通道之间的交叉数据链路(CCDL)的传输、标准总线通讯及其自检测(BIT)等功能,从而使主处理机有更多的时间进行系统管理和控制律的计算,保证了整机系统的高性能,识别并对故障进行精确定位。

1.1 飞控计算机各通道同步运行的硬件实现

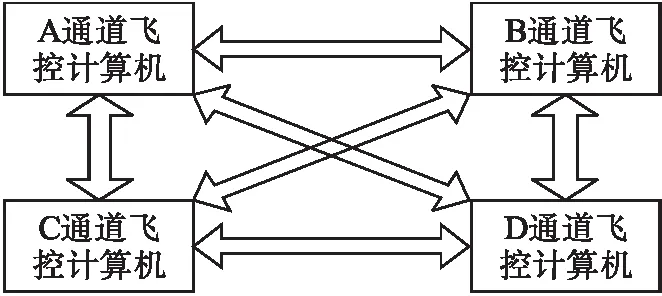

数字式飞行控制计算机经驱动完成后,按照飞行控制软件(包括操作系统调度软件及其控制律计算等应用软件)的指令,完成增稳、控制增稳及自动驾驶仪等功能,图1所示为实现同步算法的硬件连线。本文以三或四通道为例,说明飞控计算机作为飞行控制系统的核心部件与系统中的各种传感器部件、执行机构等进行交联,并能达到一次故障工作、二次故障安全的故障容限等级。多台飞控计算机用以下方式进行连接(本文以三或四余度为例说明),即一台飞控计算机输出同步信号给其他几台,并接收其他几台计算机的同步输出信号,进行握手协议,这样同步的硬件就可以实现了,下面就可以用软件实现同步算法了。

1.2 余度管理模式

余度管理的基本功能是检测飞控系统中的故障及隔离故障部件通过监控和表决余度信号来实现。系统内所有余度通道采用了相同的工作程序,即采用了相同的输入、相同的处理和计算、相同的输出。通道间同步信号连接如图1所示。

图1 通道间同步信号连接图

余度管理是保证余度系统完整性,确保飞行安全并顺利完成任务的关键。传感器及机上部件的信号(模拟、离散、数字)输出处及飞控计算机输出指令处都要进行余度管理。余度管理是在计算机内设一个伺服器模型与实物伺服器输出进行比较监控;平尾和副翼通道的伺服器监控则由液压监控阀实现。监控功能应向表决器提供有关信号的可用性以及在表决算法中应使用的输入信号等信息。在全部同名输入信号均已被认为发生永久故障的情况下,监控功能应根据信号的性质与作用,按不同的算法处理(申报合适的故障或不申报故障)或命令表决器输送不同的故障安全值。

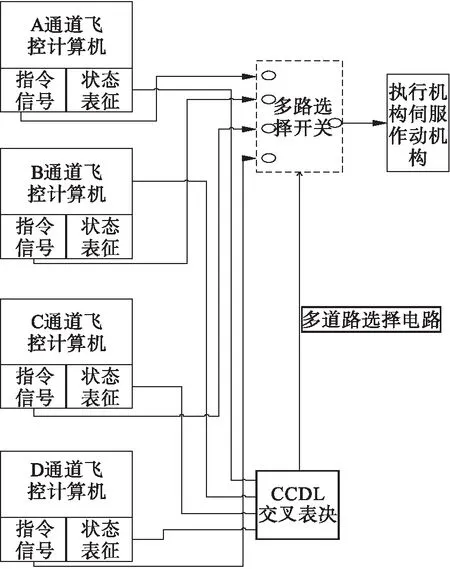

输入信号监控用于对全部三余度信号与二余度信号进行监控,在信号发生永久故障的情况下,监控算法将进行重构以保证在监控算法中不再包含已经发生永久故障的信号(多余度表决线路硬件框架如图2 所示)。

图2 多余度表决线路硬件框架

2 飞控计算机各通道同步运行的流程分析

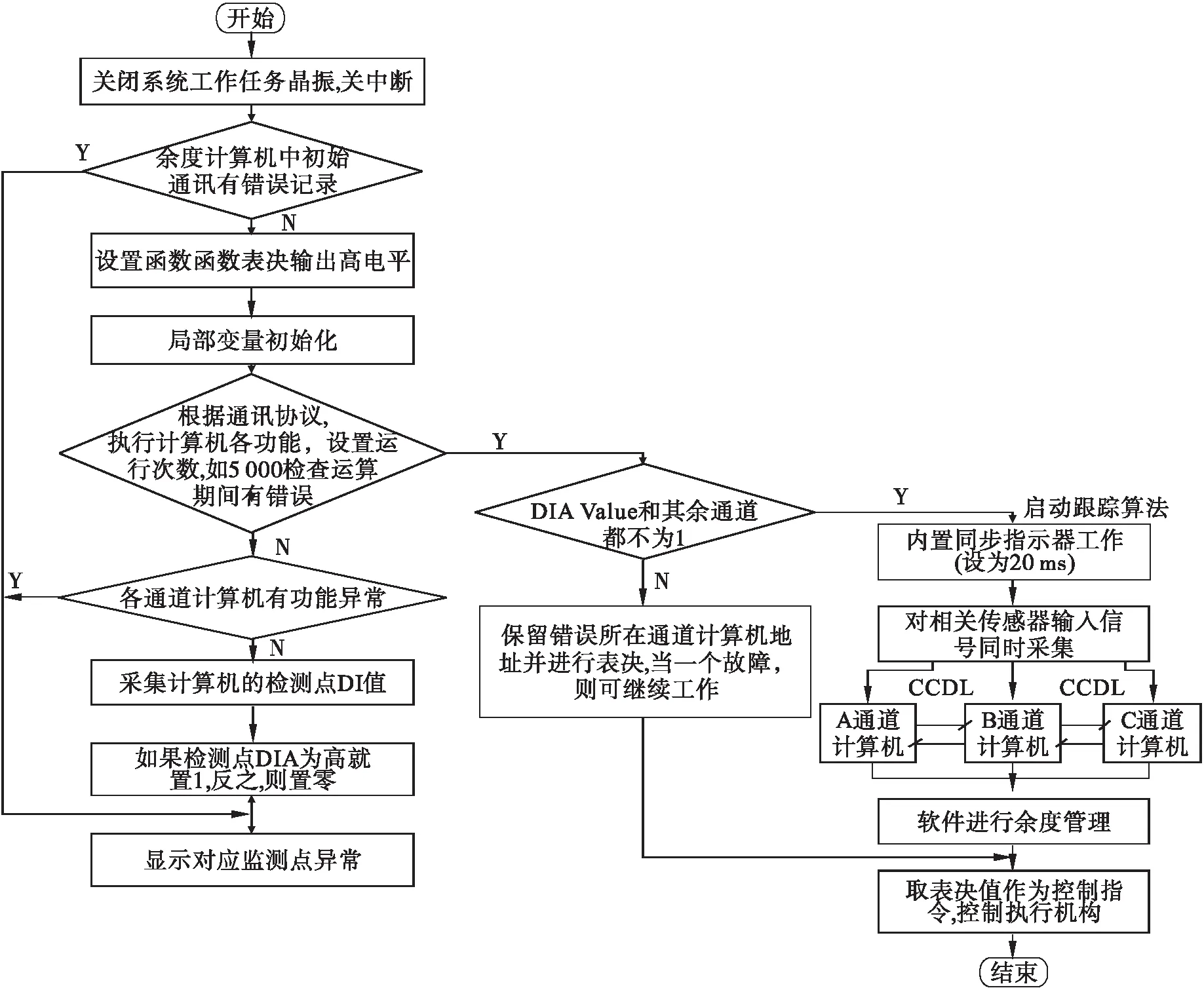

数字式飞行控制系统所有功能的实现均依赖于系统软件正确可靠的运行(同步算法流程图如图3所示)。飞控系统软件分别驻留在飞行控制计算机中,通道间的异步度限制在50ms之内,系统软件与硬件一起协调工作实现系统的控制与稳定。计算机加电或复位后由跳转指令引导而进入系统启动程序,当第一次同步即开机同步成功后就进入50 ms任务运行同步,同步等待的时间为50 ms。软件完成计算机初始化管理、余度管理的初始化,若在同步等待时间内没有收到同步信号,则系统延时一拍启动同步恢复进行计算机加电BIT测试,同步恢复的时间为51ms,大于最小监控周期50 ms。若同步恢复成功则进入50 ms任务并等待下一次同步。若同步恢复也失败则记录同步永久故障,该通道停止输出进入死循环。此时系统已经降级为二余度系统,若再次出现同步失败则双通道同时进入同步恢复,而后依据输入的有关信号进行地面和空中的任务模块转换调度。

图3 同步运行算法流程

3 问题机理分析

3.1 问题概述

外场反馈,某型飞机飞控计算机在飞行过程中会报“飞控一次”故障,故障计算机返回后,课题组结合经验对故障产品进行多项环境试验,故障复现的同时对该典型故障做了机理分析。

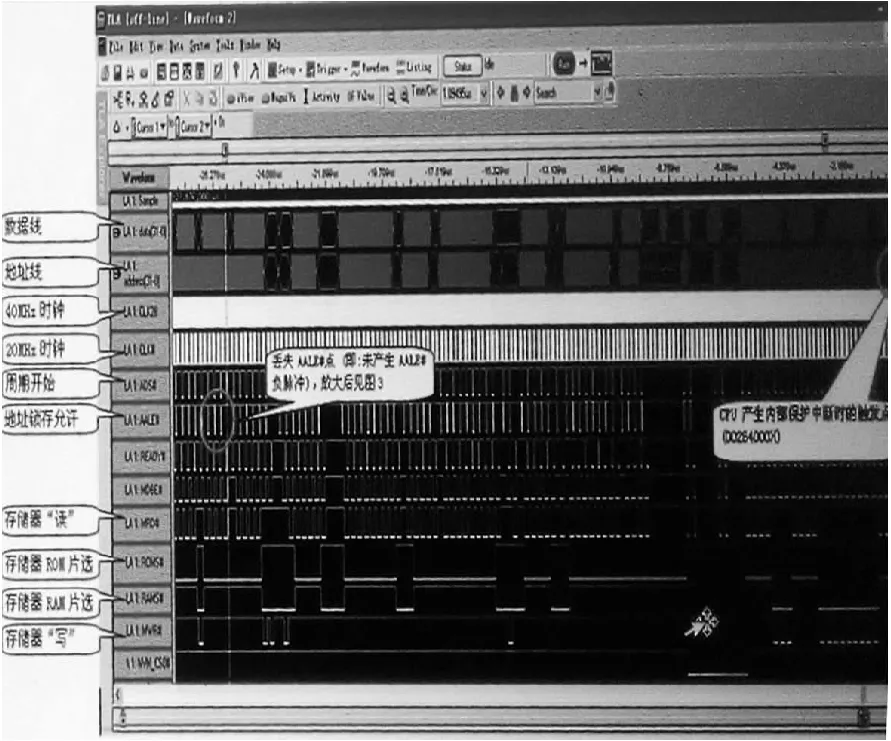

故障现象:在温度循环测试时,某通道计算机报“飞控一次”故障,课题组借助逻辑分析仪,通过系统设备串口数据发现CPU进0D中断,读取故障计算机NVRAM区信息。通过逻辑分析仪采集波形分析,当逻辑分析仪采集触发时,从触发点向前找,发现前面的地址锁存信号个别丢失,造成CPU访问的存储器地址空间片选信号无效,使得CPU模块的读/写数据不正确,从而造成飞控计算机“飞控一次”故障(采集的波形如图4)。

图4 飞控计算机“飞控一次”故障采集的波形

3.2 同步运行过程中片选负脉冲信号分析

此处片选信号的主要作用是在机上测试通讯传输,负责各并行通道计算机之间的回绕传输以测试飞控计算机的通讯状态,当某一通道计算机的输入信号(如晶振产生的起振频率)异常,会导致RT终端得到错误信息,通讯会产生异常。再通过J-K触发器(54F109)分频为20MHz(CLK#,周期50ns)提供给CPU(80486DX)和可编程逻辑器件CPLD使用,并通过CPLD的逻辑译码产生片选信号。

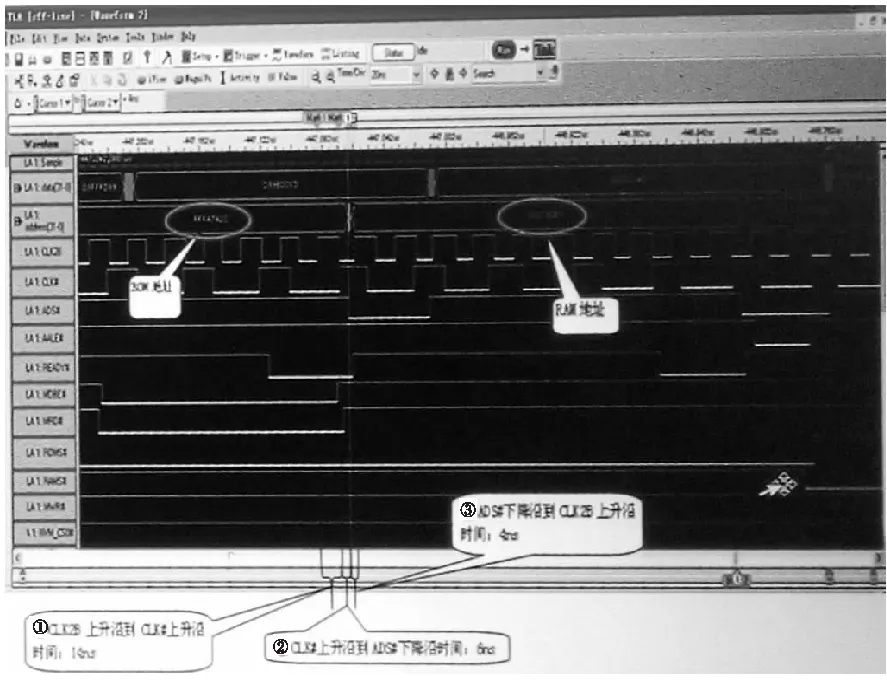

图5 丢失片选负脉冲信号原因分析图

3.3 丢失片选负脉冲信号原因分析

用逻辑分析仪采集到的丢失的片选信号波形如图5所示。由于片选负脉冲信号的丢失造成CPU访问存储器地址空间时的片选及读/写(MRD#/MWR#)信号无效,CPU的读/写数据不正确,造成CPU执行指令错误产生了内部保护性中断,即0D中断。造成丢失片选负脉冲信号的原因分析如下。

(1)通过对图5的分析,发现图5中③位置ADS#下降沿到CLK2B上升沿时间为4ns,当这段时间较小时,CLK2B上升沿时无法采集到需要的高电平信号(高电平信号的逻辑:ADS#信号反向“逻辑与”CLK#信号,即~ADS# & CLK#),从而无法产生片选负脉冲信号;

(2)结合片选信号产生原理,可以得出图5中①位置的时间取决于不同批次J-K触发器器件(F109)的参数,图5中②位置的时间取决于不同批次CPU处理器(80486DX)的参数;

(3)通过上述(1)和(2)的分析,认为给出的时间余量偏小是造成片选负脉冲信号丢失的原因。

3.4 对比分析

鉴于目前2008年前生产的某型飞控计算机未发现报“飞控一次”故障的情况,我们采用对比分析的方法,采集2008年前生产的CPU板上片选信号。

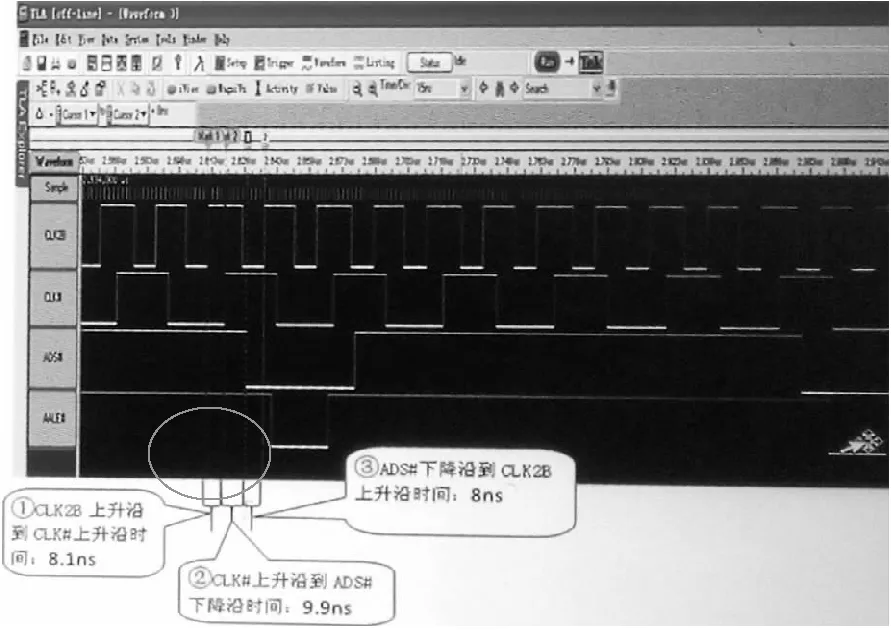

(1)用同样型号的逻辑分析仪采集CPU板上的CLK2B、CLK#、ADS#和片选信号,采集的波形如图6所示。

(2)通过图4和图5的对比分析,发现由于相关器件不同批次的参数的差异造成了ADS#下降沿到CLK2B上升沿之间时间的余量不同。当ADS#下降沿到CLK2B上升沿之间时间处于临界点时无法产生片选负脉冲信号。

图6 CPU板CLK2B、CLK#、ADS#和片选信号采集图

3.5 纠正措施及验证情况

(1)纠正措施

通过上述故障分析,对可编程逻辑器件CPLD内的逻辑进行优化设计,由于CLK2B为25ns的时钟周期,定时发送的周期设置为50ns的负脉冲有效信号,这样在CLK2B上升沿至少可以采到一个ADS#的低电平,从而保证了ADS#信号经过CLK2B上升沿两次同步锁存处理综合后产生的片选负脉冲信号(25ns负脉冲)不会丢失。

(2)验证情况

首先将一套计算机中的一台计算机写入原来逻辑,将另两台计算机写入更改后的新逻辑,进行高低温试验。一台计算机报“飞控一次”故障,再将第二台计算机的逻辑改成新逻辑试验进行三个温循试验,故障不复现;又将第二台计算机的逻辑改成原来的逻辑,在高温时故障常在并且每次关电后再开电故障很快复现。这时候将逻辑改成新版逻辑故障消失,再改成原逻辑故障复现,重复五次现象一致。将第二台计算机的逻辑改成新逻辑后(三台都为新逻辑)经过一天试验故障不复现。

(3)举一反三情况

对某型飞控计算机其它板组件逻辑进行清查,未发现有类似情况。

4 结论

多余度飞控计算机运行方式的评估与确认是一项重要的工作,某型飞控计算机CPU板逻辑地址信号给出的时间余量偏小及器件参数变化是造成片选负脉冲信号丢失的原因。本文通过具体实例的软硬件设计,针对外场报“飞控一次”的故障机理,给出了一种余度飞控计算机排故的可行性思路,片选负脉冲信号丢失是造成外场飞控计算机报“飞控一次”的原因。该方法例证了多余度飞控计算机各通道采样时刻可以略有不同,即各通道采样值必须表决后送给模拟输入信号板做相应处理,这是余度计算机排故的理论基础,而通过对CPU板逻辑的优化,可排除因此造成的飞控计算机报“飞控一次”的故障,为飞控系统余度计算机的排故提供了借鉴。