基于FPGA的AES加密算法设计与实现

摘 要:通过分析高级加密标准(AES)算法的原理及其优越性,结合FPGA高度处理的特点,提出一种基于FPGA的AES加密算法实现方案。采用了查找表方法优化了字节替代变换、列混合变换和密钥扩展模块,将设计的固核运行在Altera公司的Cyclone II FPGA芯片上,利用2块DE2硬件板和2台计算机搭建了一个AES加密文件传输平台,最后分析了设计的器件资源消耗和吞吐率,验证设计方案的可行性。

关键词:FPGA;查找表;AES;Verilog HDL

当前信息技术快速发展,用户对信息的采集、存储和传输的安全性能也逐渐提升要求。利用数据加密算法,对数据进行加密来保障信息传输与存储的安全性则是有效地解决方法,而高级加密标准AES则是很好选择[1]。本文给出的设计方案主要包括:系统整体结构、AES加解密模块、控制模块等部分。

1 AES加密算法原理

AES加密过程是在一个4x4的位元组矩阵上,此矩阵是一个明文分组区块。其中128位(bit)明文分为4列。密鑰的长度包括:128、196以及256位。矩阵列数包括:4、6以及8列。AES算法为密钥迭代分组算法,包含轮函数对state的重复作用。轮数大小取决于密钥长度[2]。

AES解密过程和加密过程互为逆运算,解密过程主要包含四个方面:逆行移位、逆字节替换、轮密钥加以及逆列混合。AES加密需要Nb个字节的初始密钥及Nr轮迭代过程所需轮密钥,所以密钥生成算法需将初始密钥扩展为Nb(Nr+1)个字。

2 AES加密算法建模与设计

系统整体结构主要包括:接口模块、AES加解密模块、串并转换和并串转换模块以及LCD显示模块。通过硬件平台DE2的开关来选择工作模式,LCD显示屏显示系统“Mode:Encryption或Decryption”。计算机通过串口将数据发送到DE2,接口模块收到数据后送到串并转换模块,处理后将数据发送到AES加解密模块,根据模式选择将数据送到相应模块,完成加密或者加密后将数据发送到并串转换模块,然后将数据发送到接口模块完成数据加密或解密。

2.1 AES加解密模块设计

AES加解密模块主要包括:AES加密模块、AES解密模块、控制模块以及密钥扩展模块。内部电路信号中,clk表示时钟输入信号,rst_n表示复位信号,mod表示加解密模式选择信号,kld表示密钥读取信号,ld表示明文(或密文)读取信号。text[127:0]表示待加密(或解密)输入数据,text_out[127:0]表示密文(明文)输出数据。

2.2 控制模块设计

控制模块外部信号中,mod开关量表示系统的工作模式,包括加密模式和解密模式。当信号text_ready有效时,数据text[127:0]发送到text_in,并且分别将信号Encryption_ld和信号Decryption_kld置为有效,并维持一个时钟周期时间。

3 AES加密算法的仿真与实现

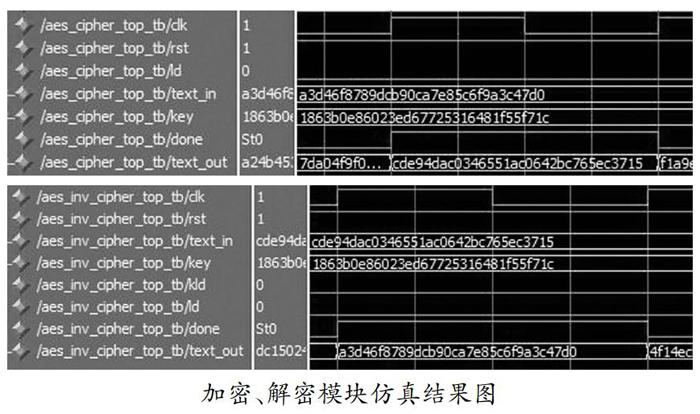

加密模块、解密模块仿真结果如右图所示,加密模块:要求输入的明文和密钥都是128位。当采样到ld有效时,读取明文和密钥;按要求进行加密,加密后done置为有效,输出密文,仿真结果如下:

明文:a3d46f8789dcb90ca7e85c6f9a3c47d0;

密钥为:863b0e86023ed67725316481f55f71c;

输出密文:cde94dac0346551ac0642bc765ec3715。

加密、解密模块仿真结果图

解密模块:要求输入的密文和密钥都是128位。当采样到kld有效,读取密钥;当采样到ld有效时,读取密文;按算法要求进行解密,当解密完成后done置为有效,输出明文。

密文为:cde94dac0346551ac0642bc765ec3715;

密钥为:863b0e86023ed67725316481f55f71c;

则输出明文:a3d46f8789dcb90ca7e85c6f9a3c47d0。

三组明文、密钥、加密结果和解密结果的硬件测试结果如下:

(1)明文:a3d46f8789dcb90ca7e85c6f9a3c47d0;

密钥:1863b0e86023ed67725316481f55f71c;

加密结果:cde94dac0346551ac0642bc765ec3715;

解密结果:a3d46f8789dcb90ca7e85c6f9a3c47d0;

(2)明文:00112233445566778899aabbccddeeff;

密钥:1863b0e86023ed67725316481f55f71c;

加密结果:6c52bc02ddc6f0d2b557578cdcc2a40c;

解密结果:00112233445566778899aabbccddeeff;

(3)明文:d6bc83b3539442fca4ef95fb4cc1b5e0;

密钥:1863b0e86023ed67725316481f55f71c;

加密结果:2cb1b53a002dca6bdd1da38d9b6f572d;

解密结果:d6bc83b3539442fca4ef95fb4cc1b5e0。

4 结语

本文分析了AES算法工作原理和实现设计方案的关键问题,包括系统整体结构、AES加解密模块、控制模块等,整个设计基于QuartusⅡ开发平台,采用Verilog硬件描述语言进行了仿真和分析,在EP2C35F672C6器件进行硬件实现,验证设计方案的可行性。该设计方案具有一定的扩展性,通过修改软件程序,即可以适应密钥长度为192和256位的AES加密算法。

参考文献:

[1]刘晗嘉.AES加密算法IP核的设计与验证[D].上海:上海交通大学,2009,1.

[2]杨波.现代密码学[M].北京:清华大学出版社,2017(第4版).

作者简介:窦贤振(1987-),男,汉族,硕士,研究方向:电子信息工程,物联网应用技术。