高速模数转换器RHF1201测试技术研究∗

许伟达 徐导进 刘 伟 潘潇雨

(上海精密计量测试研究所 上海 201109)

1 引言

对AD转换器性能进行准确的测试,在确保产品质量和可靠性方面有重要作用,特别在军事和航天型号中,集成电路严格的检测和筛选过程,对于控制质量、保障型号装备的可靠性至关重要。

本文介绍了高速模数转换器RHF1201特性,用Teradyne公司MicroFlex测试系统设计的测试方法,以及测试开发过程中处理问题的方法。

2 RHF1201概述及特性

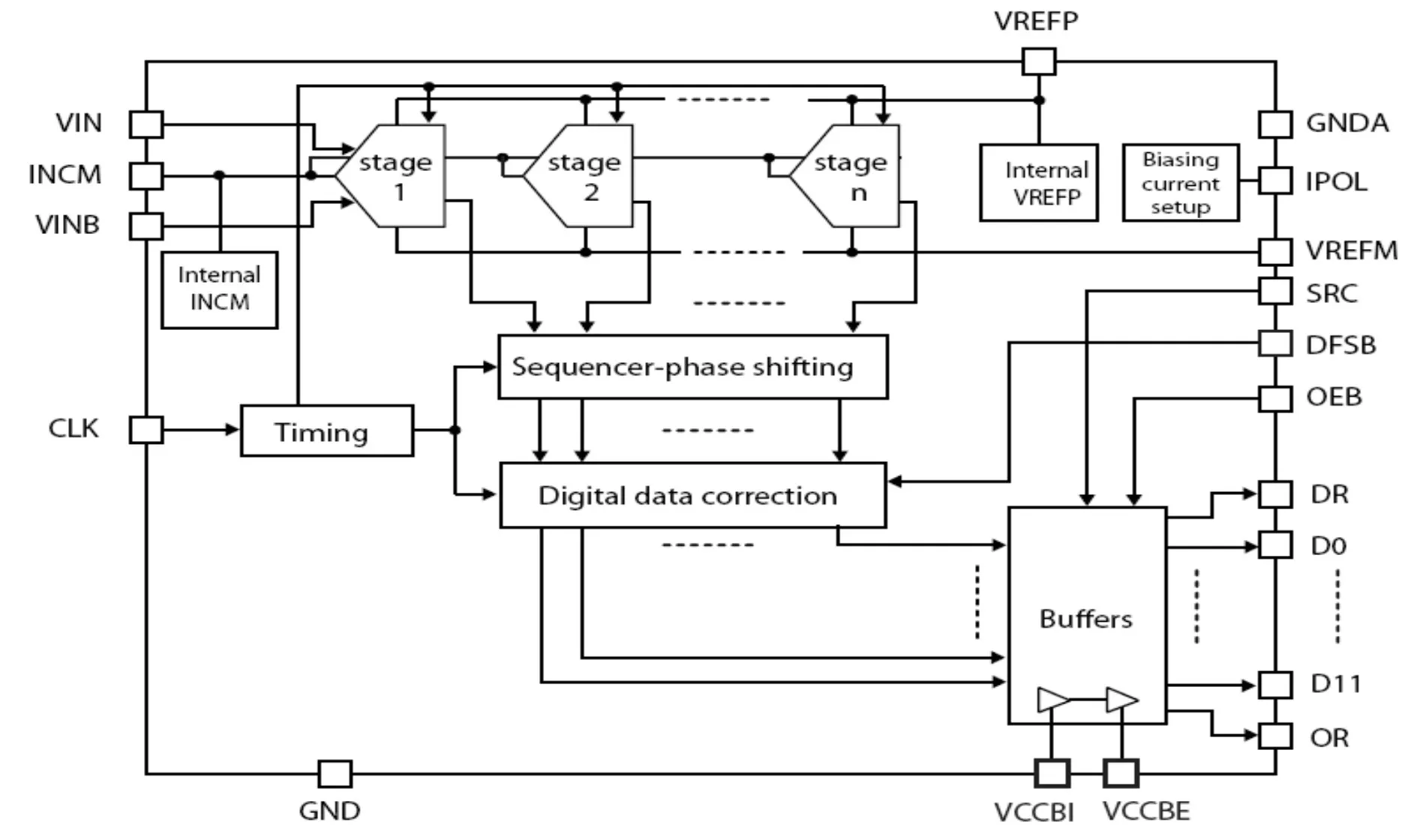

RHF1201是一款12位,采样速率高达50Msps模数转换器,采用CMOS技术0.25μm工艺的高性能,低功耗模数转换器。器件基于流线结构内部提供数字错误纠正技术保证杰出的静态线性度。特别设计优化速度与功耗比。内部集成了含IP的跟踪保持结构使中频采样应用高达150MHz。器件内部提供电压基准,简化外围电路,三态结构使数字输出总线可以共享。输出编码提供二种格式,方便用户选择。当输出数据有效时Data Ready信号可用作系统同步。

图1 RHF1201框图

RHF1201的特性:

1)抗辐照:300kRad(Si)TID;

2)Qml-V认证;

3)在2.7V电压温度125°下单粒子功能中断和锁定阈值高达120Mev-cm2;

4)采样速率500Ksps时功耗44mW,50Msps时100mW;

5)输入信号15MHz,采样率50Msps,无杂散动态范围SFDR高达75dB;

6)输出数字与2.5V/3.3V逻辑兼容。

应用于数字通讯卫星,空间数据采集系统,航空仪表,高能物理等。

3 测试设备性能满足性

大规模混合信号测试系统Micro FLEX是由Teradyne公司生产的高精度集成电路测试系统,多用于AD/DA转换器等混合信号器件的测试。它在PC机上用VBT语言编写测试程序,向被测器件提供电信号、数字测试向量和模拟测试波形,自动测量相应输出管脚上的响应,判断器件是否达到规范的功能和性能要求。

本器件是在美国泰瑞达公司高端大规模混合信号测试系统MicroFlex进行测试,该测试利用了以下几个仪表:

集成有20个VI仪表DC30,提供±30V,电流±200mA,通道数及能力都满足本器件模拟电源的要求。

对教育者而言,爱是陪伴,爱是守护。静待花儿慢慢开放,守候参天大树的种子发芽、生长。用爱的胸怀和言行去培育心中有爱、健康向善的学生,这是我们的责任。

集成有4个VI仪表DC90,提供±90V,电流±2A,通道数及能力都满足本器件数字电源的要求。并能够隔离模拟电源与数字电源的相互干扰。

具有2个15MHz任意波信号发生器、2个15MHz波形数字化仪的BBAC中低频交流信号仪表;本器件测试用到任意波信号发生器15MHz的极限值,对比15MHz正弦波性能基本与器件性能相当,线路中间不能引入任何噪声。

具有数据速率高达200MHz、每仪表48个通道的HSD200仪表,表面上满足本器件测试所需要的通道数及性能,最重要的是数字通道能否作为本器件的时钟源,这个也是本器件测试开发成功的关键。

4 模数转换器RHF1201的测试方法设计

针对RHF1201这样的高速模数转换器电路,需要在50Msps采样率下测试输入15MHz正弦波的动态指标信噪比,全谐波失真,无杂散动态范围,信号与噪声及谐波比,有效数据位。

4.1 时钟源选择

时钟源是高速ADC测试中最为重要的因素。由于ADC采样过程中需要持续抓大量数据,采样时钟需要保持在每次采样过程中上升沿或下降沿足够稳定。时钟信号的定时精度会直接影响高速ADC的动态性能,为了将这种影响最小化,ADC的时钟源必须具有很低的定时抖动或相位噪声[1,8~10]。如果在选择时钟信号时没有考虑该因素,可能根本测量不到正确的动态指标。理想时钟总能在电平跳变之间保持精确的时间间隔,而在实际中,时钟边沿之间的时间间隔是不断变化的,这一定时的不确定性结果,会使被采样波形的信噪比随数据转换过程降低。

针对高速ADC测试是一项更具挑战性的工作,其中采样时钟的Jitter是必须面对的技术难点,随着输入信号和采样频率的增大,ADC的采样时钟所携带的Jitter,在很大程度上影响到测试结果,使之成为一项很艰难的工作。这中间有两个重要的关系需要考虑,第一个重要的关系见图2的推导。

图2 抖动Jitter与噪声Noise之间的关系[3,6]

时钟Jitter并不是高速ADC性能的唯一限制。需要考虑的第二个重要的关系是ADC的分辨率与信噪比之间的关系。

4.2 输入信号源

测试高速ADC,输入信号的“纯度”会影响数字输出的性能。输入信号中的耦合噪声将转换为输出信号数字噪声,如果输入信号中有太多噪声和失真,ADC性能实际上会被测试条件所掩盖。输入信号的精度和纯度最终取决于器件的转换分辨率,一般来说测试设备的精度要比被测器件高10倍以上。另外可以考虑在输入端使用滤波器,除去输入信号之外的噪声和失真。信号发生器还需要生成多种频率叠加的信号用来完成ADC的多频率分辨相关的测试。同时为了保证测试结果的准确度,该高速信号发生器需要有远超待测试芯片的带宽和极低的本地噪声指标[1~2,8~10]。

RHF1201器件测试动态参数已经用到模拟仪表BBAC的极限,必须非常合理安排动态指标测试的每一步:

第一,如何产生高质量正弦波;本身信号频率要求高达15MHz,在本案例中每个周期尽量多采用采样点,提高输入信号的质量。

第二,如何按照Fs/Ft=N/M公式选择具体值,保证频谱不泄漏,采样周期必须是整数要求。被测信号15MHz频率是固定,采样频率50Msps也是固定不能变的。

第三,如何改善输入信号通路的质量,直流耦合、交流耦合、输入引脚之间加跨接电容、输入端增加50Ω抗匹配电阻。经过反复试验,交流耦合比直流耦合可以提高2dB~3dB,输出差分脚之间的跨接电容,根据输出频率要求适当调整。

4.3 数字管脚信号处理

RHF1201器件测试首先是如何让器件正常工作。RHF1201是高速模数转换器,速度高达50Msps,如果器件输出信号引脚直接连接到数字仪表HSD200,数字仪表读不到正常数据,必须要采用50Ω阻抗匹配。否则输出数字由于信号反射原因而毫无规律。原理见图5。

图3 数字通道50Ω阻抗终端示意图

输入模拟信号能够正常转换后产生输出对应的数码。并且用实验反复测试,其结果与分析的一致。

4.4 噪声抑制的处理

减小系统的噪声引入可以有效地提升动态参数测试的准确度[3~6],常见的方法包括对输入线路做合适的阻抗匹配,Micro FLEX设备的模拟输出端“BBAC Source”可以提供50Ω的阻抗匹配,能有效地提升器件的信噪比,对“BBAC Source”的参考电压端“SRC REF”接地,也对减小噪声,改善信噪比有明显帮助。

4.5 高性能低噪声的测试电路设计

由于数字开关的瞬时变化主要由高频成分构成,趋肤效应告诉我们逻辑变化产生的噪声几乎与地平面铜皮的总质量无关,总表面面积比地平面在总体积更为重要,典型的充满噪声的数字电路与敏感的模拟电路之间的欧化会导致很差的性能,并且会变得无法隔离和补救[4~5]。解决方法是很好地将数字电路与模拟电路分开,由于所有引起的公共回流路径会在ADC的模拟输入“地”中引起涨落,从而在转换结果中引入额外的噪声,因此不应将高功率的数字元器件放在任何线性元器件或模拟与混合元器件的电源线和电源平面之上或附近。

通常模拟和数字引线应成90°交叉,以避免数字噪声进入模拟路径,但是在高频、超高频系统中应完全避免模拟和数字引线90°交叉[11]。输入的时钟线应与所有其它引线(包括模拟和数字)隔离,应该避免通常可被接受的90°交叉。因为在高频下即使少许耦合也会引起问题,在高频下,笔直的信号路径具有最好的性能,模拟输入应与充满噪声的信号引线隔离以避免将寄生信号耦合到输入中去,任何连接在转换器输入端和地面之间的外部元件(例如滤波电容),都应被连接到模拟地平面中一个非常干净的点上,任何模拟电路(输入放大器、滤波等等)都应该与任何数字元器件分开放置。

RHF1201经过最终调试,动态指标测试结果如下:

Number Site Test Name Pin ChannelLow Measured High Force Loc

94 0 SNR -1 59.0000 dB 60.5373 dB N/A 0.0000 0 95 0 THD -1 N/A -67.8839 dB-64.0000 dB 0.0000 0 96 0 SINAD -1 59.0000 dB 60.5373 dB N/A 0.0000 0 97 0 SFDR -1N/A -67.7479 dB-63.0000 dB 0.0000 0 98 0 ENOB -1 9.7000 9.7637 N/A 0.0000 0 按照本文所采用的方法,成功解决了宇航用50Msps采样率高速模数转换器RHF1201的测试,测试结果准确、重复性好。确保该器件是经过严格的检测和筛选,有效控制器件质量、保障型号装备的可靠。5 结语