电荷泵锁相环系统级功耗估计

魏建军 王振愿 陈付龙 刘乃安 李晓辉

摘 要:功耗问题是制约集成电路设计的一个重要因素.分析了CMOS集成电路中功耗的来源,集成电路设计中功耗设计的目的,估算方法和功耗模型.研究模拟集成电路的特点和相应的功耗估计方法.针对采用环形振荡器的电荷泵锁相环,研究电荷泵锁相环的组成,各模块的工作原理及对功耗的贡献,提出了电荷泵锁相环系统级功耗估计模型.与实际测量结果相比,相对误差小于22%.该模型易于植入集成电路设计工具,可以对锁相环系统级设计提供功耗方面的参考,提高集成电路的设计质量.

关键词:功耗估计;功耗模型;能量转移;电荷泵锁相环

中图分类号:TM935 文献标志码:A

Power Estimation of Charge Pump PLL at System Level

WEI Jianjun1,WANG Zhenyuan1,CHEN Fulong2,LIU Naian1,LI Xiaohui1

(1. School of Telecommunications Engineering,Xidian University,Xi'an 710071,China;

2. School of Mathematics and Computer Science,Anhui Normal University,Wuhu 241003,China)

Abstract: Power is an important factor that restricts the design of Integrated Circuit (IC). The power origin in CMOS IC,the aim of power estimation in IC design,the estimation method,and the power model were analyzed. The characteristic of analog integrated circuit and the corresponding way for power estimation were studied. In order to distribute the power at system level, the construction of charge pump PLL,the principle of every module and the contribution to power were also studied. The power estimation model of charge pump PLL with ring oscillator was proposed at system level. The relative error is less than 22% when compared with the actual measurement. This model is easy to be integrated into design tools and can give guidance on power consumption for PLL at system level to improve the quality of Integrated Circuit design.

Key words: power estimation;power model;energy transfer;charge pump PLL

集成電路集成度和时钟频率的大幅度提高,导致功耗问题日益突出,功耗已成为许多ASIC设计中的关键因素之一.但是,由于满足功耗设计需要的EDA软件发展缓慢,设计者不得不在设计后期反复验证以满足功耗特性,延长了产品设计周期,推迟了上市时间.为使功耗设计能溶入集成电路设计方法学,使得设计者在考虑延迟、噪声和芯片面积等因素的同时,也能对功耗进行分析权衡,高层次的功耗估计越来越迫切.电荷泵型锁相环频率综合器是一数模混合系统,大量使用在芯片中,提供精确的时钟或载波信号,虽然占用的面积不大,但功耗却很显著,在芯片系统设计阶段对其进行功耗估计,便于芯片的功耗分配.目前数字集成电路存在较为成熟的功耗估计算法,可以从系统级到晶体管级估计功耗.模拟集成电路功耗估计算法研究很少,主要集中在晶体管级,系统级较少.仅有部分文献针对模拟滤波器和ADC提出了系统级功耗估计算法,而且限制了滤波器的类型[1],本文从系统级提出一种电荷泵锁相环的功耗估计算法,在系统设计阶段提供功耗方面的参考.

1 CMOS集成电路中的功耗

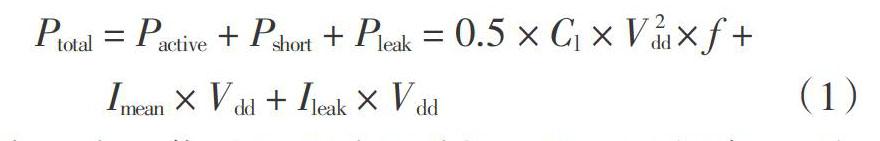

CMOS工艺是集成电路领域最普遍采用的工艺,所实现的电路的功耗由动态功耗和静态功耗组成,来源主要有三个方面: 开关功耗(Pactive)、短路功耗(Pshort)和漏电功耗(Pleak).动态功耗包括开关功耗和短路功耗,静态功耗主要指漏电功耗.

开关功耗是电路的逻辑发生改变时对负载电容的充电/放电而引起的功耗,当CMOS电路进行开关操作时,需对输出节点的负载电容进行充电/放电操作,存在有电流流动,需要消耗能量.短路功耗是由于电路中NMOS和PMOS晶体管同时导通时,从电源端到地的导通电流形成的,功耗的大小与输入信号的上升时间、下降时间、工作频率、负载电容、器件尺寸等有关.优化设计门的尺寸尽可能保证输入、输出信号的上升时间、下降时间相等,短路功耗将小于动态功耗的15%[2].漏电功耗主要由三部分构成:MOS晶体管中源、漏扩散区和体区间所形成pn结的反向电流Ipn;次开启电压下存在的反型电荷形成的亚阈值漏电流Isub;由于薄的栅氧化层导致的栅漏电流Ig.在CMOS器件中,反向pn结偏置电流与亚阈值漏电流均在pA级,在特征尺寸为1 μm的情况下,二极管的泄漏电流一般为1 pA. Ipn正比于源、漏扩散区的面积,主要由制造工艺决定.Isub随着晶体管宽长比的增加而线性增加,随着Vgs-VT的减少而呈指数关系下降.与动态功耗相比,静态功耗的影响较小,但随着深亚微米CMOS工艺的发展,器件的阈值电压越来越低,漏电流的影响不容忽视,限制了工作电压的进一步降低.