FPGA使用之时序处理技巧

姚文达

(中兴通讯股份有限公司,天津 300000)

好的编码风格和习惯不但可以增加代码的可读性,减少fpga的逻辑资源,更能对时序起到非常显著的作用,好的编码风格有很多,我们在这里只举一个小例子——在使用RAM和FIFO的时候,在RAM和FIFO内部都推荐采用对输入信号和输出信号都各打一拍的方法来进行处理,如果在资源效率等条件允许的情况下,还推荐在外部增加一级寄存处理,这样一共加入了三拍处理,输入一拍,输出两拍,这样可以提高整个代码的鲁棒性,即便进行器件移植也不容易导致时序变差。

复位也是容易引起时序问题的一个方面,对于不同厂家的FPGA器件而言,它们所支持的复位策略是不同的,有的器件内部的逻辑资源支持低电平复位和高电平复位两种策略,而Xilinx器件的7系列器件的逻辑资源只支持高电平复位策略。

如果之前采用的是低电平复位方法,即检测复位信号为低时便进行复位,外部输入的低电平复位信号在经过同步化处理之后进入BUFG,然后从BUFG出来的低电平复位信号直接就输出至各个逻辑。这样就可以使复位路径延时很小。但由于Xilinx器件只能支持高电平复位策略,即只能通过检测复位信号为高时才能进行复位,所以当代码未经修改直接移植至Xilinx器件时,低电平复位信号在经过BUFG输出之后,需要进入反向器处理为高电平复位信号之后才能输出至各个逻辑,这样会导致时序变差。将所有逻辑的复位策略均修改为高电平有效复位,将外部输入的低电平复位信号修改在进行同步化至本地处理的时候同步为高电平有效信号,这样输入BUFG的复位信号为高电平有效。这样就可以使走线延时大大减小,从而满足设计要求。所以在代码移植过程中,需要考虑器件的特性,改善复位路径上的时序。

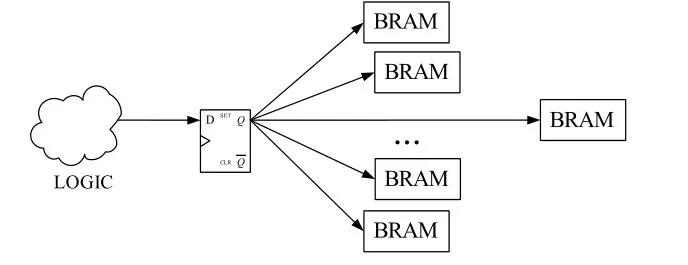

由于BRAM的位置在器件内部相对固定,当FF扇出驱动多个BRAM时,软件会摆放相关的多个BRAM,未必会将此多个BRAM放置在集中的区域,尤其是在BRAM资源占有率很高的时候,这些BRAM的位置会放置比较分散,这样就有可能出现某些BRAM放置的位置离此FF的位置比较远,如图所示,这样在这条路径上就容易出现时序不满足的情况。

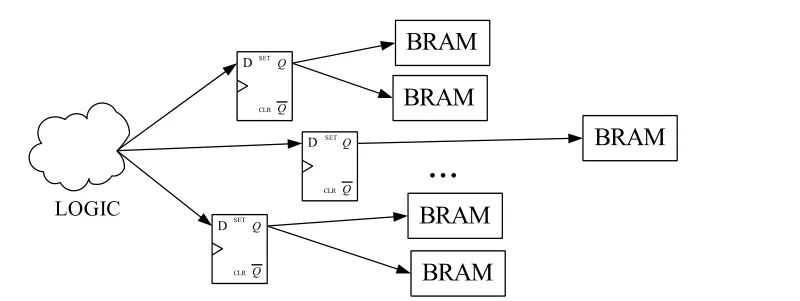

在出现此类问题时候,可以通过减少FF驱动的BRAM数目来解决,即采用复制寄存器的方法将前端的FF进行复制,减少其后端驱动的BRAM数目,如所示。对于某些时钟频率比较高的不容易满足时序的关键路径,推荐一个FF只扇出至一个BRAM的方法,这样可以极大避免出现时序告警的可能性。

除了本文提供的时需优化技巧外,时序的优化需要根据代码的不同情况,在组合逻辑中插入时序以减少时延,从而提高时序余量,加上本文的例子希望刚接触时序的开发者有所帮助。