基于导弹数据链的级联编码的设计与实现*

姜 智,闫智强,马 骏,董诗萌

(西安现代控制技术研究所, 西安 710065)

0 引言

随着导弹武器系统向着智能化方向发展,传统的光纤数据链系统已经不能满足远距离,协同化的需求,因此,基于无线传输的导弹数据链系统得到了越来越广泛的应用。为了改善导弹数据链系统的性能,提升可靠性,文中对导弹数据链系统的信道编码方式进行了研究,设计了一种由RS码、交织技术和卷积码组成的级联编码,并在FPGA芯片上实现,该级联编码能够有效地提升系统的可靠性,保证较低的误码率。

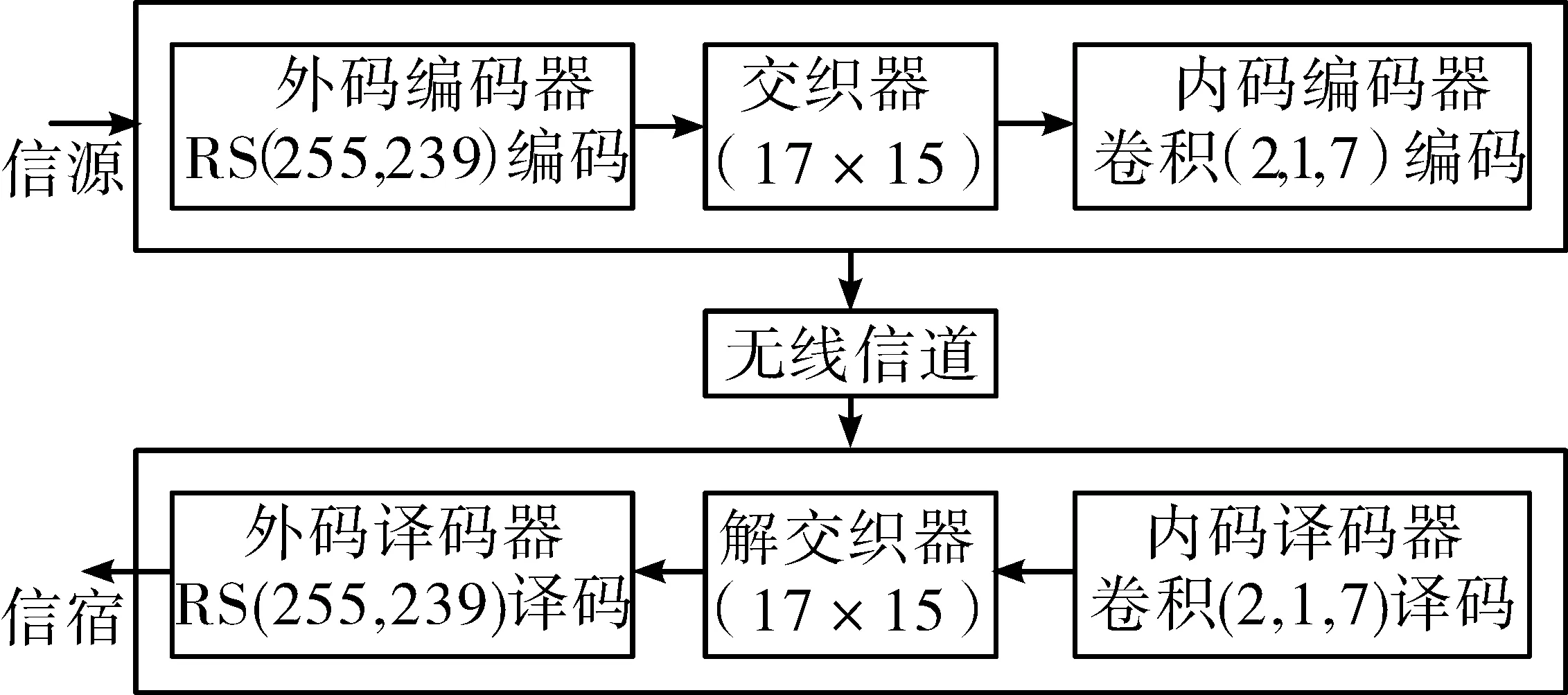

1 级联编码的总体设计

级联编码的总体设计主要包括级联编码的编码器与译码器设计。本设计中的级联编码采用RS(255,239)码、交织(17×15)与卷积码(2,1,7)级联的编码方式。级联编码结构图如图1所示。

图1 级联编码结构图

其中,RS码为非二进制的外码,卷积码为二进制的内码,内码译码与外码译码分别采用软判决译码方法与代数译码方法,外码译码可以将内码译码不能纠正的单比特错误与突发错误转化为外码的单个或多个符号错误,并在外码译码的过程中被进一步纠正,大大的提高了抗误码性能[1]。

2 级联编码编码器的设计与实现

2.1 RS(255,239)编码器设计与实现

RS(255,239)码对信道突发错误有很好的纠错性能,有239个码元,16个监督码元,可检测16个码元错误,纠正8个码元错误。

RS(255,239)码的编码采用循环码常用的多项式触发电路完成。校验多项式为r(x),信息多项式为m(x)时,与生成多项式g(x),三者之间的关系可以表述为:

r(x)=m(x)xn-kmodg(x)

(1)

本设计的RS码的生成多项式采用系数非对称方式,如式(2)所示,可以简化RS译码器的设计。

(2)

本设计中的RS(255,239)码生成的多项式展开对应的系数为:g16=1,g15=59,g14=13,g13=104,g12=189,g11=68,g10=209,g9=30,g8=8,g7=163,g6=65,g5=41,g4=229,g3=98,g2=50,g1=36,g0=59。

RS(255,239)码编码器结构如图2所示,其工作过程如下:首先,将移位寄存器b0至b16的值设为0,门1打开,门2关闭,m(x)每个时钟输入一个字节到

除法电路,同时在输出端输出,作为RS码的信息位;239个时钟周期后,m(x)输出并全部进入除法电路,此时移位寄存器中保留了r(x)的系数,作为RS码的校验位,然后关闭门1,打开门2;在第240至第255时钟周期之间,b0至b16中的值按照时钟周期依次向右移动,经过16个时钟周期后,16个校验符号在239个信息位之后输出完毕,完成一个RS码的编码工作。

图2 RS编码器结构

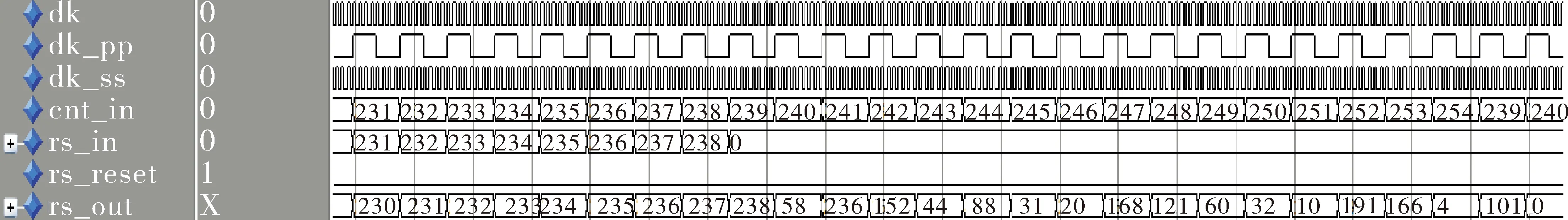

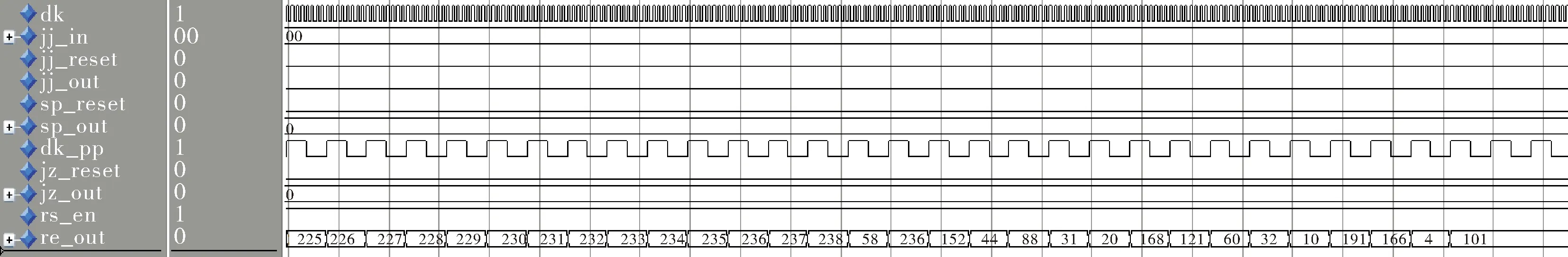

以0~238作为RS码的输入,经过RS编码产生16个校验位,为58,236,152,44,88,31,20,168,121,60,32,10,191,166,4,101。仿真结果如图3所示,rs_in为RS编码器的输入,rs_out作为RS编码器输出端输出数据。

图3 RS编码输出16位校验位仿真

2.2 交织器设计与实现

为了纠正实际信道中产生的较长的突发错误和多个突发错误,常采用交织技术。采用交织能够将连续多个突发错误分散到RS码码字中,使错误相互独立,从而改善RS码对连续多个符号错误的纠错能力[2]。

交织器的工作原理:输入端数据按顺序分别进入B条支路延迟器,第一条支路无延迟,第B条支路有(B-1)乘以M个周期数据延迟。交织器的输出对应各支路经过延迟的数据。卷积交织的每条支路数据的延迟如式(3)所示。

di=(i-1)M×B,(i=1,2,...,B)

(3)

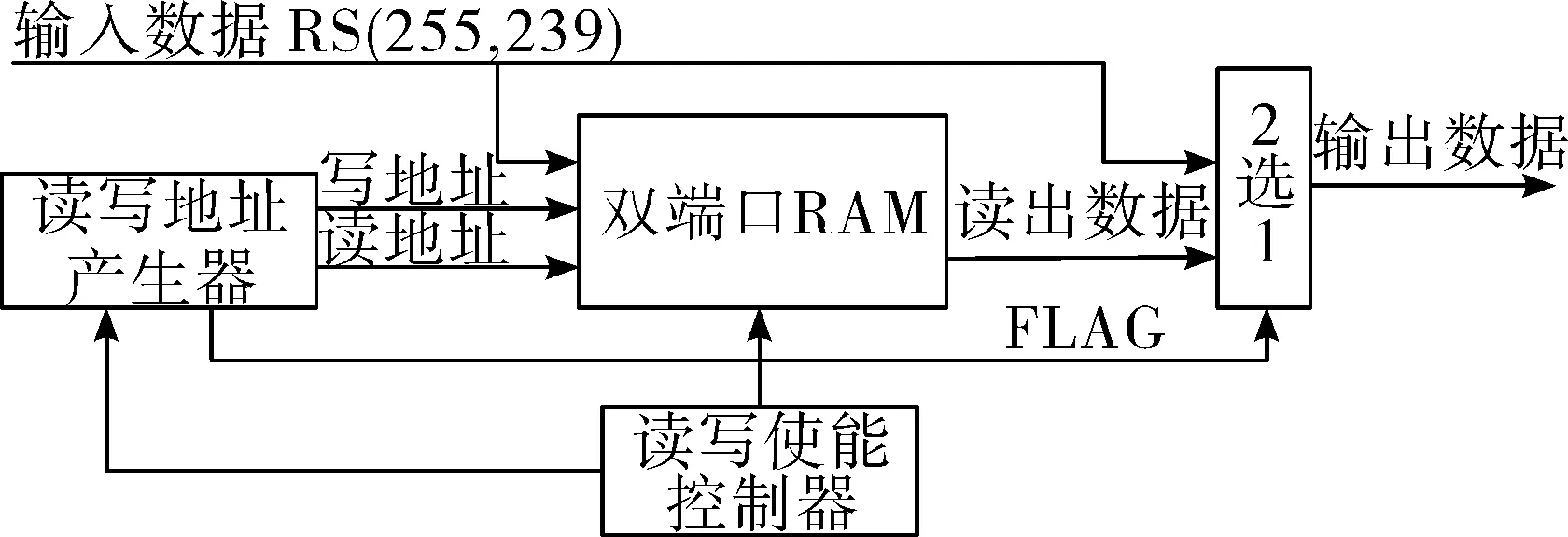

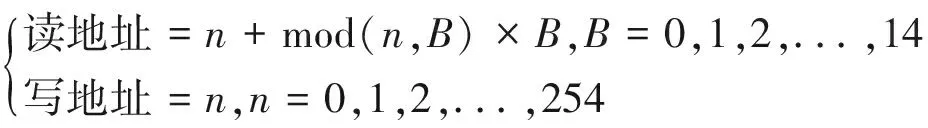

M与B的取值与RS码的码长有关,本设计中,取M×B=255,B=15,M=17。即交织深度为15,可抵抗240个符号周期的突发性差错。本设计采用FPGA的双口RAM来实现卷积交织器。其结构如图4所示。

图4 交织器结构

(4)

双口RAM的读写地址如上式(4)所示。

交织器的输入按照0,1,2, …,254顺序地址存入双口RAM,输出按照地址发生器计算的读地址将数据从双口RAM中读出。

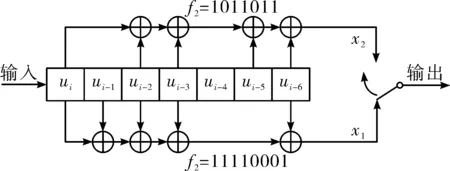

RS编码器的输出rs_out,同时也是交织器的输入,经过交织器后,数据已被打乱,交织仿真结果如图5所示。jz_out的读地址输出数据为0,16,32,…,193,209。

图5 交织器仿真结果

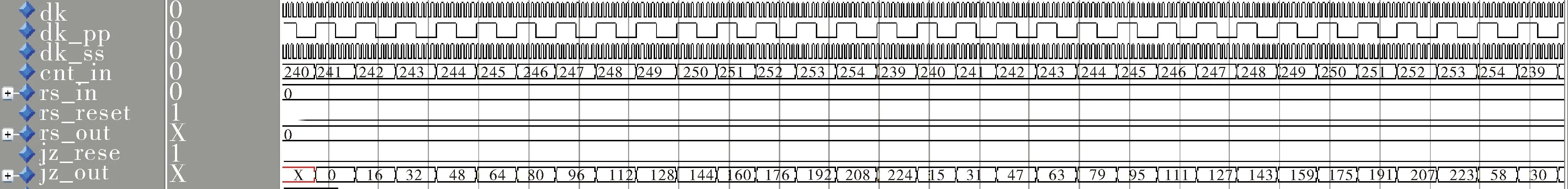

2.3 (2,1,7)卷积码编码器设计与实现

卷积码是一种比较常用的前向纠错编码,(n,k,m)卷积码是n位编码输出,k位信息输入,输出不仅与当前时刻有关,还与之前的(m-1)个分组有关。本设计采用(2,1,7)卷积码作为级联码的内码,卷积码多项式表示如式5。

(5)

卷积码编码器结构可以按照式(5)得到,如图6所示。移位寄存器ui~ui-6存储的是从当前输入值到回溯6个时刻输入值。当下一时刻产生新的输入时,移位寄存器向右移动1位,对应寄存器中的数据经异或计算后按照x1与x2的顺序输出。

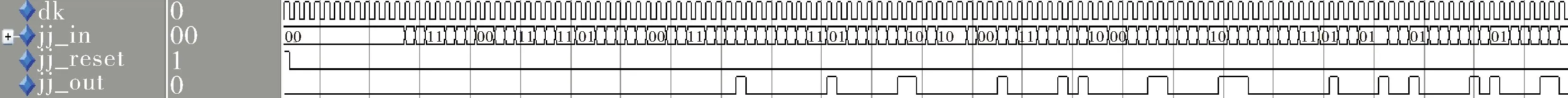

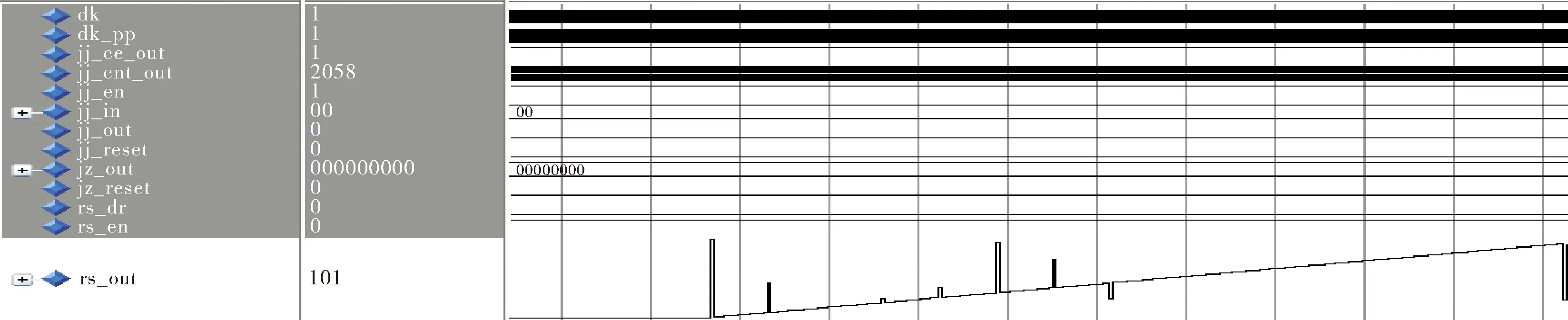

交织器输出的数据为255个字节,而卷积编码器则是按位输入,仿真采用并串转换方式,并串转换后作为卷积码输入,输入为ps_out,共2 040个字符,卷积编码的输出jj_out,输出2 046个字符,每字符为2Bits的二进制数据。仿真结果如图7所示。

图6 (2,1,7)卷积码编码器结构

图7 卷积编码仿真结果

3 级联编码译码器设计与实现

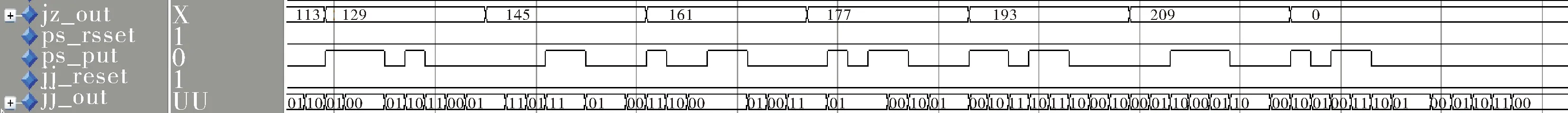

3.1 (2,1,7)卷积码译码器设计与实现

卷积码译码器为采用8电平量化、回溯深度为40的软判决卷积码全并行译码的维特比译码器[3]。维特比译码器整体结构框图如图8所示。由5个译码功能模块组成。

图8 卷积译码结构

各模块功能如下:

1)分支度量模块:将级联编码器输出分别计算和“00”、“01”、“10”、“11”的欧式距离,本设计中为软判决,故输出各分支度量值位宽为2。

2)加比选模块:每次状态更新时,每个状态都可以选择两条候选路径,所以每个状态的路径度量值更新要分别计算两个分支度量和对应路径度量之和,在设计中每次状态更新总共有128条路径,从中选择64条路径更新相应的路径度量值[4]。

3)最小路径度量选择模块:从输入的64个路径度量值寄存器中查找当中的最小值,并记录相应的寄存器位置,并输出到幸存路径管理存储模块。

4)路径回溯模块:加比选模块产生的64个幸存路径寄存器,在当前时刻,由最小路径度量值查找模块得到的路径度量值最小对应的幸存路径寄存器值作为路径回溯模块的输出。

5)控制处理模块:在加比选模块中的路径度量值经过不断累加会产生溢出,控制处理模块为防止出现这种情况。输入为64个路径度量寄存器,输出为修正后的64个路径度量寄存器。

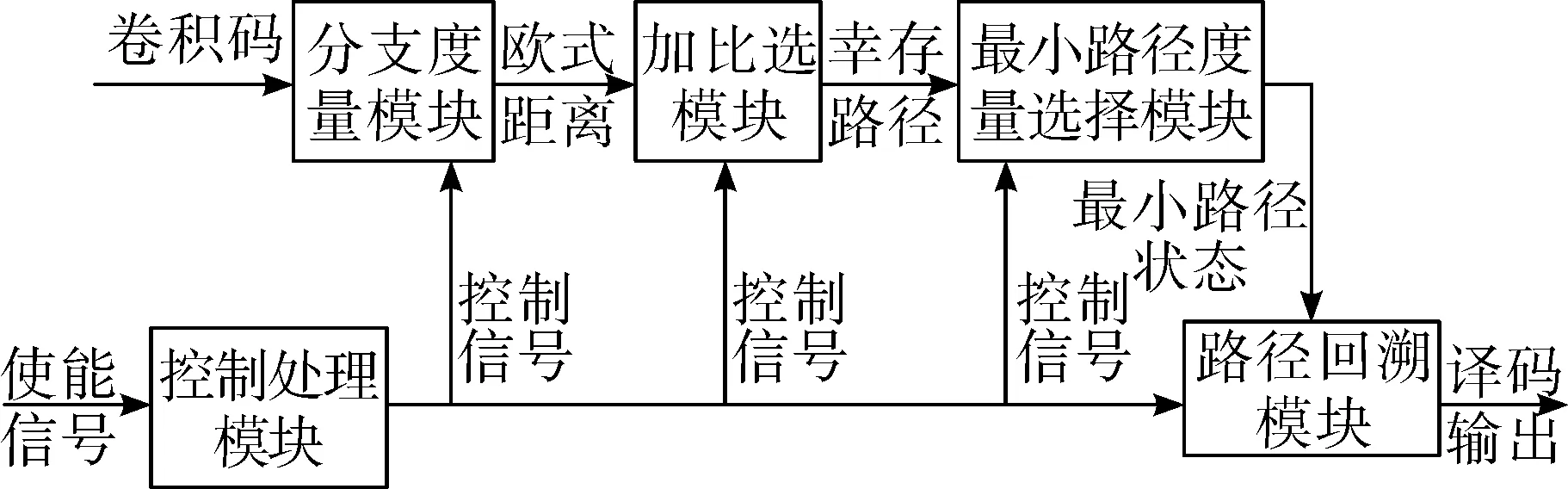

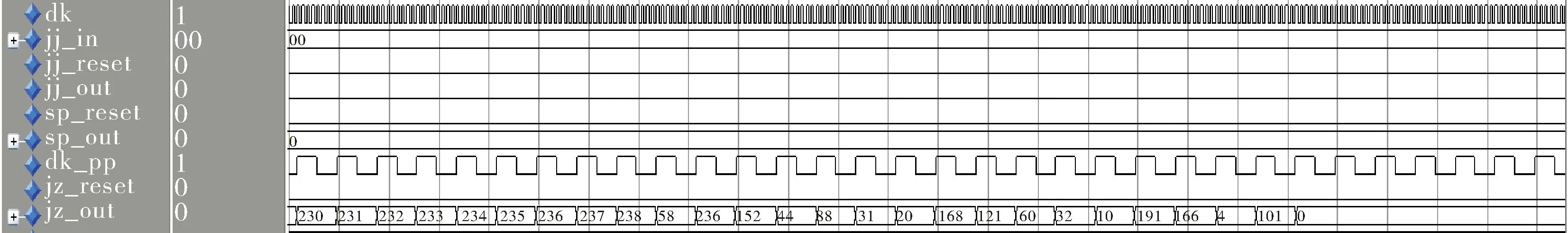

维特比译码器的输入为jj_in,2 046个字符的二进制码流经过维特比译码后产生2 040 bit输出数据jj_out,如图9所示。

图9 维特比译码器仿真输出

3.2 解交织器的设计与实现

解交织器是交织器的逆过程,结构和交织器相同,但双口RAM的读写地址与交织器正好相反,如式(6)所示。

将维特比译码器的输出经过串并转换后作为解交织输入,仿真结果如图10所示。

(6)

输出数据为jz_out,发送端交织器的输入数据的255个二进制数经过解交织器后数据被正确还原。

图10 解交织器仿真输出

3.3 RS(255,239) 译码器设计与实现

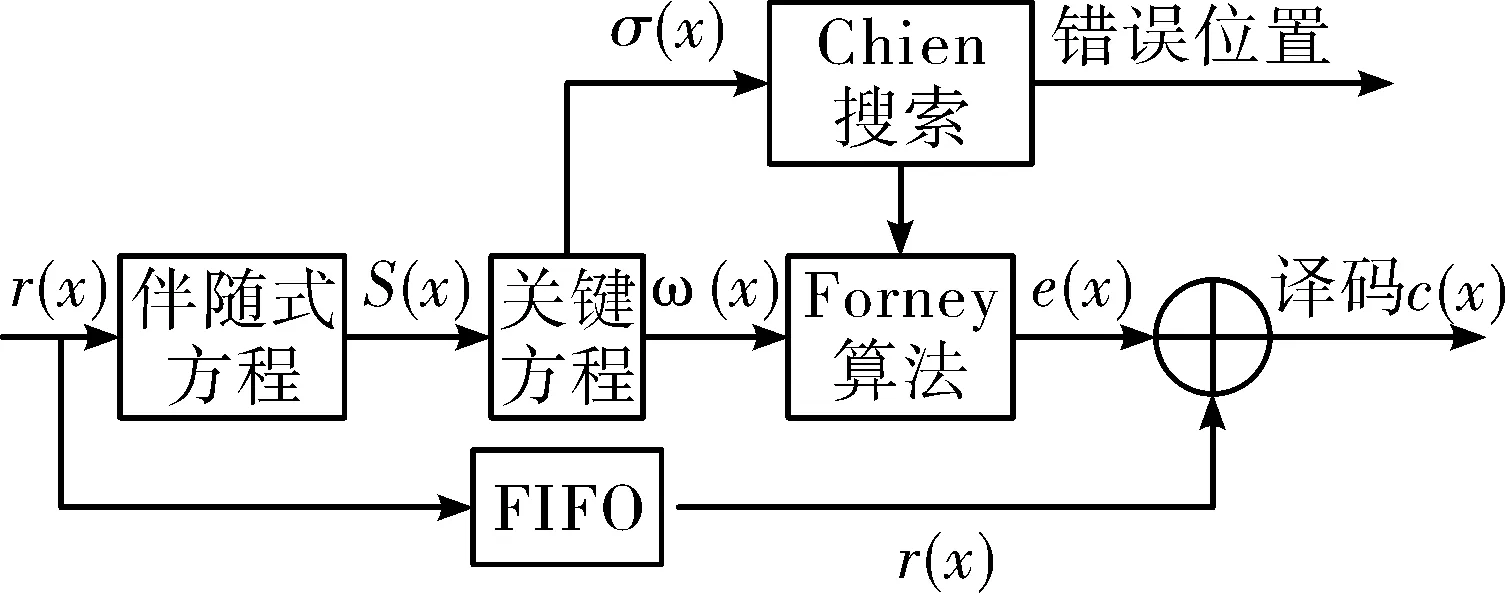

RS码译码就是从接收多项式中找出错误码元的位置和错误值,减去错误图样后得到正确码字[5]。RS译码器整体如图11所示。

图11 RS译码器结构

工作流程为:首先接收多项式r(x)进入伴随多项式模块计算伴随值,构造多项式如式(7)所示(其中t为最大纠正错误字节数,本设计中t=8):

s(x)=s0+s1x+s2x2+…+s(2t-1)x(2t-1)

(7)

解关键方程利用BM迭代算法,依据伴随多项式计算模块的输出,迭代计算得出错误位置多项式σ(x)与错误值多项式ω(x);利用错误位置多项式σ(x),Chien搜索模块找到接收码字多项式的错误位置并在Forney算法模块中计算图样,从而完成对接收码字多项式的纠错,输出正确码字。

解交织器输出的数据jz_out送至RS译码器进行译码,可正确还原出239个信息位和16个校验位,RS码译码输出如图12所示,rs_out为译码器输出。

图12 RS译码器仿真输出

4 级联编码性能仿真及结果分析

级联码编码器输入rs_in的仿真波形,验证时输入的是一组从0到238共239个8位二进制数据,为验证级联编码最大纠错位数,译码器输入一组为2 046个2位二进制数据,改变前140 bit作为信道传输后引起的数据错误,译码器输出的仿真波形如图13所示。

图13 改变前140 bit后译码器输出

可以看出输出的数据rs_out和编码器的输入一致,错误的数据位能够被纠正。图14为改变前142 bit后的译码器输出,可以看出输出的数据rs_out的数据波形和编码器输入不一致,即当信道传输导致数据错误的位数超过140个,级联码不能完全纠正错误。

图14 改变前142 bit后译码器输出

5 结论

由以上仿真结果可以看出,级联编码具有良好的纠错能力,能够纠正140 bit的错误,在导弹数据链系统中对信道编码采用级联编码的方式可以大大降低误码率,提高数据传输的可靠性。