基于AD7732的石英挠性加速度计数据采集系统的设计

杨涛 虞翔 吴海林

摘 要:针对光纤惯性测量单元(IMU)中加速度器件的指标要求,介绍了石英挠性加速度计数据采集系统的设计,设计中采用了高精度的24位Σ-Δ型A/D转换器AD7732和FPGA芯片 EP4CE75U19I7N来完成系统功能,详细描述了硬件电路设计,并对软件设计做了相关介绍。

关键词:石英挠性加速度计;数据采集系统;AD7732;FPGA

中图分类号:TH824.4 文献标识码:A 文章编号:1671-2064(2019)14-0019-03

0 引言

石英撓性加速度计是惯性导航系统中的关键部件,具有精度高、体积小、长期稳定性好、抗干扰能力强的特点,输出与载体的运动加速度成比例的模拟电流信号。导航计算机要求惯性器件的数据必须是数字格式,因此需要通过数据采集电路将加速度计输出的模拟信号转换为数字信号,并且转换后的精度应尽量不损害加速度计原有的精度[1]。为了满足低成本、小型化光纤IMU的市场需求,进行了本方案的设计,其中IMU的外形尺寸为Φ90mm×60mm,质量小于1kg,加速度计量化后的精度小于0.1mg(1s平滑,1σ),测量范围为±15g。为实现该目标,采用了两块电路板,一块电路板实现石英挠性加速度计的采集和数字化,另一块电路板实现光纤陀螺信号的采集处理、加速度计信号的处理以及IMU信号的串口输出。本文主要介绍石英挠性加速度计信号采集处理系统的设计。

1 石英挠性加速度计工作原理

石英挠性加速度计是一种力矩再平衡挠性摆式加速度计,采用整体式石英摆片作为检测质量,利用差动电容器来敏感检测质量在加速度作用下的位移变化,利用空气压膜阻尼,通过电磁力矩来实现力平衡和仪表的闭环。当力矩平衡时,力矩线圈中所需的电流与输入的加速度成正比,此时测量流经力矩线圈的电流值,即可测得载体沿加速度计输入轴上的运动加速度[2]。其输入输出特性如下:

2 硬件电路设计

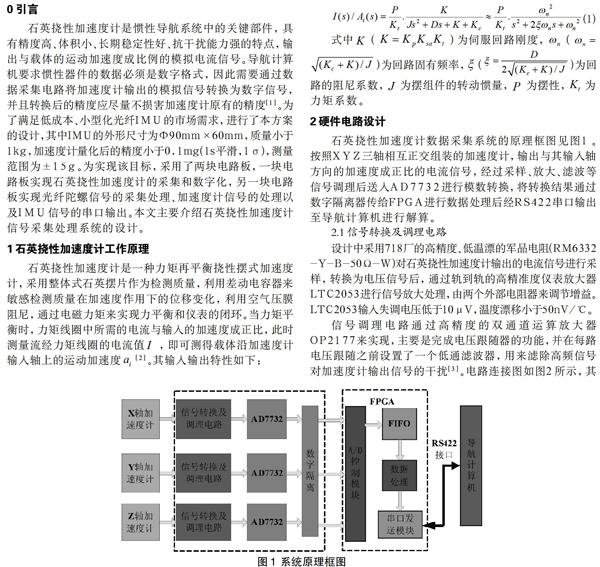

石英挠性加速度计数据采集系统的原理框图见图1。按照XYZ三轴相互正交组装的加速度计,输出与其输入轴方向的加速度成正比的电流信号,经过采样、放大、滤波等信号调理后送入AD7732进行模数转换,将转换结果通过数字隔离器传给FPGA进行数据处理后经RS422串口输出至导航计算机进行解算。

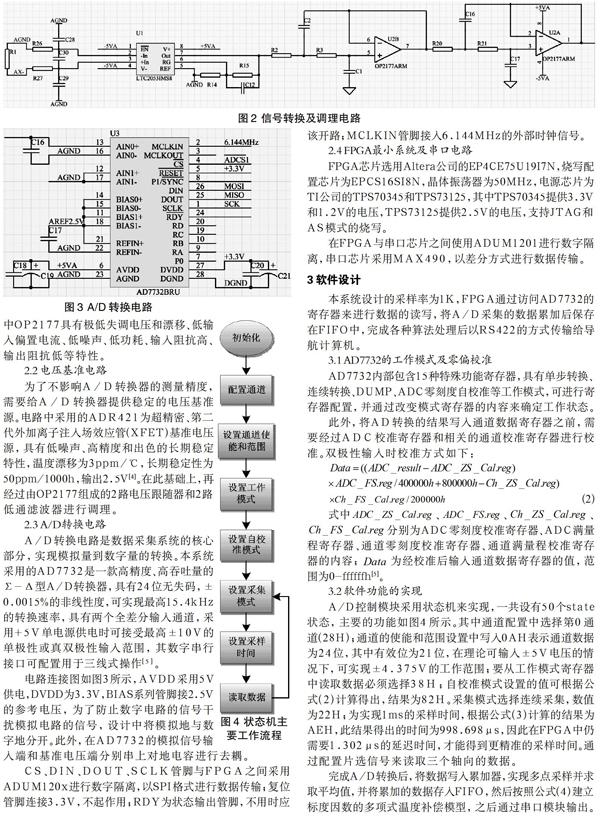

2.1 信号转换及调理电路

设计中采用718厂的高精度、低温漂的军品电阻(RM6332 -Y-B-50Ω-W)对石英挠性加速度计输出的电流信号进行采样,转换为电压信号后,通过轨到轨的高精准度仪表放大器LTC2053进行信号放大处理,由两个外部电阻器来调节增益。LTC2053输入失调电压低于10μV,温度漂移小于50nV/℃。

信号调理电路通过高精度的双通道运算放大器OP2177来实现,主要是完成电压跟随器的功能,并在每路电压跟随之前设置了一个低通滤波器,用来滤除高频信号对加速度计输出信号的干扰[3]。电路连接图如图2所示,其中OP2177具有极低失调电压和漂移、低输入偏置电流、低噪声、低功耗、输入阻抗高、输出阻抗低等特性。

2.2 电压基准电路

为了不影响A/D转换器的测量精度,需要给A/D转换器提供稳定的电压基准源。电路中采用的ADR421为超精密、第二代外加离子注入场效应管(XFET)基准电压源,具有低噪声、高精度和出色的长期稳定特性,温度漂移为3ppm/℃,长期稳定性为50ppm/1000h,输出2.5V[4]。在此基础上,再经过由OP2177组成的2路电压跟随器和2路低通滤波器进行调理。

2.3 A/D转换电路

A/D转换电路是数据采集系统的核心部分,实现模拟量到数字量的转换。本系统采用的AD7732是一款高精度、高吞吐量的Σ-Δ型A/D转换器,具有24位无失码,±0.0015%的非线性度,可实现最高15.4kHz的转换速率,具有两个全差分输入通道,采用+5V单电源供电时可接受最高±10V的单极性或真双极性输入范围,其数字串行接口可配置用于三线式操作[5]。

电路连接图如图3所示,AVDD采用5V供电,DVDD为3.3V,BIAS系列管脚接2.5V的参考电压,为了防止数字电路的信号干扰模拟电路的信号,设计中将模拟地与数字地分开。此外,在AD7732的模拟信号输入端和基准电压端分别串上对地电容进行去耦。

CS、DIN、DOUT、SCLK管脚与FPGA之间采用ADUM120x进行数字隔离,以SPI格式进行数据传输;复位管脚连接3.3V,不起作用;RDY为状态输出管脚,不用时应该开路;MCLKIN管脚接入6.144MHz的外部时钟信号。

2.4 FPGA最小系统及串口电路

FPGA芯片选用Altera公司的EP4CE75U19I7N,烧写配置芯片为EPCS16SI8N,晶体振荡器为50MHz,电源芯片为TI公司的TPS70345和TPS73125,其中TPS70345提供3.3V和1.2V的电压,TPS73125提供2.5V的电压,支持JTAG和AS模式的烧写。

在FPGA与串口芯片之间使用ADUM1201进行数字隔离,串口芯片采用MAX490,以差分方式进行数据传输。

3 软件设计

本系统设计的采样率为1K,FPGA通过访问AD7732的寄存器来进行数据的读写,将A/D采集的数据累加后保存在FIFO中,完成各种算法处理后以RS422的方式传输给导航计算机。

3.1 AD7732的工作模式及零偏校准

AD7732内部包含15种特殊功能寄存器,具有单步转换、连续转换、DUMP、ADC零刻度自校准等工作模式,可进行寄存器配置,并通过改变模式寄存器的内容来确定工作状态。

3.2 软件功能的实现

A/D控制模块采用状态机来实现,一共设有50个state状态,主要的功能如图4所示。其中通道配置中选择第0通道(28H);通道的使能和范围设置中写入0AH表示通道数据为24位,其中有效位为21位,在理论可输入±5V电压的情况下,可实现±4.375V的工作范围;要从工作模式寄存器中读取数据必须选择38H;自校准模式设置的值可根据公式(2)计算得出,结果为82H。采集模式选择连续采集,数值为22H;为实现1ms的采样时间,根据公式(3)计算的结果为AEH,此结果得出的时间为998.698μs,因此在FPGA中仍需要1.302μs的延迟时间,才能得到更精准的采样时间。通过配置片选信号来读取三个轴向的数据。

完成A/D转换后,将数据写入累加器,实现多点采样并求取平均值,并将累加的数据存入FIFO,然后按照公式(4)建立标度因数的多项式温度补偿模型,之后通过串口模块输出。

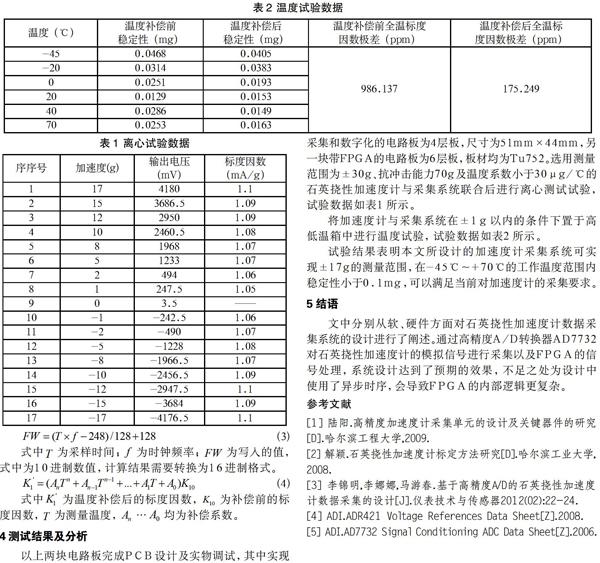

4 测试结果及分析

以上两块电路板完成PCB设计及实物调试,其中实现采集和数字化的电路板为4层板,尺寸为51mm×44mm,另一块带FPGA的电路板为6层板,板材均为Tu752。选用测量范围为±30g、抗冲击能力70g及温度系数小于30μg/℃的石英挠性加速度计与采集系統联合后进行离心测试试验,试验数据如表1所示。

将加速度计与采集系统在±1g以内的条件下置于高低温箱中进行温度试验,试验数据如表2所示。

试验结果表明本文所设计的加速度计采集系统可实现±17g的测量范围,在-45℃~+70℃的工作温度范围内稳定性小于0.1mg,可以满足当前对加速度计的采集要求。

5 结语

文中分别从软、硬件方面对石英挠性加速度计数据采集系统的设计进行了阐述。通过高精度A/D转换器AD7732对石英挠性加速度计的模拟信号进行采集以及FPGA的信号处理,系统设计达到了预期的效果,不足之处为设计中使用了异步时序,会导致FPGA的内部逻辑更复杂。

参考文献

[1] 陆阳.高精度加速度计采集单元的设计及关键器件的研究[D].哈尔滨工程大学,2009.

[2] 解颖.石英挠性加速度计标定方法研究[D].哈尔滨工业大学,2008.

[3] 李锦明,李娜娜,马游春.基于高精度A/D的石英挠性加速度计数据采集的设计[J].仪表技术与传感器2012(02):22-24.

[4] ADI.ADR421 Voltage References Data Sheet[Z].2008.

[5] ADI.AD7732 Signal Conditioning ADC Data Sheet[Z].2006.