TTE高完整性和标准完整性配置下同步机制和容错能力对比分析

杨劲赫,李 峭,汤雪乾

(北京航空航天大学电子信息工程学院,北京100191)

1 引言

在航天电子系统中的嵌入式计算应用中,综合模块化航空电子系统(Integrated Modular Avionics,IMA)为不同的航天电子应用提供开放和稳定的资源共享框架。基于混合关键安全性等特点的分布式航空电子系统(Distributed Integrated Modular Avionics,DIMA)作为 IMA的进一步升级,提升了可扩展性[1]和混合关键性综合化互连的能力。SAE AS6802标准规定的时间触发以太网(Time-Triggered Ethernet,TTE)是基于标准以太网开发的一种时间触发架构通信网络,具有实时、开放、安全以及满足混合关键安全性等特点,因此能较好地满足DIMA的要求,被广泛应用到航天电子系统中[2-3]。NASA已经使用TTE来提高航天电子系统的容错能力,并证明TTE对拜占庭错误有很高的容忍度[4-6]。SAE AS6802标准为TTE规定了一种分布式时钟同步协议。根据配置的不同,TTE同步组件可以分为高完整性(Highintegrity,HI)组件和标准完整性(Standardintegrity,SI)组件,在不同的完整性配置下,TTE网络时钟同步机制不同。为保证时钟同步的可靠运行,TTE网络为不同组件设计了不同的时钟同步容错机制,高完整性组件具有更加精准的分布式时钟同步功能和更强大的故障容忍机制[7]。近年来,TTE在众多实时应用中发挥着至关重要的作用,例如航天电子、汽车工业和其他工业网络物理系统。Loveless[4]在实验中同时配置了高完整性的交换机与标准完整性的端系统,验证了高完整性组件将故障限制为不一致-遗漏模式。兰杰等[8]实验证明了高完整性配置下的TTE网络时钟具备对抗单节点随意失效的能力。

时钟同步是实现时间触发架构的关键基础,对不同完整性配置下TTE时钟同步机制的容错能力进行验证十分有必要。本文介绍了SAE AS6802标准规定的TTE同步服务与容错机制,分析了高完整性与标准完整性配置下TTE同步机制的区别,通过网络仿真对2种配置下TTE时钟同步机制容错能力的差异进行验证分析。

2 TTE的时钟同步机制

时钟同步服务的目的是确保通信基础设施中组件的本地时钟保持彼此同步。研究时钟同步机制不仅要考察正常工作情况下的时钟同步功能,还需要关注时钟同步过程中同步组件的状态和行为。

2.1 同步过程

在TTE的同步服务中,组件被分为3类:同步主控器(Synchronization Master,SM)、压缩主控器(Compression Master,CM)和同步客户端(Synchronization Client,SC)。多数情况下,SM 与 SC配备于端系统,CM则一般由交换机充当。而同步消息则通过协议控制帧(Protocol Control Frame, PCF)来传递。

PCF帧有冷启动帧(Cold Start,CS帧)、冷启动应答帧(Cold Start Acknowledge,CA帧)和综合帧(Integration,IN帧)3种类型。PCF帧中的透明时钟域会记录帧的派发时刻td、传输延迟Dtrans、接收时刻treceive等同步信息。

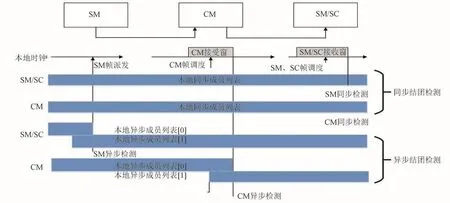

通信设施的启动过程伴随着CS帧、CA帧的交换。CS帧与CA帧的交换称为容错握手[9]。该过程中,CM不会对CS帧进行压缩,对CA帧也只是附加延迟后将其返回。在容错握手之后,同步设备将会进入协议状态机中表示同步操作的一个状态,即开始同步过程。同步过程中各个组件将会进行IN帧的交换,其过程与容错握手的方式相同,如图1所示。SM将PCF帧发送到CM,然后CM根据这些PCF的相对到达时间计算平均值,作为响应统一返还新的PCF。新PCF也会发送到SC。由于PCF帧的接收时间与发送时间有偏差,CM将对IN帧进行固化和压缩,获取时钟修正值,在对本地时钟进行修正后,把同步信息附加在IN帧中返还给各个端系统。各个端系统也将对IN帧进行固化,还原发送时刻,得到时钟修正值来对自身的本地时钟进行修正。而为了保持各个时钟始终处于同步,每隔一个固定的时间段,系统就会再次进行同步。这个过程称为集群周期。

图1 TTE同步过程Fig.1 Synchronization process of TTE

SM的协议状态机有异步状态和同步状态,异步状态包括SM_Integrate状态、SM_Wait_4_Cycle_Start状态、SM_Unsync状态、SM_Flood 状态和SM_Wait_4_Cycle_Start_CS状态,同步状态包括SM_Tentative_Sync状态、SM_Sync状态和SM_Stable状态。

当SM是标准完整性时,CM只会派发用于自身时钟同步的压缩过的PCF帧,这样可以防止故障帧的传播;当SM配置为高完整性时,不管是否已经用于CM自身的时钟同步,所有的PCF帧都被派发。

2.2 固化与压缩

通过固化功能与压缩功能,可以获取较为精确的时钟修正值,用于各个组件的本地时钟修正,实现同步。固化功能在SM、SC、CM中都有实现,而压缩只在CM中实现。

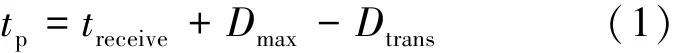

固化功能用于还原PCF帧发送的真实时刻。每个节点都可能接收多个的PCF帧,固化功能将还原它们的正确发送顺序。通过透明时钟内携带的同步消息,可以计算固化时刻点tp,如式(1)所示:

式中,Dmax为最大传输延迟,treceive为本地时钟测得接收时刻点的值,Dtrans为PCF帧从发送端到接收端的传输延迟。

压缩功能在接收到PCF帧时开始启动,而不是在同步的本地时钟到达某一个时间点时开始。CM在第1个不属于当前同步的固化时刻点tp,1打开一个长度为P的接收窗,P/2为系统的预设精度。若在该接受窗内至少接收到2个固化时刻点,则打开下一个接收窗。从第2个接收窗开始,若收集到至少一个固化时刻点,则打开新的接收窗,直到窗的长度达到最大值Wmax=(f+1)×P,f为所容忍的错误的SM个数,SM的总数为n。否则关闭窗并不再打开新的接收窗。

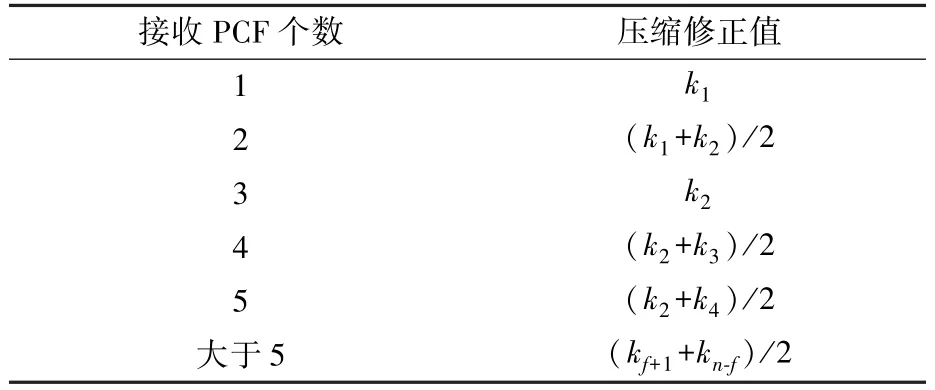

对于接受到的PCF帧,通过具有容错能力的均值公式(Falut-Tolerant Average,FTA)来计算压缩修正值。tp,i为第i个不属于当前同步的固化时刻,定义后续固化时刻点与tp,1之间的时间间隔为 ki=tp,i-tp,1[10],具体计算如表1所示。

表1 FTA计算压缩修正值Table 1 Calculation of compression correction value

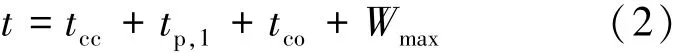

得到修正值tcc后,CM对压缩时刻点t进行计算,如式(2)所示:

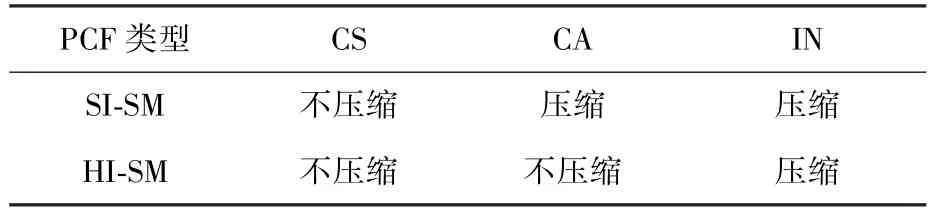

式中,tco为固有计算开销。以t为基准,CM将PCF帧发回到SM。CM不会在同一时刻点操作高完整性和标准完整性配置的SM,因此同步时对PCF帧的处理因高完整性与标准完整性配置差异而有着显著的区别,如表2所示,高完整性配置的SM只会压缩IN帧,标准完整性配置的SM则会压缩CA帧和IN帧。

表2 不同完整性下对PCF帧的处理Table 2 Processing of PCF with different integrity

不同完整性配置下,TTE同步组件的对PCF帧的响应也不同。当配置为标准完整性时,SM会对所有CS帧做出响应。CM将仅转发与CM的本地时钟同步的IN帧,在派发时刻点到来时将压缩后的IN帧发送。并且通过漏桶算法[11],每一个集群周期都只会接收来自每个SM的一个PCF帧。

当配置为高完整性时,SM仅会对来自其他SM的CS帧做出响应。CM将转发所有IN帧。并且高完整性的设计将会阻止SM在一个集群周期内发出多个IN帧。

3 TTE的时钟同步容错机制

3.1 失效模式与假设

TTE在同步过程中出现的各种故障总是与SM、CM等组件及其接口的行为有关,常见的各种失效模式包括以下3种:

1)寂静失效。同步组件处于静默状态,不会对任何输入做出回应,停止输出。

2)不一致-遗漏失效。这种失效模式是不一致失效和遗漏失效的组合。在接收来自不一致失效组件的消息时,群组内的一些组件会收到正确的消息,而另一部分收到的则是错误的消息。而处于遗漏失效模式的组件则无法成功发送或接收任意数量的帧。

3)随意失效。处于该失效模式的组件会不可控地在任意时间产生任意消息,并且这种失效模式会不受控制地产生不一致失效。

TTE网络支持单点失效和双点失效2种类型的失效假设。在单点失效假设下,TTE旨在容忍终端系统的任意故障或交换机的不一致-遗漏故障。TTE中的交换机可以配置为执行中央总线监控功能。中央总线监控功能确保即使一组端系统出现随意失效,它也会通过将其转换为不一致-遗漏失效模式来消除这些故障终端系统的影响;在双点失效假设下,TTE旨在容忍2个不一致-遗漏失效设备,这些设备可以是2个端系统,2个交换机或1个端系统和1个交换机。

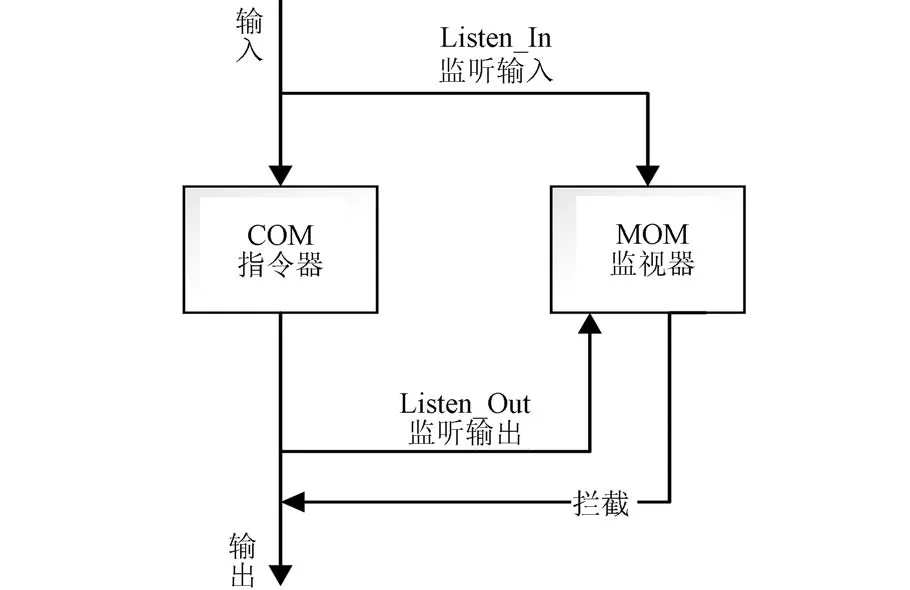

高完整性与标准完整性配置的TTE具有的同步容错能力有明显差异。当配置为高完整性时,SM和CM的故障模式限制为不一致-遗漏故障。根据SAE AS6802标准,在高完整性配置的TTE网络中,组件包含了如图2所示的指令/监视对结构,以应对不一致-遗漏失效模式。

图2 指令/监视对结构Fig.2 Structure of Com/Mon pair

当配置为标准完整性时,TTE容忍单个SM的随意故障或单个CM的不一致-遗漏故障,但不能同时容忍两者同时出现。

由于标准完整性配置下的SM在同步过程中会对自己发出的CS帧做出响应,即某个SM也可能从未与其他的节点进行过正确的“握手”,获取有效的时间修正信息,从而造成随意失效,这也是标准完整性配置的TTE无法对抗随意失效的原因。由于高完整性配置的SM只对来自其他SM的CS帧做出响应,保证了“握手”的有效性,避免了随意失效的发生,因而比标准完整性配置具有更强的容错能力。在高完整性配置下,TTE能容忍SM和CM的并发故障。

3.2 结团检测

结团是指同步域中某一些节点(但不是全部)形成了同步并可以维持,但其他的节点无法参与同步,也就是整个系统未能达成正确的同步。常用的结团检测包括同步结团检测与异步结团检测,具体如图3所示。

同步结团检测用设备本地变量local_sync_membership跟踪与当前达到同步的SM数目。local_sync_membership是一个位向量,与 pcf_membership_new中对SM与位的指定一致。pcf_membership_new为PCF帧中的位向量,当某一位为1时,表示该PCF帧携带了该位所对应SM的时间信息。同步结团检测功能可以在TTE协议状态机中的每个同步状态独立的使能或禁止。当同步结团检测服务工作时,local_sync_membership与状态定义阈值进行对比,如果local_sync_membership中设置位数比相应的阈值小则表示检测出结团情况。

图3 结团检测Fig.3 Clique detection

异步结团检测功能使用2个本地变量local_async_membership[0]和local_async_membership[1]用于跟踪当前与相应设备不同步但可用(不包括关闭电源的 SM)的SM的数目。local_async_membership{0||1}都是位向量,与 pcf_membership_new中对SM的分配关系一致。

异步结团检测功能监视通信链路中预期外到达的PCF帧。这种情况可能是该帧的固化时刻点在接受窗口外,也可能是固化时刻点在接受窗口内但有错误的集成周期值。

4 不同完整性配置同步的仿真对比

4.1 仿真实现与参数配置

OMNet++是一个可扩展、模块化、基于组件的C++仿真库和框架,主要用于构建网络的仿真。该软件提供基于Eclipse的IDE、图形运行时环境和其他工具,有实时模拟、网络仿真、数据库集成、SystemC集成等功能的扩展[12]。本文利用OMNet++,根据SAE AS6802标准建立TTE的仿真模型,进行同步及容错仿真实验。

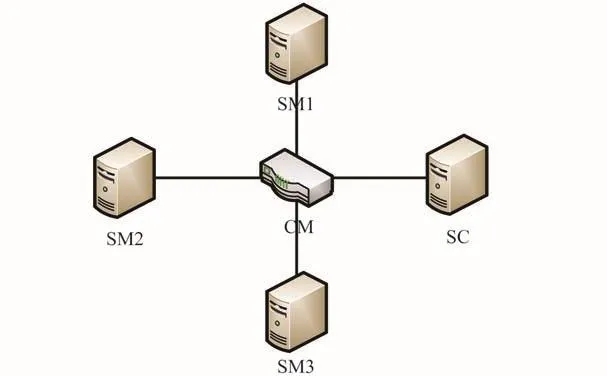

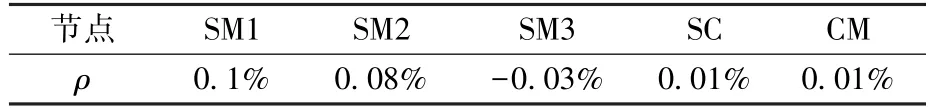

同步仿真实验的配置为:设置tick为10 ns,代表物理时钟一个滴答的时间宽度,同步精度为50 tick。如图4所示,实验仿真的网络有1个交换机和4个端系统。节点个数会影响FTA的计算以及错误节点的设置,但并不妨碍高完整性和标准完整性TTE的工作机制。

图4 TTE仿真Fig.4 Simulation of TTE

5个节点的时钟漂移率ρ如表3所示:

表3 节点时钟漂移率设置Table 3 Clock drift rate setting

4.2 无失效正常同步

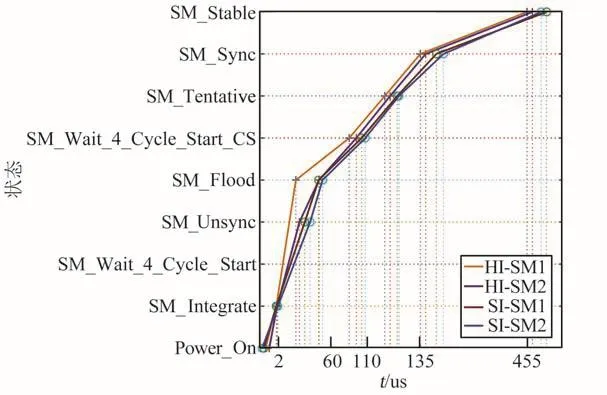

选取SM1和SM2进行无失效正常同步实验,进行高完整性配置和标准完整性配置下的对比,如图5所示。高完整性和标准完整性配置的SM最后都达到了同步稳定的状态(SM_Stable),只是高完整性所需时间要略小于标准完整性。

图5 无失效同步Fig.5 Normal synchronization

当同步节点进入同步状态时,不同配置下各节点的时钟修正值如表4所示,以tick为单位。时钟同步修正值的最大值为17 tick,小于规定的同步精度(50 tick),说明所有的TTE网络节点实现了全局同步。

表4 节点时钟同步修正值Table 4 Clock correction value

4.3 单节点不一致-遗漏失效

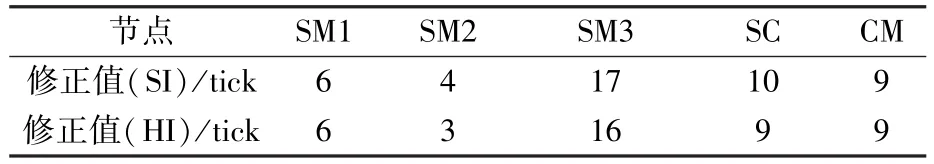

设置SM1为故障状态,不会向CM发送PCF帧。根据FTA算法,节点总数N与需要容忍错误节点的个数f需满足N>3f,因此设定f=1。对比高完整性和标准完整性配置实验结果,如图6所示,标准完整性配置下同步所需时间为455μs,明显大于高完整性配置下的时间293μs。

单节点的不一致-遗漏失效不会影响全局的同步,失效节点可以通过其他节点的同步信息在当前的集群周期中完成同步。

发生失效时,如果PCF帧落到接收窗外,高完整性配置的TTE网络可以快速通过同步结团检测服务将同步状态退回到同步的初状态并进行重启动。而标准完整性要在下一个同步周期到来时,通过异步结团检测才能进行重启动。

4.4 多节点不一致-遗漏失效

图6 单节点不一致-遗漏失效Fig.6 Inconsistent-Omission failure of single node

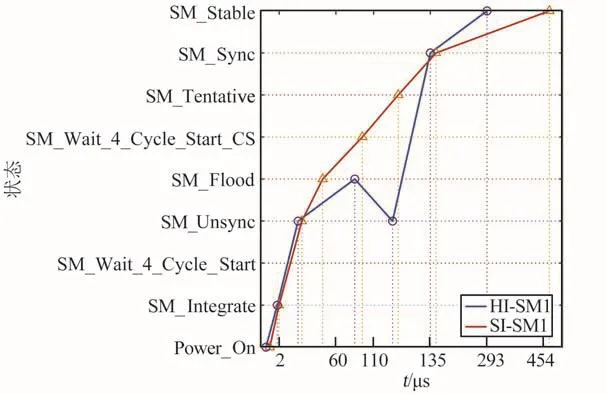

设置SM1和CM为故障状态。SM1无法正常发送出CS、CA帧,CM也不会向其发送来自其他节点的CS帧与CA帧。因此SM1只能接受到IN帧。

如图7所示,在CM和SM1同时失效的情况下,高完整性配置的TTE网络节点可以完成同步(SM_Stable),而标准完整性配置的节点则无法进入最终的同步状态,无法从SM_Tentative_Sync状态跳转到更稳定的同步状态。

图7 多点不一致-遗漏失效Fig.7 Inconsistent-Omission failure of multiple nodes

5 结论

通过对TTE高完整性与标准完整性的仿真验证和分析,二者在机制上尤其是容错能力方面的区别主要体现于:

1)2种完整性设计的时钟同步机制都有一定的容错能力,高完整性配置下TTE网络时钟同步机制的容错能力更强,能对抗标准完整性所无法对抗的随意失效。

2)面对不一致-遗漏失效时,高完整性配置的TTE网络能更快地进入重启动,因此反应速度要明显快于标准完整性。相较于标准完整性配置,高完整性配置具有更好的安全性和可靠性。

3)具有高完整性设计的TTE对比标准完整性配置有更好的时钟同步机制容错能力和对故障的反应速度。

本文研究可以为航空航天等安全关键等级高的实时应用容错配置提供论证参考。