多通道混合数据采集系统设计与实现

(西安工业大学 光电工程学院,西安 710021)

0 引言

为了能够考核战斗部的威力与作战效能,静爆试验一直是兵器装备试验行业广泛采用的方式方法。而评估破片的速度、大小与散布特征又是战斗部静爆实验的核心测试内容。国内外通常采用静爆试验的方法测量战斗部爆炸产生的破片的威力。其中,破片速度测量是试验测试的核心内容之一。传统破片速度测量方法分为三种:网靶法、光电靶法和高速摄影法[1-3]。

文献[3-4]分别设计了二维光幕测试破片速度并对破片的大小体积进行估算的测试原理。钱礼华[5]介绍了梳状靶在破片测速中的应用问题,指出破片测速中现场数据采集的困难并研制了一种破片测速用的数据存储装置。刘秀及刘吉[6]针对破片参数测试中需要多点分布测试的问题,提出一种以爆炸火光作为触发信号源的多通道同步分布式数据采集系统,将火光作为触发信号启动采集系统[7]。

差分式梳状激光光幕探测器是为静爆试验中速度测试而产生的一种较新的技术。它是一种基于激光扫描阵列技术的差分式光幕,差分式光幕在其光阑狭缝下有两排光电二极管,它应用光学对称的两个探测视场形成差分探测结构。通过探测对称光幕光通量的相对变化感知运动目标达到预定空间位置的精确时刻。当有目标垂直穿过幕面时,引起的光通量变化会导致接收的光电管产生一个脉冲信号,产生被测目标的过幕信号[8-9]。

图1 差分式梳状激光光幕

通过信号处理与分析,可以通过过幕信号的时域特征来表示目标穿过光幕的特征时刻[10-11]。当一定数量的差分式光幕通过排列组合形成类似于“梳齿”的形状后,这样的探测器便具备一定的辨识同时过幕的多个破片的能力,能够对破片穿过幕面时相对探测器的大致方向进行粗略的估计,必要时,这个估计值可以对破片速度的测试结果进行一定的修正,用来提高测试精度[12-13]。

实际测试过程中,根据被测物的特点,同时在不同位置布置多个探测器,而单个探测器各个差分梳齿的输出是独立的,如果要对破片的过幕信号进行记录采集,就必须满足每个通道占用不同的数据采集通道。并且对于高速破片来说,提高采集信号的时间分辨率是保证速度测量精度的必要措施。

为解决上述问题,本文设计一种具有自治能力的多通道混合数据采集系统,以满足对差分式梳状激光幕探测器的数据采集需求。

1 系统总体结构

静爆试验测试系统整体由4部分组成,如图2所示。其中前级差分式梳状激光光幕探测器完成对飞行破片的探测及感知任务、输出相应的模拟信号,多通道混合数据采集系统完成对前级数据采集剔除、有效数据片段UTC打标及传输任务,数据处理软件完成对采集数据的二次分析、处理及人机交互任务,温度自适应控制系统完成对探测设备机箱内部温度的管控,使整体设备处于恒温状态。

图2 静爆试验测试系统整体架构图

针对前级探测系统输出特性,本设计完成整体系统中多通道混合数据采集系统的硬件电路及控制软件设计及功能测试。实现主要技术指标见表1。

表1 主要技术指标

如图1中虚线框中所示,本设计采用以FPGA+ARM为核心的方案。为满足采集系统对高精度时间频率的要求,首先通过GPS的PPS信号对压控温补晶振进行驯服,使得本地时钟系统与当前UTC时间保持μs级别的同步。然后FPGA控制数据的采集并完成剔除及有效数据片段的缓冲及打标UTC时间片段。最后ARM根据上位机要求,读取缓冲有效数据,通过USB总线传输至上位机,其中有效数据片段的组成由前级探测器输出的模拟信号片段及当前片段对应的UTC时间组成,如图3所示,其中波形为采集前级探测器输出的弹形信息,起点数字标注本弹形产生的UTC时刻,如084522-121-256表示本波形UTC时间为08点45分22秒121毫秒256微秒。

图3 混合信号

2 系统硬件设计

2.1 板级时钟

晶振时钟短期稳定性好,随机误差较小,而GPS的PPS秒脉冲没有累计误差的特点,使用GPS对晶振时钟进行驯服,以消除晶振时钟的累计误差及产生本地UTC时间并细分到μs级。

时钟驯服的基本原理是利用卫星授时接收机提供的固定频率信号, 与本地振荡器产生的振荡信号进行比对,获得频率差;再通过对本地振荡器的调节,使振荡频率与卫星的振荡频率一致,从而完成对高稳晶振的驯服校频过程。

GPS芯片选取双模的BD126,其接收频率GPS L1与BeiDou B1,冷启动31 s,热启动1 s。输出电平TTL,波特率9600 bps,PPS输出频率1 Hz,脉冲宽度100 ms。

图4 GPS驯服压控温补晶振流程图

驯服过程:ARM解析GPS产生的秒级UTC时间,并通过SPI总线传至FPGA。PPS秒脉冲及晶振时钟进入FPGA,FPGA对CLK进行分频至10 MHz并记录相邻两个PPS脉冲上升沿之间的个数。并将误差值传递至ARM。ARM结合当前频率误差值来调整晶振压控端电压值,进而调整晶振的震荡时钟周期,使用晶振趋向于一个标准值,并于当前UTC时钟保持同步。

图5 GPS及温补晶振电路图

2.2 模拟信号调理及采集电路

前端信号调理电路为一个二阶的巴特沃斯滤波器、电压跟随及低通滤波器,主要完成对输入信号的钳位保护、滤波带宽限制及输出满足AD芯片输入驱动能力要求。采用TI公司的ADS7888芯片,ADS7888是一个8bit,1MSPS的模数转换器,该逐次比较型模数转换芯片内部包含一个基于电容的采集保持器。16路通道每一通道使用一片ADS7888芯片,各通道之间相互独立工作。ADS788数字控制端为LVTTL电平、三线串行接口,依此为CS,SCLK,SDO。其与FPGA通用IO连接,由FPGA控制AD的采集时序。

图6 模拟信号采集及调理电路

2.3 ARM及USB驱动电路

ARM芯片选用意法半导体公司的STM32F429,其内核Cortex-M4主频可达180 MHz,32位。主要使用该片内资源有 3个DMA,1个UART,1个USB HS控制器,FMC控制器等。选择该芯片的主要原因是其内部提供专用的USB协议层及数据调度总线资源,在USB高速运行过程中,并不占用CPU资源,且外部仅需要USB2.0PHY芯片支持即可工作。

USB PHY层选用芯片USB3300,该芯片遵守USB2.0 Transceiver Macrocell Interface 协议,8bit的数据位宽,主时钟24 MHz,支持USB2.0高速模式。

2.4 FPGA及DDR存储电路

使用型号为MT47H64M16HR的两片DDR2作为数据缓冲芯片,其单片容量1 Gbit,两片组合总容量为2*1 Gbit=2 Gbit 即为256 MByte。单片DDR2存储器为16 bit,两片存储器共用控制线和地址线,数据线并列,即组成了32位的2 Gb的存储器组,其带宽可达达:166.7M*2*32约为10 Gbit。可满足数据缓冲速率及容量的需求。

FPGA采用Alter Cyclone Ⅳ系列得EP4CE30F23C6,其内部含有15408的可编程逻辑单元,片上有516Kbit RAM,4个PLL,343个IO口及丰富的布线资源。板载晶振选用频率50 MHz,频率稳定性小于1 ppm的温补晶振。50 MHz经过FPGA内部锁相环配置至100 MHz作为全局时钟。Alter提供该型号的DDR—IP核,能简化DDR复杂时序的读写要求。

2.5 电源电路

电源主要分模拟区域跟数字区域,外部提供+12 V的输入电压,经过设计的电源转换电路,转换为系统正常工作时的电压。其中模拟区域供电为+5 V,数字区域供电有+5 V,+3.3 V,+2.5 V,+1.8 V。主选芯片MP2359是单片降压开关模式转换器,带有一个内置的功率MOSFET,开关导通电阻0.3 Ω。其输入范围4.5~24 V,可调输出范围从0.8~15 V。MP2359可实现电流的峰值输出电流在很宽的输入电源范围内出色的负载及电压调节。故障条件下的保护动作包括逐周期电流限制和热关机,通过改变FB端口的反馈电阻易得到所需电压且封装TSOT23 -6小巧,便于PCB设计实现。

图7 MP2359部分电源结构图

3 系统软件设计

整个系统软件有FPGA内部逻辑、ARM控制程序组成。对于实时性要求高的部分由FPGA处理,对如复杂繁琐的控制信息由ARM处理。

FPGA作为整个系统的关键之一,其内部时序设计至关重要,结构如图8所示。其中FPGA完成的工作按功能划分主要分为三大类:1)对模拟数据的采集、剔除、打时标及缓冲;2)协助ARM完成GPS对本地时钟的驯服;3)接收ARM的控制指令完成相应的任务。

图8 FPGA内部逻辑图

ARM主要负责工作:1)接收上位机控制指令并完成对应操作;2)结合FPGA完成对本地时钟的驯服;3)读取FPGA缓冲的数据并通过USB总线向上位机发送。

图9 ARM主程序流程图

系统整体上电后进入初始化状态首先完成本地时钟与UTC时钟同步,由ARM、DA、FPGA、GPS及压控温补晶振共同完成,其过程分为三个阶段。

第一阶段在上电后的二十分钟内使机箱内部温度及GPS信号区域稳定,GPS正常接收卫星信号并通过串口输出当前对应的UTC时间码文及TTL电平的PPS秒脉冲信号。ARM解析串口信息得到当前的UTC时间并通过SPI总线传输至FPGA,形成秒级系统时钟。第二阶段晶振输入时钟进入FPGA并进行5分频至10 MHz,通过计数器连续测量相邻PPS秒脉冲上升沿之间10 MHz时钟上升沿的个数,并计算其与标准值的偏差ΔT并将该值传递至ARM。第三阶段于GPS信号在传输过程中有一定程度的干扰,使得PPS信号存在抖动。ARM接收一段时间内的偏差ΔT1,ΔT2,ΔT3,…,ΔTn,ΔTn + 1…,以n作为窗口长度对其中的n个测量值取平均值。通过移动窗口得到误差值Δe1,Δe2,Δe3,…,Δen,Δen+1…。如式(1)所示:

(1)

通过PID算法计算当前需要输出的控制电压值Un。ARM通过控制DA调整晶振压控端电压值调整其频率。

(2)

经过系统初始化状态的调整,压控温补晶振输出时钟趋向一个标准值并且与当前UTC时间同步,形成板上微妙级系统时钟。

当系统完成初始化工作后,进入主循环进行任务处理,此时系统的工作状态均由上位机控制指令管理。

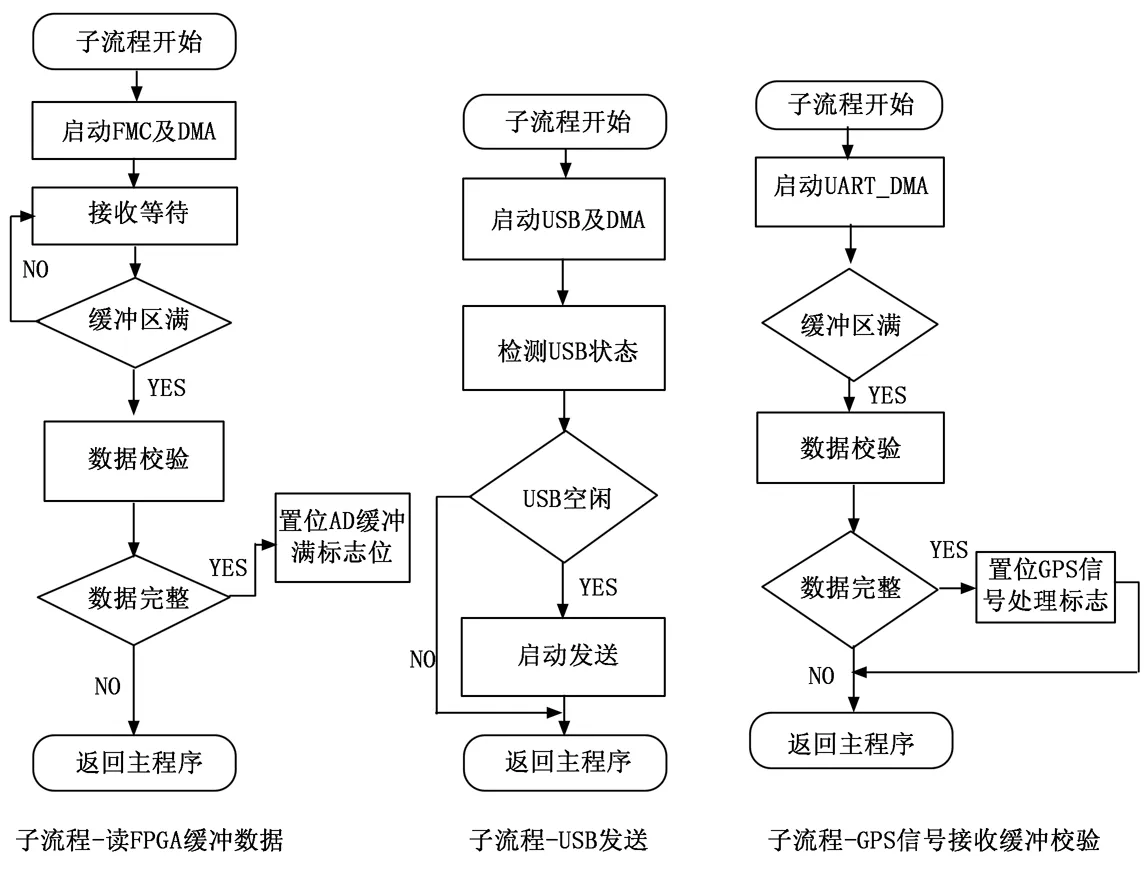

图10 ARM子程序流程图

由于系统整体工作时长往往达数小时,且实时采集模拟数据量达到每秒16兆字节,庞大的数据量给存储及传输通道带来严重的压力,且不便于后续软件处理。上位机软件算法根据系统整体要求配置合适的TS和Vm阈值作为数据筛选依据并传递至本系统,其中TS表示时域上采集信号脉冲宽度,Vm表示脉冲信号幅值阈值。FPGA根据其配置的阈值在数据采集阶段,对每个通道设置一定深度的乒乓缓冲区,当其中一个缓冲区满时,数据缓冲至另一通道。在此期间检测其中数据点是否满足阈值要求,若满足则向DDR中继续缓冲该数据并根据上位机的控制指令进行传输,若不满足阈值条件则清除该缓冲区域数据,不做保留。

为保证数据的不丢失,FPGA内部设三级缓冲区并配合片外DDR缓冲区域,共可缓冲2556 MByte。FPGA与STM32F429通过并行FMC总线相连接,并且ARM内部三个DMA均被使用各个独立工作服务于相应的单元,完成数据的搬运工作,并产生相应的标志位。上位机通过Libusb库实时轮询ARM端口,将采集数据通过USB2.0高速模式传递至上位机。

4 实验结果与分析

多通道混合数据采集系统完成与前后级系统的联调试验,并且经过高低温工作及贮存、功能振动及电磁兼容性试验,产品满足技术指标。并采用型号为XGK01型校验仪产生时序可控的模拟光信号入射至前级探测器,通过本采集系统对前级探测器输出信号进行采集,并校验仪进行对比,其中无漏采集信号现象发生、且产生的信号UTC时标值与校验仪达到一致。

5 结束语

本文针对静爆试验中差分式梳状激光光幕探测器的输出特性设计一款多通道混合数据采集系统。详细介绍了该的硬件及软件设计,其中以为FPGA+ARM为核心架构,主要包括GPS驯服温补晶振单元、有效数据UTC时间打标及缓冲单元单元及ARM上位机通信单元,其中数据采集及打标为该系统核心。采用FPGA作为处理器确保数据采集及UTC时间的实时性及准确性,ARM确保设备控制及系统与上位机交互的便利性。试验结果表明,应用本设计进行混合信号采集可为后续处理软件提供破片过幕的弹波信息及特征时刻进行有效、精确的提取。