基于以顶层ITO为像素电极设计的产品工艺优化

吕艳明,操彬彬,栗芳芳,安 晖,叶成枝,李法杰,杨增乾,彭俊林,冯耀耀,刘增利,陆相晚,李恒滨

(合肥鑫晟光电科技有限公司,安徽 合肥230001)

1 引 言

高开口率高级超维场转换技术(HADS)薄膜晶体管(TFT)中使用的有机膜绝缘层膜厚可达数微米,并且介电常数低、平坦度高[1-2],极大地增加了信号线(Data)与公共电极(Common)、像素电极(Pixel)之间的间距,有利于减少寄生电容、降低功耗、增大开口率。

负性有机膜因感光性好、显影速率高、产能高、工艺步骤少等优点,在TFT-LCD行业中应用最为广泛。但负性有机膜由于需要大面积曝光交联,因此更容易受光路中的颗粒物影响,造成光刻后图案厚度偏薄甚至缺失。对于顶层氧化铟锡(ITO)为像素电极(Pixel Top)、首层ITO为整面覆盖的公共电极的TFT而言,若信号线上方的有机膜厚度偏薄将会拉近信号线与公共电极之间的距离,严重时将导致两者之间的短路(Data-Common Short,DCS),造成暗线不良。在此背景下,本文通过工艺流程变更从源头上规避了上述形式DCS不良的发生,有效提升了良率,节约了生产成本。

2 有机膜产品DCS不良介绍

2.1 DCS不良现象

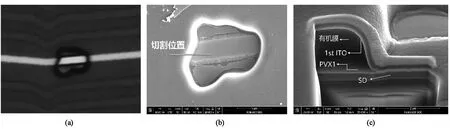

图1(a)为TFT阵列工艺终检工序电学测试检出的DCS不良显微镜图,图中可见不良位置存在膜层异常。图1(b)为不良位置聚焦离子束俯视图,图中可见不良位置存在明显的膜层缺失产生的凹坑。进一步用离子束按图1(b)标示位置对凹坑处切割,从图1(c)切割后截面图可以清晰地看出有机膜和第一钝化绝缘层(PVX1)缺失,但未见膜层熔融痕迹,可排除静电击穿。显然绝缘层的缺失造成了信号线与公共电极ITO之间的直接导通,导致该处信号线信号被公共电极信号拉动,从而被电学检测检出DCS。

图1 DCS不良。(a)显微镜图;(b)聚焦离子束俯视图;(c)聚焦离子束截面图。

2.2 DCS不良机理分析

从图1(c)中可以看出DCS位置的公共电极ITO上方各膜层以及下方的信号线膜层均正常,因此不良产生工序应为有机膜至PVX1之间。通常有机膜厚度相对较厚(2~3 μm),有机膜涂覆时烘烤的热交联效应及曝光时的射线衍射易导致开孔区底部形成残膜,故常利用干法刻蚀进行表面处理(PVX1刻蚀):一方面利用干法刻蚀的物理轰击、化学氧化作用清除残膜;另一方面对于首层ITO为像素电极设计的HADS产品,可利用有机膜做掩膜同步形成像素ITO与TFT信号线源/漏极导通的开孔。一般情况下,PVX1刻蚀对有机膜厚度的损耗仅为0.2~0.3 μm,显然不足以将有机膜刻穿。因此,图1中有机膜的缺失应主要与其自身制程的异常相关,其中最常见的情况为制程中颗粒导致的负性光阻异常。如图2所示,曝光过程中异物附着在有机膜表面,产生类似光罩(Mask)的遮光效应,遮光严重情况下会导致显影时有机膜的缺失。进一步地,PVX1刻蚀掩膜的缺失将导致PVX1膜层的缺失,最终导致顶层ITO为像素电极设计的HADS产品的公共电极ITO与信号线在异常区域短接形成DCS不良。

图2 DCS不良发生机理

3 DCS不良改善方案与实验验证

鉴于行业内TFT制程中微小颗粒异物无法做到100%管控规避,通过提高设备内的洁净度管控来改善有机膜异常导致的DCS不良效果有限。对于顶层ITO为像素电极的产品而言,显示区内公共电极ITO无须与源/漏极直接导通,故可考虑将PVX1刻蚀工序省略。基于上述DCS不良发生机理,即使有机膜发生缺失,PVX1的存在仍可有效对公共电极ITO与信号线起到绝缘作用。

由此可以建立如图3(b)所示新的TFT制作工艺流程,与图3(a)所示现有工艺流程对比:(1)PVX1刻蚀省略,即新工艺流程中公共电极ITO沉积前PVX1完全保留;(2)显示区和周边过孔全部在第二钝化绝缘层(PVX2)刻蚀时形成,即PVX2、PVX1、栅极绝缘层(GI)3层氮化硅同步刻蚀。最终如图4所示,有效避免了有机膜异常导致的公共电极ITO与信号线短接现象。

3.1 “一步刻蚀”工艺初探

为验证新工艺流程对DCS改善效果,在某高分辨率以顶层ITO为像素电极设计的HADS有机膜产品上进行实验。按照图3(b)所示新工艺流程进行全膜层TFT基板制作,制作完成后对TFT基板进行电学检测,确认DCS发生率。测试时输出界面基板缺陷图出现大量黄斑、黄线,报出大面积不良,但显微镜确认未发现明显异常。通过扫描电子显微镜进一步确认周边跨接过孔截面,结果如图5所示,连通栅极的跨接过孔在PVX1层存在非常严重的底切(Undercut)现象,导致ITO在PVX1处断裂。信号断路后造成大面积不良发生,无法甄别DCS是否得到有效改善。

图3 工艺流程变更。(a)原工艺流程;(b)新工艺流程。

图4 DCS改善原理

鉴于PVX1处存在底切现象,推测PVX1膜质相对偏软。进一步地对单层膜进行刻蚀率测试发现PVX1刻蚀率最大(见图6标示),即PVX1膜质最软,与此前分析相符。图6表示了PVX1层底切的发生机理:干法刻蚀同时存在物理性各向异性刻蚀和化学性各向同性刻蚀。物理性刻蚀主要通过离子轰击,垂直于基板方向进行刻蚀,对PR胶形貌依赖性大;而化学性刻蚀则对被刻蚀膜层的膜质依赖性大,刻蚀效率高,膜层间刻蚀率不匹配情况下容易在膜质较软膜层处产生底切现象。

图5 TFT栅极过孔截面

图6 PVX1 底切形成机理

3.2 刻蚀率匹配调整

PVX1位置膜层出现底切的根本原因在于PVX1刻蚀率大于PVX2刻蚀率,要解决底切问题首先需要进行膜质变更以实现膜层刻蚀率匹配,即要保证膜层刻蚀率满足PVX2>PVX1>GI。在3种氮化硅膜层中,PVX1作为有机膜第一钝化层,功能性要求低且厚度最薄,膜质变更品质风险最小,因此选择调整PVX1膜质较为合适。为此按表1所列成膜条件进行PVX1膜质变更的4因子2水平实验设计,对各条件对应的PVX1单膜刻蚀率进行测量,测量结果如表1所示。

表1 PVX1 等离子增强化学气相沉积成膜工艺优化实验设计

续 表

(“-”表示同改善前条件)

从图7刻蚀率测试结果的主效应图可以看出,在选定的实验条件下,增大成膜射频功率、降低成膜压力、减小电极间距以及增大SiH4∶NH3气体流量比均可降低膜层刻蚀率;标准化效应正态图显示射频功率、压力、电极间距对刻蚀率影响显著,气体流量比影响不显著。

图7 PECVD成膜参数对刻蚀率影响分析。(a)主效应图;(b)标准化效应正态图。

各成膜条件对膜质影响机理如下:增大成膜射频功率可以提高反应气体激活效率及沉积速率,增加等离子体密度,可增加薄膜中Si—N键,减少Si—H键、N—H键,使薄膜无序程度降低,提高薄膜表面均匀性和有序性[3],提高薄膜的致密性[4]和膜层硬度。降低反应腔体压力,可使反应物自由电子的平均自由程变长,在高频电场中碰撞加速获得更多能量[5],提高激活反应气体的能力,可减少成膜成分中Si—H、N—H键及杂质成分,虽然反应气体分解得到的活性等离子体向基底运动动能变大,但单位时间内到达基板表面的粒子数目变少,沉积速率会下降,这也利于氮化硅薄膜的整齐均匀生长,增大氮化硅密度[6-10]。电极间距过大会影响薄膜沉积速率,造成颗粒性粉尘问题;而电极间距过小会使离子反应速度过快,薄膜沉积质量下降。在适当区间内减小电极间距虽然沉积速率会有所下降,但会使等离子体密度提高,Si—N键结合增强,可以得到相对较好的成膜质量和良好的薄膜平坦度。当NH3流量较大时,等离子增强化学气相沉积成膜物质中Si—H键、N—H键含量高,氮化硅膜质会较疏松[11],而通过减少NH3流量即增加SiH4∶NH3流量比可减少Si—H成键,成膜成分倾向于Si3N4原子计量比,从而提高膜层硬度。

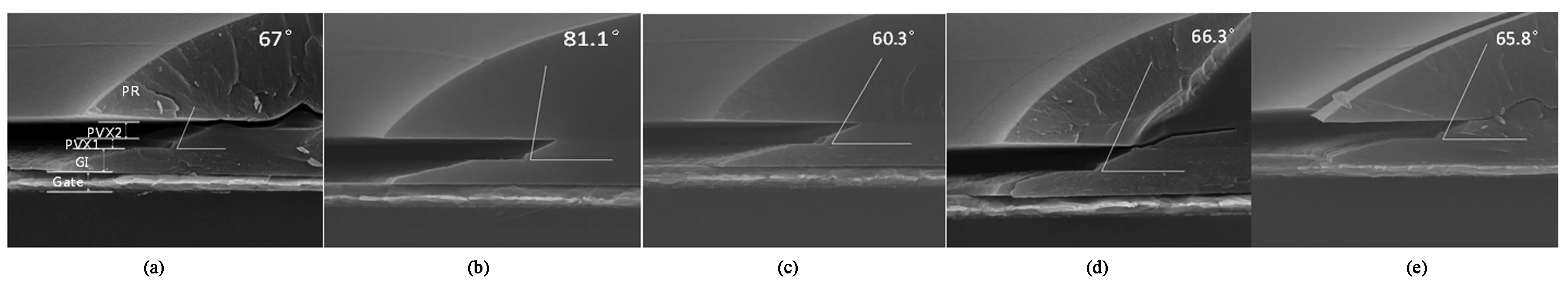

从表1中各成膜条件对应的PVX1刻蚀率结果可以看出,成膜条件2、7刻蚀率较大,不满足刻蚀率要求,成膜条件1、3、4、5、6满足刻蚀率匹配要求。但图8扫描电子显微镜观察到的使用条件1、3、4、5、6成膜的样品,栅极过孔刻蚀截面有明显差异。其中条件3的刻蚀后PVX1层坡度角超过80°,ITO镀膜断线风险较大;条件1、5、6 PVX1层坡度角差异不大,均在66°左右;条件4坡度角为60.3°,相对最好。

以上虽然通过等离子增强化学气相沉积成膜优化已经得到了较好的成膜条件,PVX1层底切有明显改善,但从图8中可以看到最优条件4的PVX1刻蚀台阶仍比较明显,在PVX1、PVX2交界面可观察到轻微的尖角。这种情况可以通过干法刻蚀调整进一步优化。

图8 栅极过孔扫描电子显微镜图。(a)条件1;(b)条件3;(c)条件4;(d)条件5;(e)条件6。

3.3 PVX1刻蚀坡度角改善

为进一步改善膜层界面的刻蚀台阶,减缓刻蚀坡度角,在成膜条件4基础上按表2所示工艺条件使用增强型等离子体耦合干法刻蚀机进行干法刻蚀工艺优化实验,其中条件A为理论恶化条件(压力降低,物理刻蚀加强)作为参照,各实验条件对应的栅极过孔扫描电子显微镜图如图9所示。

表2 干法刻蚀工艺优化

(“-”表示同改善前条件)

图9 不同刻蚀条件栅极过孔扫描电子显微镜图。(a)条件A;(b)条件B;(c)条件C;(d)条件D。

增强型等离子体耦合干法刻蚀设备的主要特征是其下部电极接有13.56 MHz源极射频和3.2 MHz的偏置射频。其中源极射频频率相对高,主要用来解离反应气体,生成自由基和离子。带电粒子在源极射频产生的电场中运行距离短,对基板轰击作用小,主要依靠自由基与基板表面的薄膜发生反应进行化学性刻蚀。而偏置射频频率相对较低,波长长,带电粒子在偏置射频产生的电场中运行距离长,对基板表面的离子轰击效果较大,物理性刻蚀效果明显[12]。

干法刻蚀反应腔室的压力变化会直接影响等离子体密度和化学反应方向。压力升高反应腔室内化学活性的自由基和离子浓度增加,化学刻蚀作用增强,刻蚀坡度角会有降低趋势[13]。而压力降低时,离子之间、离子与原子之间碰撞减少且自由基浓度降低,横向刻蚀速率降低,离子轰击基板表面的物理刻蚀作用增强。

从图9中过孔扫描电子显微镜图像和PVX1层坡度角可以看出,条件A刻蚀压力降低,由于物理刻蚀增强,刻蚀坡度角恶化变大。而刻蚀压力变大、偏置射频功率降低的化学刻蚀增强条件B~D的刻蚀台阶均较表1中条件4对应的量产刻蚀条件的坡度角有所改善,其中压力和偏置射频功率变更组合条件D与仅变更压力或仅变更偏置射频功率的条件B、C相比,不仅PVX1层坡度角最小,而且PVX1层刻蚀台阶最短,几乎观察不到膜层界面尖角。条件A~C的栅极过孔扫描电子显微镜图像均能看到3种不同氮化硅绝缘膜层坡度角不同形成的3个斜坡,而条件D的PVX1、PVX2层的坡度角差异较小,过孔截面仅能看到两个膜层斜坡且膜层间台阶过渡自然平缓。

综合以上实验结果,使用成膜条件4进行PVX1层成膜并采用刻蚀条件D进行干法刻蚀可以解决“一步刻蚀”工艺流程的栅极过孔PVX1膜层底切问题,获得良好的刻蚀坡度角。

4 量产投入验证

对采用成膜条件4搭配刻蚀条件D的“一步刻蚀”工艺条件进行生产投入验证,“一步刻蚀”条件与量产条件各投入120张玻璃基板加工至TFT完成,进行阵列电学检试并通过阵列维修工序全抓图判定,统计DCS不良发生率,结果如图10所示。

图10 DCS改善前后良率对比。(a)DCS改善效果;(b)有机膜缺失型DCS改善效果。

从图10可以看出,采用优化后的“一步刻蚀”工艺,总DCS不良率较同批次量产条件下降了0.9%,而有机膜缺失型的DCS不良发生率降为0。说明优化后的新工艺流程可彻底改善顶像素电极设计HADS产品有机膜缺失型DCS不良。

5 结 论

本文从HADS有机膜产品DCS不良产生的机理入手,提出了PVX1刻蚀工序省略,在PVX2刻蚀时进行外围栅极跨接过孔处多层氮化硅“一步刻蚀”的工艺方案。通过优化PVX1成膜工艺进行刻蚀率匹配消除跨接过孔PVX1层底切不良,并在优化后的PVX1膜层基础上调整干法刻蚀工艺进一步改善过孔刻蚀坡度角和刻蚀台阶,使得过孔处膜层间台阶过渡自然平缓,实现“一步刻蚀”工艺的导入,HADS有机膜产品特有的有机膜缺失类型DCS不良得到彻底解决。新的工艺流程不仅提升了产品良率和产品在市场中的竞争力,还缩减了工艺步骤,大幅提升了产能,收到了良好的经济效益。实验中通过工艺流程变更进行不良改善的思路,以及等离子增强化学气相沉积、干法刻蚀工艺优化方法,也为新产品、新工艺的开发提供了指导和借鉴。