大数据量低延时航电中继系统设计与实现

樊智勇 鲁 彦 刘 涛

1(中国民航大学工程技术训练中心 天津 300300)2(中国民航大学电子信息与自动化学院 天津 300300)

0 引 言

民用飞机航空电子系统主要由通信、导航、自动飞行、综合显示等系统组成,其数据交联关系复杂,系统间数据交互量巨大[1]。近年来,民用飞机航电系统的升级改装需求逐渐增加,其改装方案评估需要在集成测试系统中进行大量数据交互[2-3]。为了解决集成测试系统中数据交互时面临的设备连接工作量大、易出错等问题,本文设计了一种作为中间件的航电中继系统。

1 系统定义及功能

航电中继系统是指在集成测试中能将不同类型航电信号在位于不同物理空间的航电系统组件或半实物仿真器之间进行大数据量、低延迟相互转发的中间件。针对集成测试数据交互需求的特点,航电中继系统需具备4个功能:多并发通道的数据转发;转发延迟时间在毫秒量级;不同物理空间实验室之间的传输距离可达数千米;转发过程中数据易于集中监控。

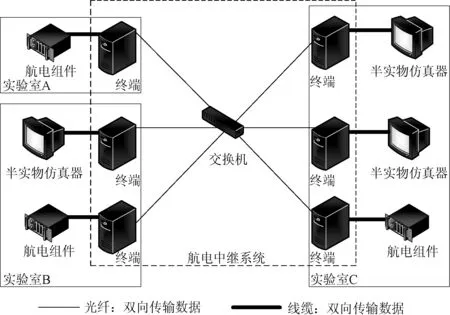

在集成测试数据交互问题的研究方面,Pan等[4]在研究半实物仿真的实时数据传输问题时,提出了基于反射内存中断的时钟同步方法,实现微秒级延迟表明反射内存技术的低延迟和延迟确定性。Sakakura等[5]研究了基于反射分布式内存的数据管理方案,监控整个测试环境,并支持数据中心对数据的实时修改,表明反射内存网络易于监控的特性。田赤军等[6]研究了远程实验室协同仿真问题,实现了千米级跨区域实时数据共享,表明反射内存网远程异地传输数据的优势。黎凡等[7]设计了光纤反射内存卡,应用于传输大规模高清图像,表明反射内存技术能进行大量数据传输。航电中继系统选择反射内存网络构建其底层数据通信支撑实现4个功能。图1为基于反射内存网的航电中继系统的功能示意图。

图1 航电中继系统的功能示意

航电中继系统由终端和交换机构成,其传输介质为光纤,每个终端构型相同。不同实验室的航电组件、半实物仿真器等只需和航电中继系统的终端连接,即可实现数据的收发功能。终端所连设备改变时,航电中继系统只需改变转发配置软件的设置,无须改变硬件布线。

2 系统设计

航电中继系统需要确定硬件配置和反射内存分配。硬件配置是选择进行集中监控和发布控制命令作用的计算机、运行转发应用的终端计算机、反射内存交换机等硬件;反射内存分配是将硬件通道资源与反射内存一一对应。

2.1 硬件配置

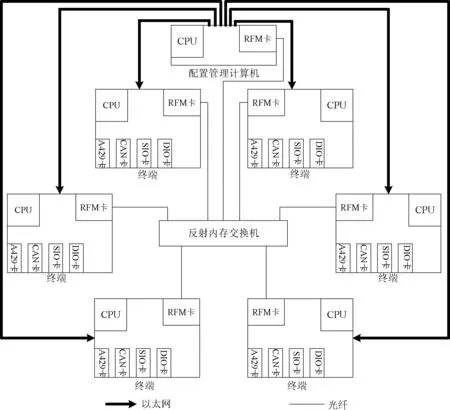

如图2所示,航电中继系统由1台配置管理计算机、6台终端计算机和1台反射内存交换机等组成。

图2 航电中继系统内部结构图

配置管理计算机是标准工控机,包含反射内存卡(RFM卡),通过以太网向终端机发布转发配置命令、转发应用的执行文件,通过本地反射内存卡对中继的数据进行集中监控。终端计算机由处理器、反射内存卡、ARINC429卡、CAN总线板卡、串行总线(SIO)卡和离散量(DIO)卡组成,实现8通道ARINC429数据、2通道CAN数据、4通道SIO数据和32通道DIO数据的接收和转发。反射内存交换机是一个8口的256 MB光纤交换机。

2.2 反射内存分配

根据民用飞机航电系统交互数据的类型可知,终端需要中继四种类型数据。在集成测试过程中数据交互量大,为了避免数据在中继过程中碰撞、丢失,同时充分利用反射内存,在反射内存分配时,进行四次分配,分配细化图如图3所示。不同终端机、不同型号板卡、不同通道(Channel)的读和写都对应不同的反射内存地址段,实现数据传输互不冲突。同时,反射内存网络具有错误管理和检测机制,保证数据无错传输[8]。由于系统转发数据量大,将每个通道读或通道写内存都设置一个FIFO队列缓存,队列长度为40个数据区大小。

图3 反射内存分配细化图

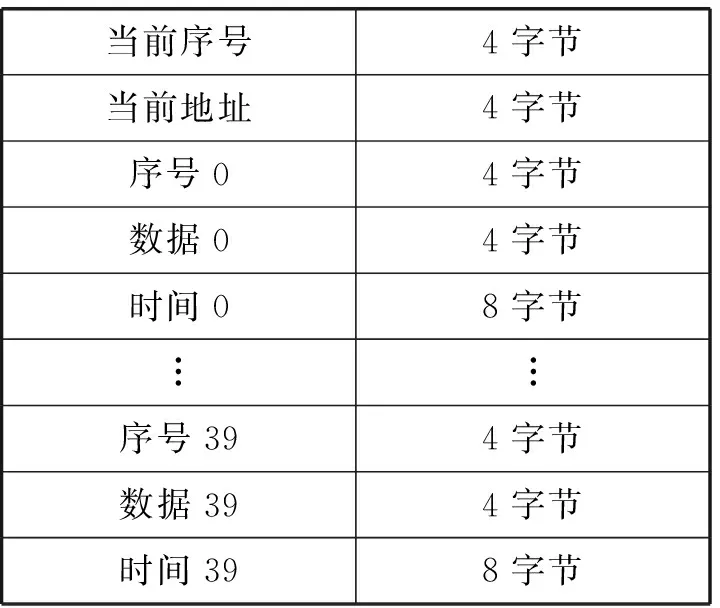

离散量(DIO)的分配方式不同于其他三种数据类型,其对应航电系统中的开关量,取值为0或1。由图3可知,为使反射内存利用率最大,DIO第四次分配时按位分配。为DIO设置两个FIFO队列缓存,队列长度为40×4字节。表1为DIO对应反射内存的FIFO存储格式,数据区4字节为32位,对应Channel 0到Channel 31共32个发送通道或接收通道内存。

表1 DIO对应反射内存FIFO存储格式

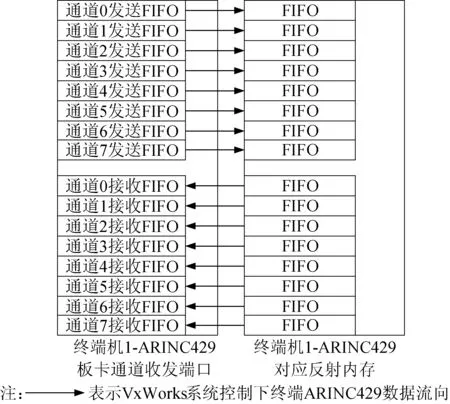

以ARINC429为例详细说明终端FIFO间数据流向,ARINC429数据对应16个FIFO缓存队列,终端板卡与反射内存FIFO间数据流向如图4所示。ARINC429板卡每个通道的接收或发送FIFO均对应一个反射内存FIFO,终端系统从ARINC429板卡FIFO中读数的原则是将前一个FIFO读空,读到的数均写入其对应的反射内存FIFO,再将下一个FIFO读空,写入其对应反射内存FIFO。依此循环读写,直到板卡FIFO中无数据为止。终端VxWorks系统时钟速率高于ARINC429板卡的硬件驱动程序执行速率,即外部组件发送数据存入ARINC429板卡FIFO的速率小于终端系统从中读数速率,此设计是为了避免数据丢失。以此类推,终端系统将数据从反射内存FIFO写入ARINC429板卡FIFO具有相同原理。

图4 终端FIFO间数据流向示意

3 终端中继转发逻辑设计

终端计算机在VxWorks操作系统的控制下以系统时钟速率轮询反射内存和4种板卡各通道内存的数据情况,依据FIFO不同的状态执行读写操作。中继转发逻辑由数据采集任务和数据激励任务实现,VxWorks系统任务占据0到50的优先级值,驱动任务占据51到99的优先级值[9],这两个应用任务的优先级值均设为100。系统运行时,VxWorks按照先进先出原则调度这两种任务。

以ARINC429为例阐述具体执行过程,图5为数据采集任务的流程图,其功能是使数据从接口板卡到反射内存。

图5 ARINC429数据采集任务的流程图

其执行过程如下:

(1) 终端机系统创建ARINC429数据采集任务。

(2) 终端机系统检查ARINC429板卡各通道的状态,若通道FIFO状态不空,则使能读FIFO数据函数(EnableReadFIFO)开始工作,终端机系统获取待接收数据的通道号。若通道FIFO状态为空,则在100次查询后仍空时结束运行。

(3) 接收数据函数(ReceiveData)执行,控制终端机接收此ARINC429数据。

(4) 终端机将接收数据写到反射内存对应通道读地址,同时反射内存网络在其共享内存机制的作用下,将此数据广播到其他终端机反射内存卡的相同通道读地址中。

(5) 终端机根据转发配置文件判断是否转发此数据。若转发,则转发的目标终端机根据获取的通道号等信息将此数据写到对应通道反射内存通道写地址中;若不转发,则结束运行。

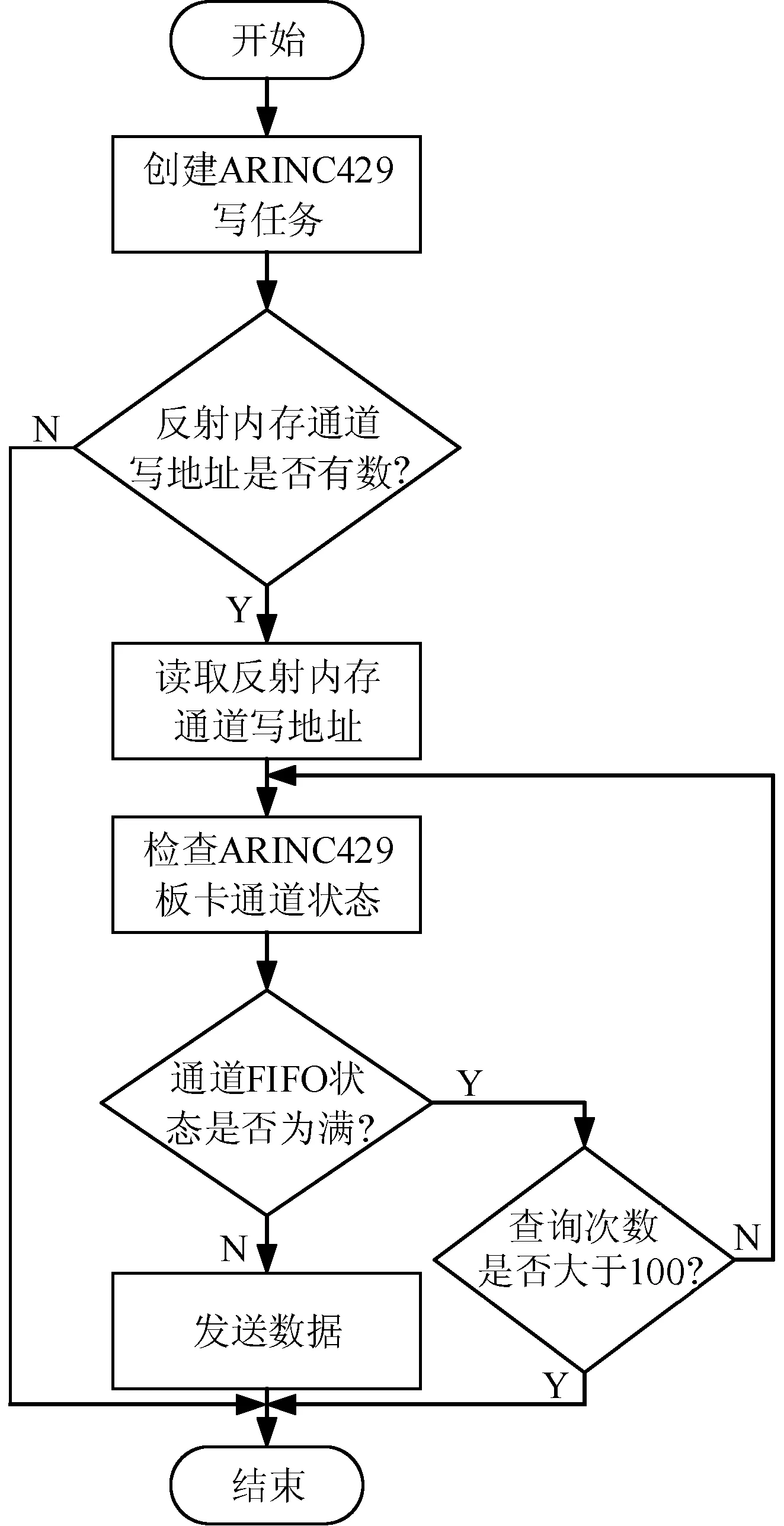

图6为数据激励任务的流程图,其功能是使数据从反射内存到接口板卡。

图6 ARINC429数据激励任务的流程图

其执行过程如下:

(1) 终端机系统创建ARINC429数据激励任务。

(2) 每个终端的每个ARINC429板卡的每个通道轮询反射内存通道写地址是否有数据,若无数据,则结束执行;若有数据,则对应终端机系统读取反射内存通道写地址数据。

(3) 终端机系统轮询ARINC429板卡各通道的状态是否为满。若通道FIFO状态不满,则调用数据发送函数(SendData),将此数据写到ARINC429板卡对应通道输出端口内存中,然后板卡基于硬件操作将数据输出给转发对象。若通道FIFO状态为满,则在100次查询后仍满时结束运行。

(4) 采集任务和激励任务均设定100次查询的目的是防止没有数据转发时程序进入死循环,影响系统运行效率。

终端中继转发功能是由采集任务和激励任务协作实现的,将ARINC429数据存入反射内存通道读地址,反射内存网络依据其自动更新机制将数据广播到其他终端的同一反射内存通道读地址中,所有终端系统依据转发配置决定是否对本地反射内存通道写地址执行写数操作。

4 实 验

4.1 延时分析

航电中继系统数据转发延迟时间T是指从输入端发送数据至航电中继系统转发后输出端接收到数据这两个时刻的间隔时间,是衡量中继系统性能的重要指标。

(1)

t1=m/B

(2)

式中:t1为操作系统控制处理器读取以速率B发送的各类型数据的时间;m为一帧数据的位数;t2为航电中继系统进行数据转发时,终端操作系统执行读操作命令要依次遍历板卡通道的时间;t3为此过程中等待任务循环调度信号量的时间;t4为终端系统执行写操作依次检查板卡通道状态的时间;t5为此过程中释放信号量的时间;t6为单级反射内存交换机消耗的时间;t7为光纤传输时间。

4.2 实验分析

系统验证实验以转发ARINC429数据为例,测量扩展多个并发通道转发大量数据的延迟时间,实验结果取每个通道的延迟时间的平均值。采用长度为2 km的光纤,ARINC429信号发射器以12.5 kbit/s的速率发送数据,进行3组不同数据量的转发实验。

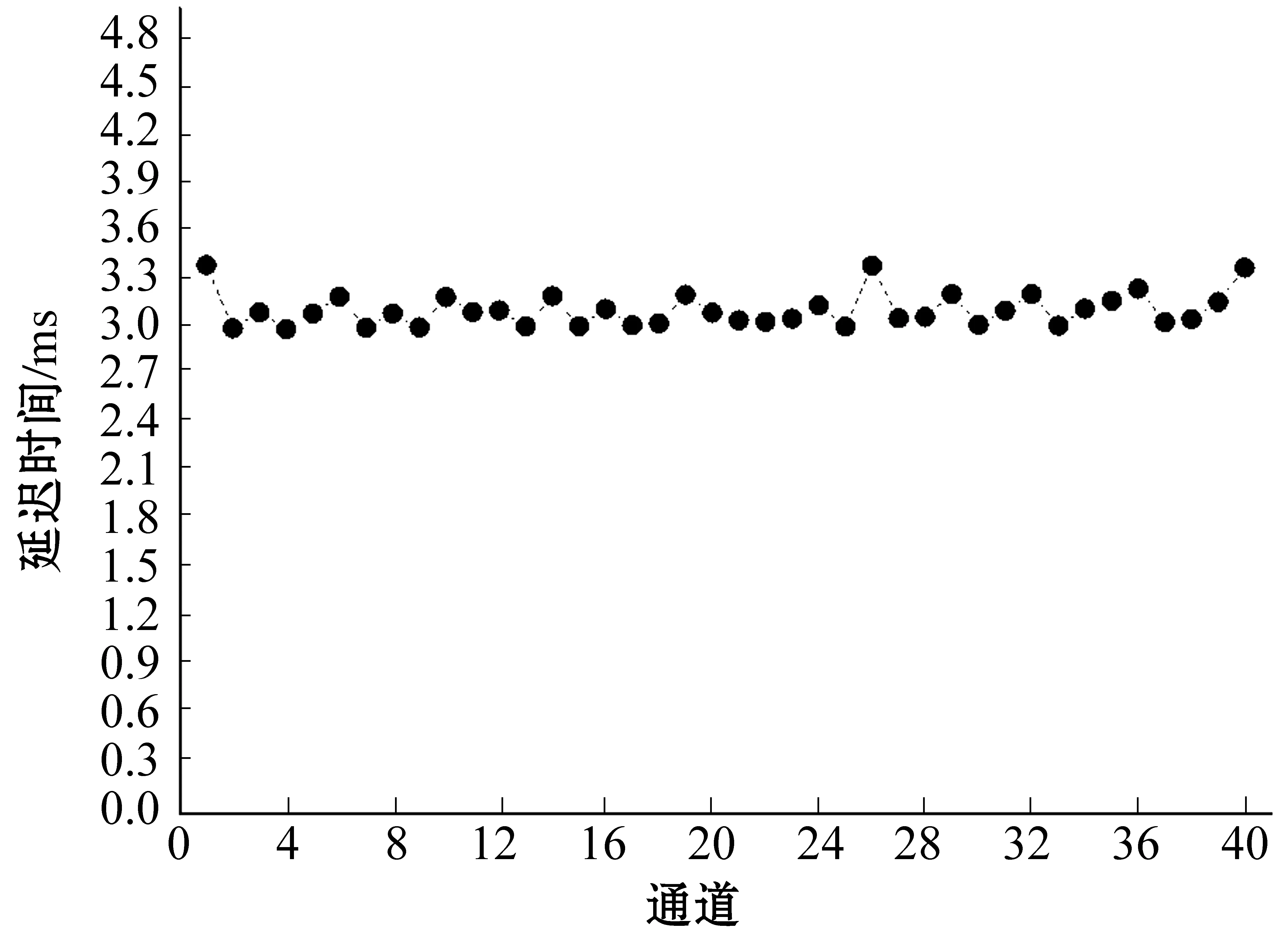

(1) 一对一转发。将终端机1的ARINC429板卡8个通道输入端口接ARINC429信号发射器,在配置管理计算机上设置转发配置,将终端机1的8个通道输入数据分别转发给终端机2至6的8个通道。利用ARINC429信号接收器测量各通道输出数据,结果均准确。利用示波器测量源信号和各通道转发输出信号的延迟时间,如图7所示,a表示系统只转发到终端机2的8个通道的延时均小于3.50 ms,b对应延时均小于3.42 ms,c对应延时均小于3.29 ms,d对应延时均小于3.36 ms,e对应延时均小于3.45 ms。因此,系统8个并发通道的数据转发延时小于3.50 ms。

图7 只转发到一个终端的延迟时间

(2) 一对多转发。终端机1的8个通道接ARINC429信号发射器,同时转发给终端机2至6的40个通道。利用ARINC429信号接收器测量各通道输出数据,结果均准确。利用示波器测量源信号和各通道转发输出信号的延迟时间,如图8所示。图中40个点对应时间均小于3.40 ms,即系统40个并发通道的数据转发延时小于3.40 ms。

图8 转发到5个终端机40个并发通道延迟时间

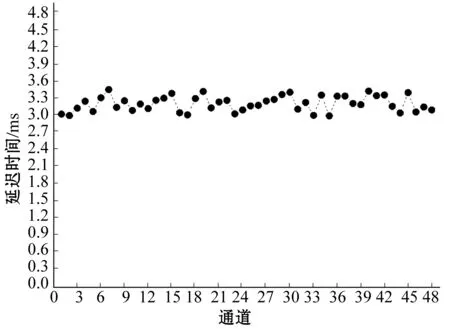

(3) 多对多转发。终端机1至6的48个通道接ARINC429信号发射器,同时转发给终端机1至6的48个通道,6个终端相互转发,任意一个目标通道只设置一个源通道对其转发。利用ARINC429信号接收器测量目标通道输出数据,结果均准确。利用示波器测量源信号和目标通道输出信号的延迟时间,如图9所示。图中48个点对应时间均小于3.48 ms,即系统48个并发通道相互转发的延时小于3.48 ms。

图9 6个终端48个并发通道相互转发延迟时间

实验结果表明,系统中继的并发通道数从8增加到48,转发大量数据的延时T均小于3.50 ms。其中t1为2.56 ms,t6为2.00 μs,与反射内存技术有关[10],t7为13.30 μs,t2至t5与终端系统效率有关,大小为微秒级。因此,固定延迟时间为2.58 ms,系统实际延时小于920.00 μs。

5 结 语

本文设计的航电中继系统,实现了远程异地进行ARINC429数据的40个(不包含本地终端)并发通道转发、串行数据(SIO)的20个并发通道转发、CAN数据的10个并发通道转发、离散量(DIO)数据的160个并发通道转发功能。该系统对4种类型数据均能够以反射内存交换机级联的方式扩展更多并发通道进行转发,并且系统稳定运行的实际延迟时间为微秒级。航电中继系统已应用于大型民用飞机航电系统升级改装项目,项目研发效率显著提高。