一种基于AD9266和AD9361的卫星中频信道设计

宋 颖,朱小流

(南京熊猫汉达科技有限公司,江苏 南京 210000)

1 应用背景

随着卫星通信技术发展,对设备的体积、功耗、集成化程度要求越来越苛刻,这必然需要在一个较小的空间同时实现中频下行接收通道和中频上行发送通道,完成AD/DA的转换;进行数字信号处理,并完成与外部设备的通信交互。由于数字电路“0/1”跳变的特性,随着处理频率的提高,其对模拟信号电路的影响越来越大,且不可忽略[1-2]。在设计模拟中频通道时,必须采取保护措施,屏蔽来自数字电路的干扰;或采取合理的设计,增强模拟电路自身的抗干扰能力。

2 设计实现

本设计可分为中频下行接收通道、中频上行发送通道、AD/DA转换电路3部分组成。

2.1 中频下行接收通道能力

(1)中心频率:2 180~2 200 MHz,步进100 Hz。

(2)信号带宽:30 kHz。

(3)输入电平:-100~-70 dBm。

2.2 中频上行发送通道能力

(1)中心频率:1 970~2 010 MHz,步进100 Hz。

(2)输出电平:-15~-15 dBm。

(3)相位噪声:

≤-60 dBc/@100 Hz;

≤-70 dBc/@1 kHz;

≤-80 dBc/@10 kHz;

≤-90 dBc/@100 kHz。

(4)输出杂散:≤-70 dBc。

(5)载波泄露:≤-40 dBc。

2.3 AD/DA转换电路

A/D转换电路由高性能的AD芯片AD9266实现,D/A转换由芯片AD9361实现。AD9361既能实现A/D转换,又能实现D/A转换,但本设计中只使用其D/A转换部分功能。这是由于AD9361的下行接收滤波带宽只有200 kHz,而本设中下行接收信号带宽为30 kHz,未减小数字信号处理的难度,故未使用AD9361设计下行接收通道。

本设计在有限的空间内,同时实现了高灵敏度、大动态范围的下行接收通道和具有高质量相位噪声、杂散、载波泄露性能的上行发送通道。最小接收电平“-100 dBm”和最大输出电平“+15 dBm”之间的电平差达“115 dBm”。这使得本设计具有更广泛的应用范围,可以应用在多种卫星通信环境中,同时也增加了设计的难度。

3 方案原理

3.1 下行接收通道

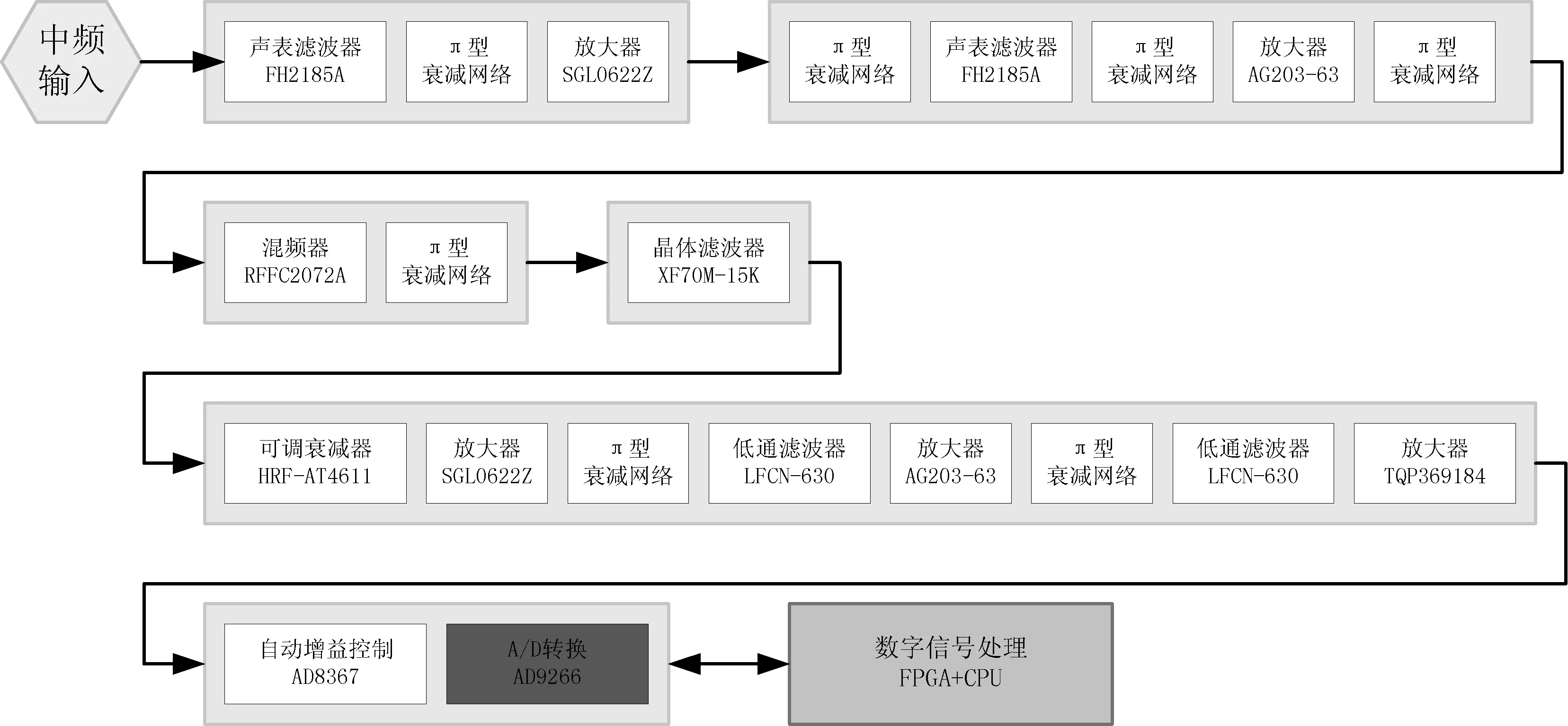

下行接收通道采用超外差架构技术,主要由放大器、数控衰减器、混频器、锁相本振源、声表面滤波器、中频放大器和低通滤波器等部分组成[3]。来自射频前端组件输入的中频信号,经过放大和滤波后,通过混频器将其搬移至70 MHz处,滤波器带宽为30 kHz。由于单个声表面滤波器抑制带外干扰能力有限,在本设计中采用了两级级联声表面滤波器抑制带外干扰;混频后通过晶体滤波器和低通滤波器共同抑制本振信号泄露信号和其他干扰噪声;最后经过自动增益控制AGC电路调整后,将70 MHz低中频信号传送至AD9266转换成数字信号,发送给基带FPGA、CPU等处理。下行接收通道方案设计如图1所示。

图1 下行接收通道方案原理

由于下行接收通道的输入信号最低只有“-100 dBm”,因此必须经过足够的放大处理,才能被A/D转换芯片AD9266处理。如果采用一级放大电路,放大倍数必然很大,容易造成自激,故在本设计中采用了多级级联放大滤波的方案,且在硬件设计中每级均用屏蔽罩盖住,以阻止本级电路向外的辐射电磁干扰,并屏蔽外部电磁辐射干扰。在上图中每个框均为一级,每级均用屏蔽罩盖住;在混频前有两级,混频后有3级。下行接收通道的增益分配如图2所示。

图2 下行接收通道增益分配

3.2 上行发送通道

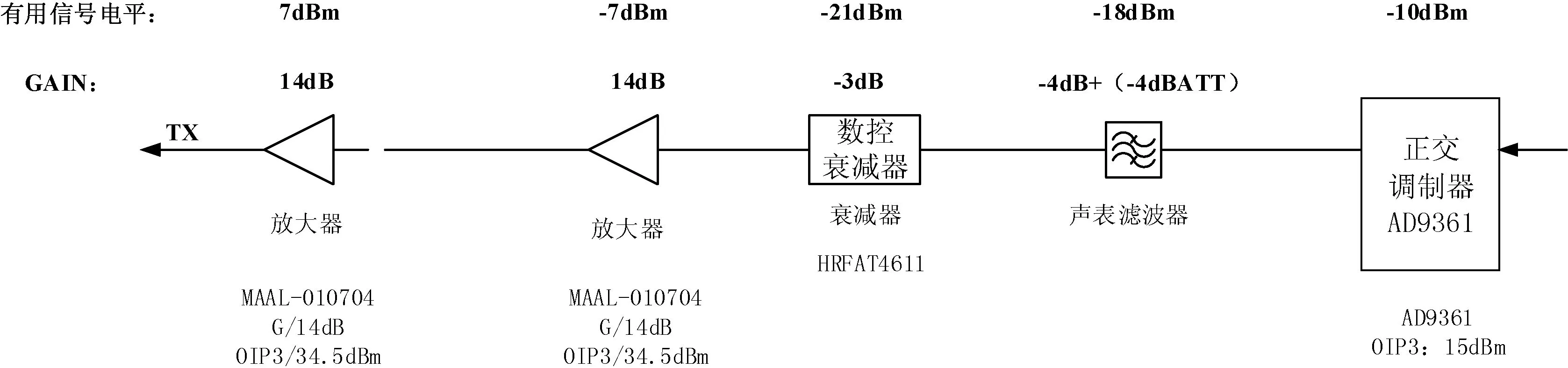

上行发送通道采用零中频方案,即基带直接调制至中频工作频点,主要由AD9361、声表面滤波器、放大器和可控衰减器组成。AD9361是一款优秀的数模转换芯片,其上行通道中集成了放大器、高性能锁相环和IQ调制/解调器,这无疑减小了设计的复杂度和印制板布局空间需求。声表面滤波器用于滤除中频信号带外干扰,使得发送的信号更纯净。数控衰减器用于调整发送信号的电平大小。上行发送通道方案设计如图3所示。

图3 上行发送通道设计方案

因为AD9361集成了小数N分频锁相环,IQ调制/解调等功能,因此其电路比下行接收通道简洁得多。但是仍然不能忽视最大发送电平“+15 dBm”这一指标。首先,最大发送电平信号易干扰具有高灵敏度的下行小信号接收通道;其次,要满足这么大的发送电平,必然需要高增益的发送器,处理不好,易产生自激。在本设计中上行发送通道采用三级级联放大滤波结构,每级均用屏蔽罩盖住,减少辐射和干扰。上行发送通道增益分配如图4所示。

图4 上行发送通道增益分配

4 结语

本文只给出了一路下行接收通道和一路上行通道的设计方案,但该方案的适用范围不仅限于一收一发的应用。在实际应用中,采用本设计方案,在190 mm×140 mm的印制板上同时实现了3路下行通道和2路上行通道,并具有高速的FPGA,CPU数字信号处理电路。