基于FPGA的六维并联机构的数据采集系统设计

孙嘉霖,李艳辉,霍 琦,李 昂

(中国科学院长春光学精密机械与物理研究所,长春 130033)

0 引言

在大口径空间光学望远镜中,由于加工中存在误差,环境因素导致的材料形变,都会对望远镜的成像效果产生影响,无法达到预期的成像要求[1]。因此,为了满足高精度望远镜位姿调整的六维并联机构就应运而生,而位姿的调整需要接收6组编码器数值。

传统的系统设计将现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)与编码器端直接连接,通过BISS-C协议能够正确地接受单个编码器的数据来进行电机控制[2]。但在实际的运动控制的应用条件下,单个编码器的数据不足以反映整个运动控制系统的运动状态。因此,需要并行采集多个编码器的数据来满足对精密机械的控制[3]。而对于多路编码器的数据采集,赵洪深等[4]采用FPGA和多路选择器进行组合来进行数据采集的,但由于多路选择器的使用,丧失了编码器数据接收的实时性,无法满足电机控制过程中编码器数据实时性的要求。张立等[5]使用FPGA对多路数据进行并行采集,并用单片机进行数据处理和传输的,但针对于六足平台的控制来讲,FPGA编程的灵活性更强,更适合用来进行运动控制程序的设计开发及验证。而如果只用一片FPGA芯片进行多组编码器数据的并行处理,不仅占用了大量IO端口,增加了主控FPGA的运算量,而且由于时序信号(MA)与数据信号(SLO)差分处理,控制端与六维并联机构间连接线缆数量为24根,线缆数量较多,给整个运动控制系统增加了负担[6]。

基于上述原因,本文设计的系统由2片FPGA来进行实现,编码器端FPGA负责六维并联机构支腿上的编码器数据采集,将采集到的6组编码器数据整合后,等待控制端的时序信号MA来到时,将实时更新整合的编码器数据发送到控制端FPGA处。如此设计该系统后,软件方面上减少了六维并联机构运动控制端FPGA的运算处理量,使得运动控制单元能够提供更多的运算处理单元,提供给控制算法,留给控制算法更大的空间来进行优化处理运动过程中的问题。硬件方面上,减少了控制端与六维并联平台间连接线数量,由原来的24根线缆减少为4根,同时也减少了占用的控制端FPGA的端口。最后通过实物验证实验,验证了编码器端FPGA能够正确接收6组编码器数据,并进行校验,控制端FPGA能够接收并解算出6组编码器数据,数据传输过程稳定可靠。

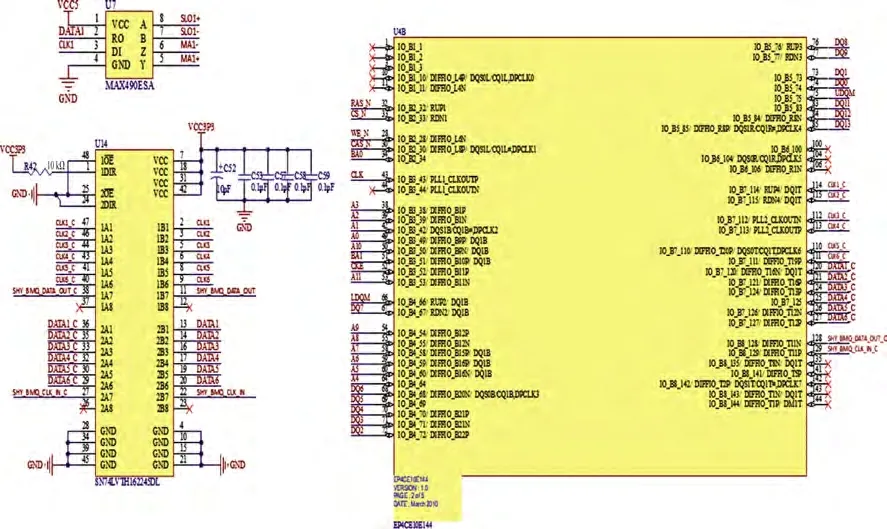

图1 FPGA硬件电路原理Figure1 FPGA hardwarecircuit schematic diagram

1 硬件电路设计

该数据传送系统的硬件分为编码器端FPGA和控制端FPGA两部分组成。

首先介绍编码器端FPGA硬件电路的设计,硬件原理如图1所示,以其中一个编码器数据接收为例,编码器数据直接接收端接收编码器发出的时序MA的差分信号(MA1+和MA1-)并接收数据SLO差分信号(SLO1+和SLO1-),4条信号线通过MAX490EAS将差分信号SLO与MA转化为单端信号DATA1与CLK1。该单端信号通过具有三态输出的3.3 V-ABT-16位总线收发器SN74LVTH162245DL,将单端信号DATA1与CLK1转化为可直接连接芯片引脚的DATA1_C与CLK1_C,来进行编码器数据的收发,该部分芯片采用的是Altera公司的EP4CE10E22C8N。

编码器数据间接接收端为进行试验验证,采用的是SPARTAN-6系列的开发板替代了六足平台的控制电箱,FPGA芯片型号为XC6SLX45。

2 数据收发原理及FPGA软件设计

2.1 CRC校验的基本原理及计算

CRC检验的基本原理就是通过在正常的二进制k位数据后面,通过固定的运算关系,生成一个r位的校验位,构成一个n=k+r位的数据,通过在接收端检测接收到的数据关系,来判断在传输数据的过程中,是否发生错误[7]。CRC校验的基本原理可以用下式来表明:式 中: M=xTu(x),u(x)=un-l-1xn-l-1+…+u1x+u0;r=n-k;R=vr-1xr-1+…+v1x+v0;g(x)=gn-kxn-k+gn-k-1xn-k-1+…+g1x+g0。

M(Message)为传输信息部分的多项式,R(Remainder)为校验部分的多项式,r为检验部分的位数,k为信息字段的位数,G为约定生成的多项式。对于发送端来说,通过需要传输的信息M和确定的G,可以生成对应信息M的一个校验字段R。将R附加在M后面构成新的多项式V=Mxr+R,将新的多项式V发送到接收端。对于接收端来说,将接收到的V与G用模二除法进行运算,余数为0,则表示传输信息正确。

2.2 FPGA软件流程设计

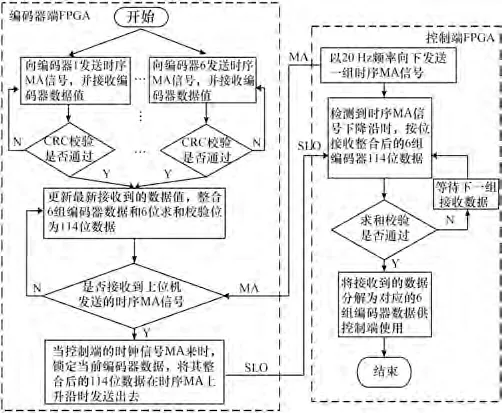

编码器数据采集系统软件流程如图2所示。

图2 编码器数据采集系统软件流程Figure2 Flow chart of system software of encoder data acquisition system

首先,编码器端FPGA接收6组编码器,并进行CRC校验,校验成功后,编码器端FPGA对6组编码器数据进行整合,6只光电编码器软件处理后得到各自18位数据,其中,前15位为有效二进制数位(高位在前,低位在后),后3位为该编码器当前时刻状态值(可以用此值判断当前编码器状态是否异常)。这样,每一数据包包含6只光电编码器108位数据,编码器端FPGA将从108位数据最高位起,每6位为一段,通过这个样的方式获取18段6位数据,将18段数据累加求和,最后以累加和的6位数据作为求和校验位,高位在前,低位在后。当接收到控制端FPGA发送的时序MA信号时,送出这108位数据和6位的求和校验位。

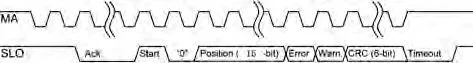

2.3 编码器接收数据时序图

编码器端的FPGA与编码器间的通信是采用Biss C模式的通信协议对6只编码器的数据进行采集。6只编码器的MA发送及SLO接收都是由一片FPGA进行控制,接收到编码器数据后,对数据进行CRC校验,检验通过后更新当前编码器的返回值。各个编码器的接收数据时序图如图3所示。

图3 编码器接收数据时序图Figure3 Encoder receives thedata timesequencediagram

在MA没来到的时候,SLO一直处于高电平状态,完成确认周期Ack后,会进入高电平Star位和“0”位并传输数据,数据传输完毕后,SLO会进入低电平超时周期Timeout,编码器准备好进行下一个周期的数据传输时,SLO会置为高电平来提示FPGA端接口[8]。

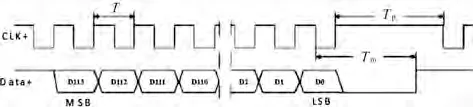

控制端FPGA读取数据采用SSI串行的方式进行数据输入,时序图如图4所示。

图4 控制器读取数据时序图Figure4 Thecontroller reads thedatasequencediagram

当时序的上升沿到来时,编码器端FPGA开始发送整合后114位数据,其中Tm为低电平持续时间,约30μs,Tp为时钟持续高电平,这里Tp≥Tm。在每次SSI通讯完毕后,首先对接收到的数据进行校验位校验,如果校验通过,则将该组数据保留用以六足平台的控制,否则舍弃该组数据,等待下一组数据的到来[9]。

3 实验结果及分析

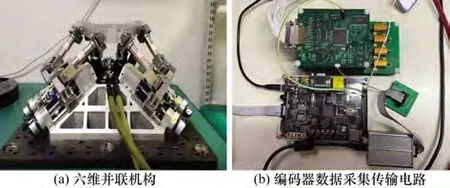

该编码器数据采集系统将应用于六维并联机构上采集编码器数据,六维并联机构及2块FPGA编码器数据采集传输板如图5所示。

图5 六维并联机构与编码器数据采集传输电路Figure5 Six-dimensional Parallel platform and encoder data collection transmission circuit

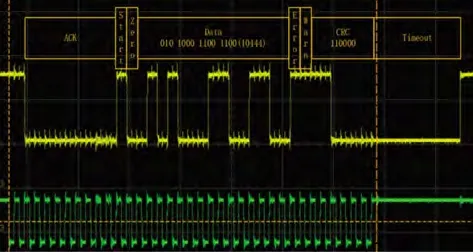

采集单个编码器数据的数据传输过程如图6所示,当编码器接收到时序信号MA时,会按照图2所示时序向编码器直接接收端通过SLO发送相应编码器数据,所传输的数据用二进制表示为“010 1000 1100 1100”,转化为十进制表示为10444。编码器端CRC校验采用的校验多项式为x6+x1+x0,生成的校验码为“110000”。

图6 编码器1数据接收波形Figure6 Encoder 1 datareceive waveform

图7所示为两个FPGA之间的数据传输过程。当接受到控制端FPGA发送的时序信号MA时,采集端FPGA会将整合好的114位数据通过数据SLO发送出去。由于示波器屏幕显示限制,将该信号用ChipScope进行抓取分析,如图8所示,传输的114位数据信号以十六进制显示为“7944DBB766B3BF0F39108E”。

图7 SSI协议传输过程示波器采集信号Figure7 SSIprotocol transfer processoscilloscopecollection signal

图8 控制端接收数据过程波形Figure8 Control end receivesthedataprocess waveform

图9所示为通过Quartus中的Signal Tap和ISE的Chip Scope来抓取到的数据传输过程中的信号。由图可知,控制端FPGA可以正确的接收到由6组编码器数据整合后的114位数据,并以编码器1为例,对数据进行解算,接收到的编码器数据与传送前的编码器数据码值一致,均为10444。

图9 SSI协议发送端与接收端数据对比Figure9 SSIprotocol sendingend and receiving end datacontrast

4 结束语

经过实物实验验证,编码器数据采集端FPGA通过BISSC协议,并经过CRC校验,能够正确地采集6组编码器的当前码值,通过对采集到的编码器数据进行整合,控制端FPGA通过SSI协议与求和校验,能够正确解算出所传输过来的编码器数据。该方案能够很好地解决直接接收的多编码器数据方案中传输线缆过多,占用FPGA端口过多与单独FPGA处理6组编码器数据运算量大的问题。实验证明,该系统工作状态稳定,数据传输正确,能够满足六维并联机构控制所需要的编码器数据采集需求。