一种基于SRAM工艺FPGA的防克隆保护方法*

刘 贺,刘 瑶,杨 竞,王小骥,刘星江

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引 言

以现场可编程逻辑门阵列(Field-Programmable Gate Array,FPGA)为核心的可编程逻辑器件(Programmable Logic Device,PLD)因具有用户可编程和在线动态重构的特性,方便了电子产品设计的修改和升级,提高了产品的灵活性和通用能力,缩短了产品的开发和上市时间,在现今的电子系统中得到广泛的应用和迅速的发展。

在FPGA中使用的设计和配置数据代表了系统中知识产权的重要部分,然而FPGA设计面临着克隆(Cloning)、反向工程(Reverse Engineering)、篡改(Tampering)和过度构建(Overbuildering)等威胁[1]。其中克隆是指通过复制获得FPGA设计的相同副本,而不需要理解它是如何工作的,窃取方即可零设计成本仿造、伪造产品,这极大地损害了正品厂商的品牌声誉和利益,随着竞争变得越发激烈,FPGA内部设计电路和知识产权的安全性成为产品市场化必须考虑的因素[2]。

基于静态随机存取存储器(Static Random-Access Memory,SRAM)工艺的FPGA具有易失性,每次上电都需由外部进行重新配置,这使得剽窃者可以轻松通过对FPGA的配置数据引脚进行采样,得到该FPGA的配置数据流,实现对FPGA内部设计电路的克隆。

基于反熔丝等技术的FPGA芯片虽然可以很好地解决防克隆、逆向工程破解、篡改等问题,但限于如规模、成本或技术等各方面的原因,在国内外基于SRAM工艺的FPGA仍处于主流地位。这使得对基于SRAM工艺的FPGA芯片的防克隆研究具有重要现实意义。

为此,本文提出一种由FPGA外置安全电路结合杂凑算法(HMAC方式)和伪随机序列生成等技术手段进行合法性认证检测来提高FPGA防克隆的安全设计方法。

1 技术理论支撑

本文综合运用了杂凑密码算法的可认证性、FPGA器件本身固有的组合电路因竞争冒险现象而导致信号变化的不确定特性、线性反馈移位寄存器的简单易于硬件实现特性,构建了FPGA基于密码的一次一认证防克隆安全保护手段。

1.1 杂凑算法

杂凑算法可以将任意长度的消息压缩成固定长度的摘要。给定1个消息计算其杂凑值是容易的,但是找到具有相同杂凑值的2个不同消息是困难的。除了数据压缩、易于计算这两个基本属性,杂凑算法还满足三个安全属性:单向性(抗原像攻击)、弱抗碰撞性(抗第二原像攻击)、强抗碰撞性(抗碰撞攻击)[3]。哈希信息验证码(Keyed-Hashing for Message Authentication,HMAC)用秘密密钥与杂凑算法结合来产生固定长度消息认证码,其安全性建立在杂凑算法基础上,可用来作加密、数字签名、报文验证等。

1.2 竞争与冒险

信号在FPGA器件内部通过连线和逻辑门时,都有一定的延时,延时的大小与连线的长短和门单元的数目有关,同时还受器件的制造工艺(片与片间有物理误差)、工作电压(供电也有误差)、温度等因素的影响。在门电路中,两个输入信号同时向两个相反方向的逻辑状态转换,即一个从低电平变为高电平,另一个从高电平变为低电平,或反之,称为竞争。由于竞争而在电路的输出端可能产生尖峰脉冲的现象称为冒险。

数字电路设计中的竞争和冒险现象所导致的不确定性是十分头疼的问题,本文将利用这种因不确定性而导致的数据采样不可预测特性来完成保护设计。

1.3 线性反馈移位寄存器

线性反馈移位寄存器是指给定前一状态的输出,将该输出的线性函数再用作输入的移位寄存器,其结构简单、容易实现、成本低、性能优,非常适合用于硬件实现[4],在通信系统中常用于构成伪随机数发生器。其特性通常由移位寄存器级数、初始状态、反馈逻辑和时钟周期等共同决定。

2 方案设计

本文在参考文献[5]和文献[6]的设计方法和理念基础上进行方案设计,其中文献[5]的方法为在CPLD和FPGA中预置8组相同的密钥表,通过每次传递不同的随机数来同步双方密钥选择,使用M序列(Maximum-length Sequences,最长线性反馈移位寄存器序列)对选定的密钥加密后由解密方确认双方选择的密钥是否一致来判定FPGA使用是否合法,该方法主要通过M序列算法安全强度来保证FPGA内IP core的合法使用,可选择的密钥只有有限组,在M序列算法被破译后,克隆方可通过截获、分析线路数据并通过穷举方式,根据规则重放模拟认证过程。文献[6]通过外置安全电路对FPGA进行基于杂凑算法和AES算法的身份认证、产权认证的双重认证保护,杂凑算法仅用于保护数据完整性,其FPGA身份认证过程交互较为复杂,需要两种算法支撑,从而额外消耗大量硬件资源,并且对外置安全芯片的安全性和性能也具有较高要求。同时其设计中以口令为输入条件的认证方式,只适用于具备人机接口的设备使用,应用范围受限。

本文在上述研究基础上,以不浪费系统资源、不增加系统开销负担,同时考虑经济效益与破译复杂度间进行平衡为原则,在有限范围内保证设计安全性,达到防克隆的安全设计方法安全、可用、好用的目的,结合并继承前述两种安全设计方法各自的优点,同时进行适当的优化设计。

2.1 系统框图

方案的设计核心为以增加外置安全保护电路方式配合FPGA完成上电后的合法性单向认证过程,认证由FPGA中保护模块和外置安全保护电路交互实现。需保护的IP core在上电后不能正常工作,只有对外置安全保护电路的合法性进行认证成功后,IP core才能获取自身参数完成启用过程。

同时,不同于前述方案中FPGA合法性认证成功后以单一使能信号启用IP core的方式,本方案根据IP core的设计特性,提取其中参与完成核心功能的重要参数信息作为IP core启动钥匙,在使用合法性认证成功后,内部控制电路将此信息传递给IP core以完成启用过程,同时该参数信息作为密钥参与认证过程的保护,将保护对象与保护过程一体化融合设计。

认证过程利用可编程逻辑器件在应用设计过程中的竞争与冒险现象并结合线性反馈移位寄存器的简单易于硬件实现特性,产生随机特性良好的随机数作为不可重复的认证变量,利用杂凑算法的HMAC方式良好的基于密码的认证特性对认证过程加以保护,达到FPGA对外置保护电路的合法性保护。

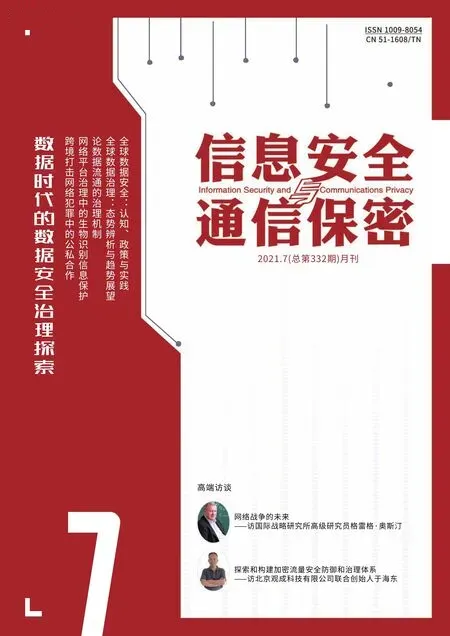

本方案设计的系统框图如图1所示。

图1 系统框图

安全保护电路作为设计的重要部分,其自身的安全性与整体设计强相关,以达到ASIC的安全水平为目标,综合考虑设计成本、使用维护方便度以及该电路承载的设计实现复杂度较低的特点,本方案选用上电自启动且难以通过物理手段进行反向工程的CPLD或小规模反熔丝FGPA进行设计。同时从更经济角度考虑,也可以与供电电池配合使用小规模SRAM工艺FPGA进行设计,在设备出厂前通过JTAG对其加载配置文件,在其使用生命周期内由电池维护其内部程序,无需重新加载,同样可具备较好的安全特性。

随机序列生成模块实现认证过程随机数据生成功能,其根据使用环境的电压、温度等环境特性结合各类芯片个体固有的物理差异特性,保证每次认证过程中FPGA使用该模块自主生成不可预测、不重复的随机数据,防止克隆方采集线路数据重放以仿冒认证过程。

IP core参数存储模块对IP core的核心功能要素进行抽象提取,在认证过程充当认证保护密钥,在认证成功后作为启用钥匙辅助完成IP core的功能启用。

杂凑算法模块承担认证过程校验值计算功能,使用其HMAC方式,以IP core中抽取的核心参数作为密钥,进行认证数据的完整性及可认证性保护,以基于密码的安全特性保证安全保护电路的合法性。在设计验证时使用国家密码管理局发布的SM3杂凑算法,其安全性和效率与SHA-256相当,实际使用时可根据情况简化设计,在一定安全范围内降低算法的实现规模。

安全保护电路内部的随机序列检测模块,在内部保存多组已认证过的随机数,对新启用的随机数进行重复性检测,检测到重放数据则终止认证过程。

FPGA内部的合法性验证模块将FPGA计算生成的校验码与安全保护电路生成的校验码进行一致性校验比对,通过后由安全控制电路提取IP core参数,使能IP core的全部功能。

2.2 工作流程

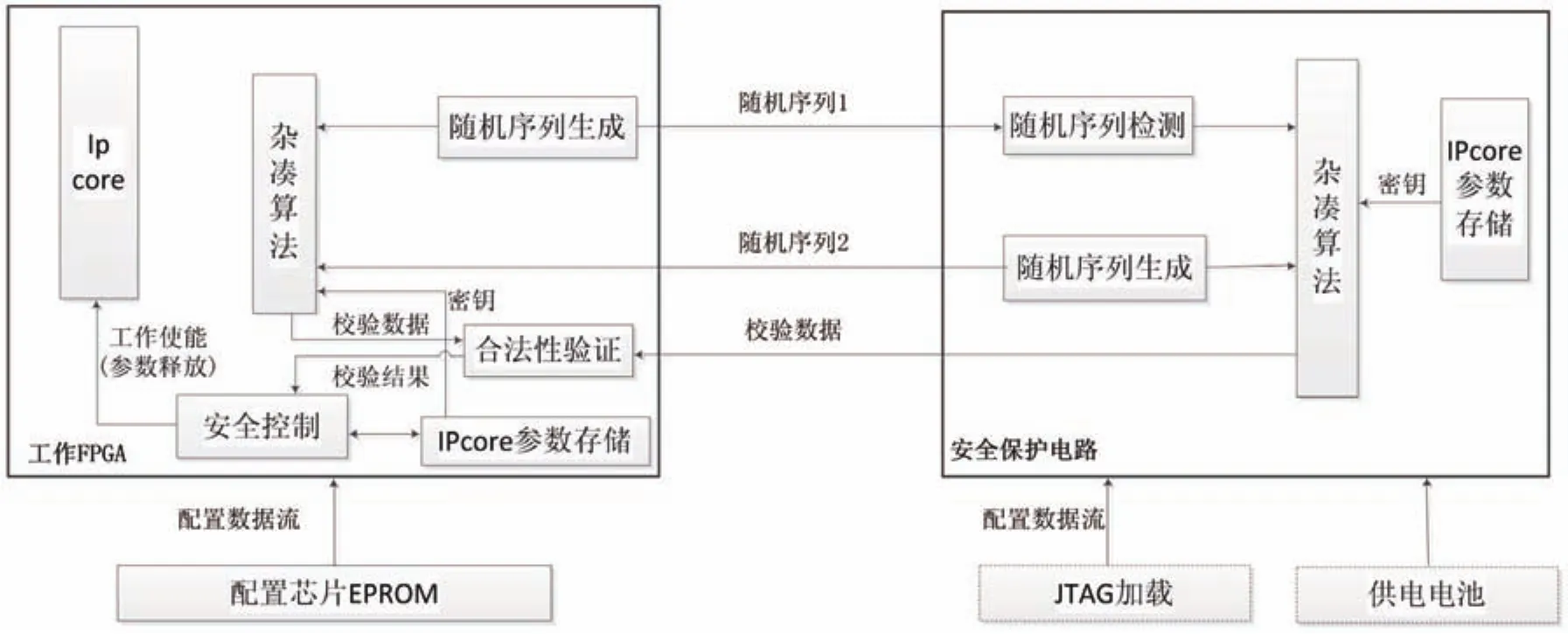

本方案的工作流程如图2所示。

图2 工作流程

认证交互流程:

(1)FPGA上电后,通过随机序列生成模块发送随机序列1。

(2)安全保护电路检测随机数是否重复,如不重复使用自身的随机序列生成模块生成随机序列2,使用IP core参数和杂凑算法的HMAC方式计算序列1、2的杂凑值,将随机序列2与杂凑值发送给FPGA。

(3)FPGA接收随机序列2后,以同样方式计算序列1、2的杂凑值与安全保护电路杂凑值进行比对。

(4)校验成功,则FPGA释放IP core参数,使能IP core。

3 关键模块的设计实现

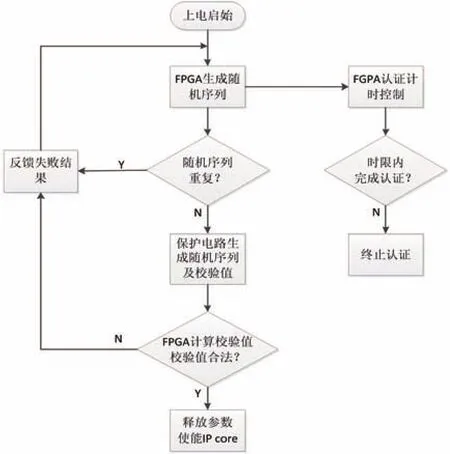

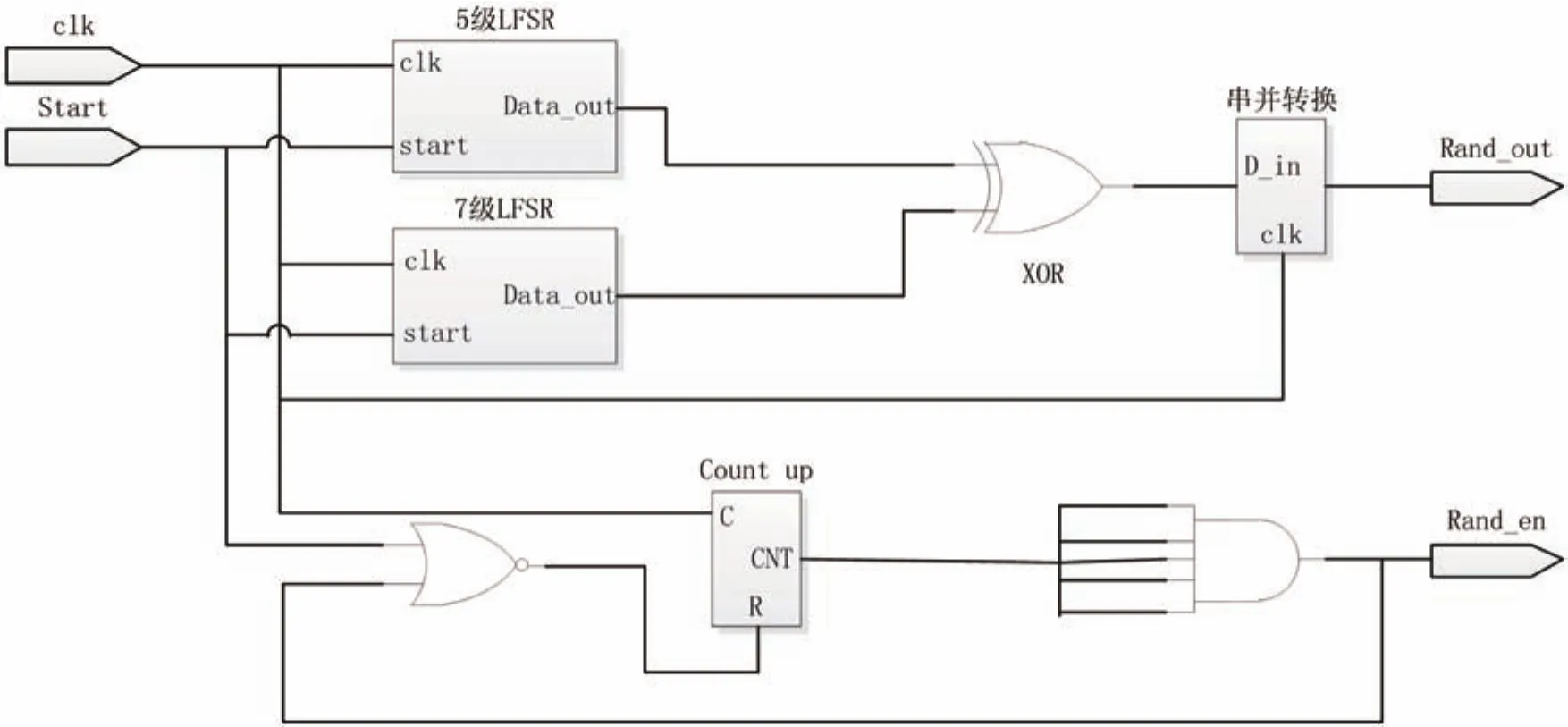

本方案中由FPGA内部电路产生良好随机性的随机数,设计简单、易于实现,不占用过多的硬件资源,是该安全保护方法安全性保障及设计可用性的重要一环。本方案设计的随机数由一个5级和一个7级的纯组合逻辑实现的LFSR抽头异或后由外部时钟采样生成,利用了组合电路的竞争冒险现象,并结合电子器件信号受外界环境影响和自身固有物理差异,对单FPGA芯片而言,每次上电时,因FPGA芯片所处环境的温度、气压等因素都会有所波动,导致门电路的延时特性在每次上电时都有些微差异,而单LFSR模块为完全由门电路组成的组合电路,其抽头输出数据与门电路的时延特性密切相关,因此在确定的时钟域上具有不可预测性,随着反馈级数的增加,这种不可预测性更加明显,当由固定时钟对生成的数据采样时,因被采样数据与该时钟对应的频率和相位均具有不确定性,因此产生了一个难以预测的序列,当两种不同级数LFSR产生的随机序列通过异或门电路使用后将放大这种不确定性,确保了每次上电生成的随机数具有不重复的特性,而对不同型号FPGA或同一型号内的不同个体而言,因工艺水平和制作工艺本身的误差,导致不同FPGA芯片内部电路物理特性不一致,确保了FPGA个体间生成的随机序列具有不重复特性。随机序列生成模块电路设计如图3、图4所示。

图3 组合逻辑实现5级LFSR模块

图4 随机序列生成模块

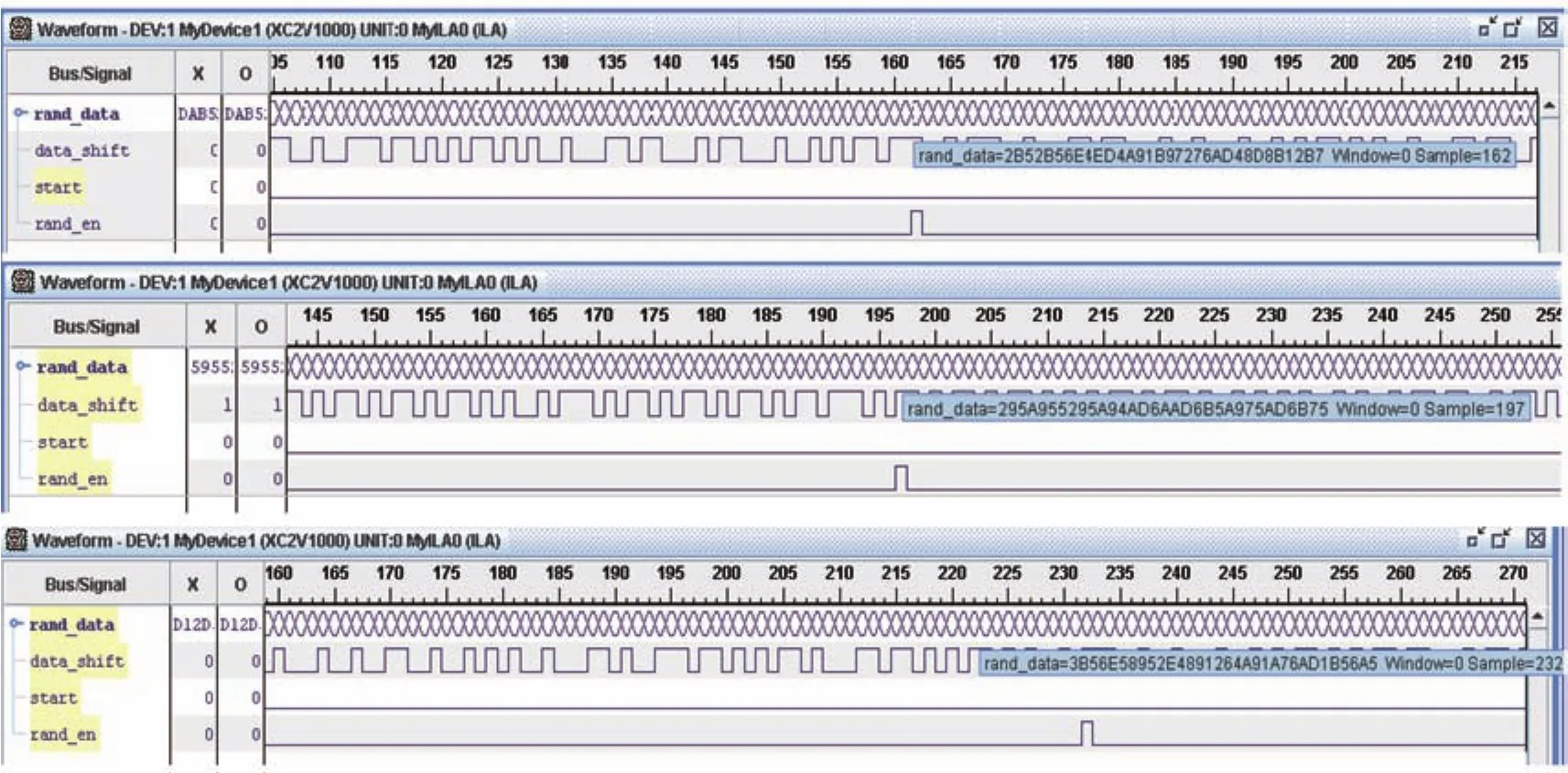

本设计在Xilinx公司xc2v1000器件环境下,利用其辅助ChipScope工具多次抓取的随机数生成实测结果,如图5所示,生成的随机数符合一次一变不重复的特性。

图5 随机序列采集结果

4 安全性分析

(1)防仿冒攻击。FPGA对外置保护电路实行单向身份合法性认证,通过双方共享的IP core参数作为保护密钥,用于认证数据生成,第三方在不能获取密钥数据的情况下,依据杂凑算法HMAC方式的密码保护特性,其无法通过伪造认证数据方式通过FPGA的合法性认证判断。

(2)抗重放攻击。FPGA每次认证开始时根据应用环境特点由内部电路产生随机数,第三方无法控制FPGA生成随机数的随机特性或掌握其生成规律,因而认证数据具有一次一变特性,任何对线路上截取的过往认证数据的重放都与FPGA当前产生的随机数据不一致,FPGA对非当前使用随机数生成的认证数据均判定为非法数据,导致认证失败。同时外置保护电路也以同样机制产生新随机数参与认证计算,并对FPGA产生的随机数进行重复性检测,辅助增强了设计的抗攻击能力。

(3)防穷举攻击。认证过程中由FPGA内部电路生成的随机数长度以4字节为例,其变化量达到232=4294967296,多种可能的变化使得第三方无法通过穷举截取线路数据的方式来伪造认证过程,同时通过适当调整随机数长度可达到更高的保护效能。

(4)防篡改攻击。消息认证码基于密码算法生成,其保护范围为FPGA和外置保护电路各自产生的随机数据,对线路传输的任何数据的改动都将导致认证过程失败。

(5)可用性。本方案设计的认证过程简单、实用、高效,通过二次握手即可完成FPGA对外置保护电路的合法性认证;双方交互的数据量小,在满足安全性需求的条件下,随机序列长度取4字节,消息认证码取8字节,则一次认证过程的通信开销只有16字节;代码实现简单,综合考虑破译难度和经济成本间的平衡,保护方案只使用易于硬件实现的LFSR以及实现复杂度较低的杂凑算法,在满足第三方对认证过程的破译成本与IP core的开发成本相当的前提下,可使用复杂度更低的杂凑算法以降低对硬件资源的开销,本设计使用简易、低成本的电路和芯片即可完成外置保护电路的功能。

5 结 语

本文分析了基于SRAM工艺FPGA设计中包含的知识产权存在被克隆风险产生的原因及可能造成的严重损失。通过设计外置安全保护电路方式,利用FPGA器件固有的物理差异及环境敏感特性产生一次一变的随机数据,结合杂凑算法HMAC方式的可认证性,设计了对该类型FPGA的IP core通过一次一密认证成功后才能正常工作的防克隆保护方法。设计仅需额外增加简易且低成本的外围电路资源,易于工程实现,安全性较高,具有良好的实用价值。