一种小型化双层拓扑的低通LC滤波器*

陈 雄,张 鹏,王 玲

(天津大学 微电子学院,天津 300072)

0 引言

随着现代无线通信系统的高速发展,其微波电路结构越来越复杂,性能要求越来越高,体积越来越小,重量越来越轻。在现代无线通信系统中,高性能的滤波器器件依然是不可或缺的一部分,通信系统对于多个频带的兼容性与频率的选择性要求越来越苛刻,此时需要滤波器具备更高的阻带抑制与宽阻带性能[1]。随着5G时代的到来,微波以及毫米波滤波器正朝着小型化、高频带宽化、集成化方面快速发展。同时,在空间航天技术中,航天器和基站中对滤波器的要求极为苛刻,其性能要求较高,体积要求较小,因此高集成度和高性能滤波器成为发展的方向[2]。

集总元件和分布元件是微波以及毫米波滤波器的主要设计形式,集总参数元件尺寸小、价格低、可实现宽带,目前仍然具有极大的优点[3]。本文主要研究了一种结构新颖、性能独特的LC低通滤波器,并提出了详细的设计方法[4]。相较于传统的LC低通滤波器[5],本文采取了双层拓扑结构,在尽量小的空间内布局尽量多的LC元器件,使得其整体结构相较于传统的单层结构体积较小,并且其性能优越,适用于空间航天等对于滤波器体积与性能有着苛刻要求的环境中[6]。本文设计的滤波器仿真结果很好,并把其中滤波器进行了加工实测,结果与仿真结果吻合度较好,有广泛的工程应用前景。

1 电路模型与理论基础

1.1 LC滤波电路

LC滤波器是一个选频电路,电感L存储磁能,电容C存储电能,当存储的电场能量等于存储的磁场能量时电路产生谐振,此时可以使通带范围内的信号几乎无衰减地通过,抑制带外信号通过[7]。LC滤波器为微波滤波器如螺旋滤波器、微带滤波器及腔体滤波器等提供理论基础[8]。通常滤波器有以下基本指标:

截止频率:是指给滤波器输入信号时,输出信号的幅度下降到其最大值0.707倍对应的频率,也即是-3 dB点处。低通和高通滤波器分别有一个截止频率,对于带通和带阻滤波器,则是上截止频率和下截止频率。

中心频率(f0):上截止频率f2和下截止频率f1求得均值时所对应的频率点为:

f0=(f1+f2)/2

(1)

带宽(BW):是指频段宽度,即:

BW=f2-f1

(2)

相对带宽(FBW):用来表示滤波器的带宽:

FBW=(f2-f1)/f0

(3)

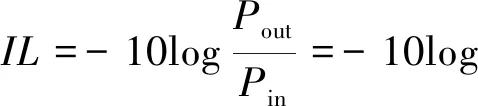

插入损耗(IL):信号经滤波器传输时,功率的损耗为:

(4)

Pout是输出功率,Pin是输入功率,|Γin|是输入端的反射系数, 插入损耗可用S21表示。

回波损耗(RL):是指滤波器和其他器件连接时由于内部阻抗不匹配,用以描述信号反射强弱的参数:

(5)

Pr是反射功率,回波损耗也可以用S11表示。

带内波纹(LAr):是指通带内插入损耗随频率的变化量。

1.2 滤波器响应

在插入损耗法中,滤波器响应是由插入损耗定义的,即由式(4)决定,Γin是输入端的反射系数:

(6)

其中ω为变量频率,ω1为滤波器的截止频率。

当滤波器的阶数已经确定,如果指标中最关键的是带内插损,那么最平坦响应滤波器就是最优选,对于低通滤波器[9]:

LAr=10log

(7)

其中n对应滤波器的阶数。

对于本文设计的LC低通滤波器,其设计面向对于体积、插入损耗等参数有着较高要求的环境[10]。本文通过调节拓扑结构使得体积缩小,此时关键的指标就是带内插损,因此巴特沃斯型响应完全符合条件,所以选择此种响应方法。选择归一化低通滤波器原型电路[11],根据归一化滤波器设计表,可得归一化低通滤波器原型电路,假定其源阻抗为1 Ω,截止频率为ω1=1,源电阻g0=1,此时:

(8)

gk为电感或者电容的值,gn+1为负载电阻,此时各电容电感的值为:

g1=0.347 3,g2=1.000 0,

g3=1.532 1,g4=1.879 4……

LC低通滤波器电路结构如图1所示,其基于LC滤波电路产生谐振,可以使通带范围内的信号几乎无衰减地通过,符合其设计要求。各个谐振节的电容电感值如图1所示。

图1 低通滤波器电路原理图

2 电路仿真与试验测试

本文旨在实现一种宽阻带、双层结构的LC低通滤波器。提出的滤波器电路结构如图1所示,该电路是由8个串联电感和8个并联电容组成的LC 低通滤波器。

2.1 ADS模型仿真

基于图1所提出的低通滤波器电路原理图,借助电路仿真软件ADS,进行滤波器的建模与仿真。根据ADS仿真软件选择巴特沃兹类型后,建立仿真原理图,如图1所示,对滤波器进行仿真分析[12],扫描频率设置为100 MHz~4 000 MHz,频率间隔1 MHz。

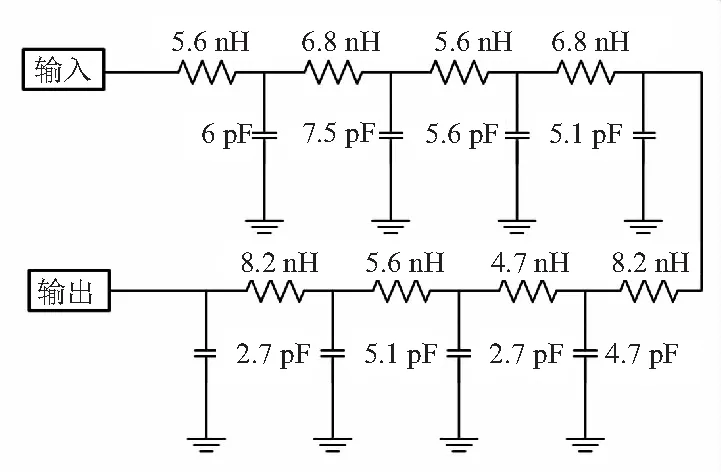

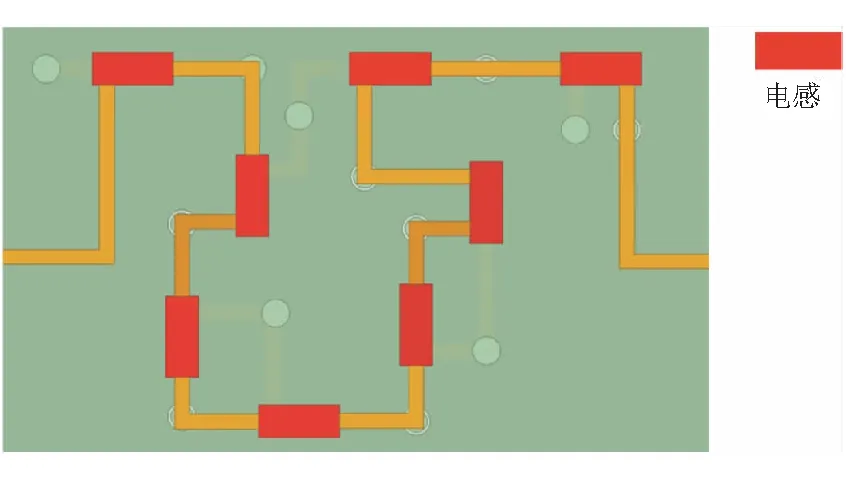

2.2 HFSS模型建立与仿真

相较于传统的LC低通滤波器,本文采取了双层拓扑结构[13],在ADS中进行的是二维平面上的仿真,因此接下来在HFSS中进行三维模型的设立,为尽可能的缩小空间,将之前确定的电子元件进行折叠式排布[14],使得其占据空间较小,其平面结构如图2所示。

电感的分布如图2所示,其中8个电感分布在上层表面上,以折叠式排列,这样在20 mm长度的PCB板上,可以容纳近两倍数量的电子元器件,使得滤波器实现小型化、集成化[15]。

根据所采用的电感和电容资料,可以计算出电感和电容的寄生参数。同时考虑实际工程实现中的PCB引线和过孔对应的等效电感,需要进一步优化仿真,电磁仿真软件HFSS具有精确自适应的场解器,能计算任意形状三维无源结构的S参数和全波电磁场,优化部件的性能指标,并进行容差分析[16]。

(a) 顶层电感示意图

(b) 底层电容示意图

电容分布在下层表面上,其排列结构与电感相同,电感与电容之间的连接,通过上下层表面穿孔,过孔的导线进行串联。在HFSS中进行三维模型的建模,通过此种排列方式,使得其整体结构缩小。并且在该低通滤波器两端,添加具备SMA接口的焊盘,引脚间距4.2 mm,引脚长度4 mm。进行滤波器的仿真分析,扫描频率为100 MHz~4 000 MHz,频率间隔1 MHz,其仿真结果与理论计算值相符合。

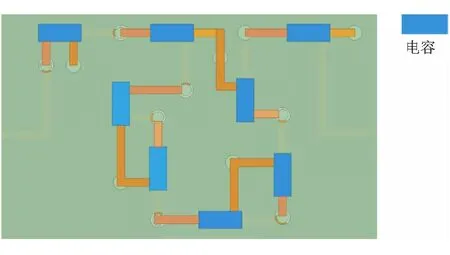

3 滤波器实物测试

根据上节中优化得到的滤波器结构,进行下一步工作,完成LC低通滤波器的制作加工。对于成品PCB电路,采用矢量网络分析仪对滤波器的具体参数进行测试。

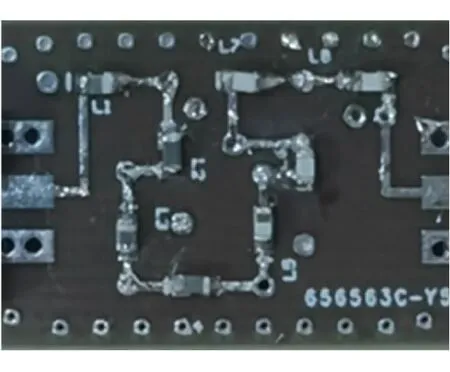

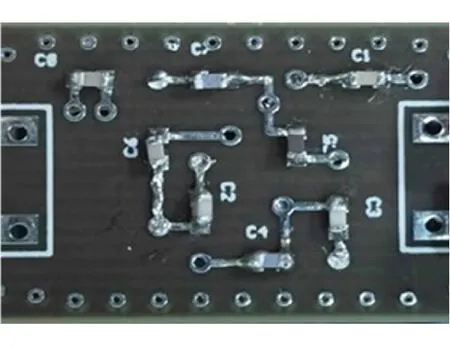

根据仿真软件设计所加工的滤波器如图3所示,此LC滤波器采取4层PCB结构,电感和电容元器件分别焊接在上表面与下表面,接下来对滤波器进行测试,其具体参数如图4所示。

从网络分析仪的测试结果图可以看出,其滤波器实物的工作指标为:在0 MHz~800 MHz通带内,滤波器插入损耗小于1.5 dB。频率大于1 000 MHz时,阻带的损耗大于40 dB。

(a) 顶层电感实物图

(b) 底层电容实物图

同时将网络分析仪的测试结果与在电磁仿真软件得出的仿真结果相对比,可以看出,在HFSS得到的仿真结果为:在0 MHz~800 MHz通带内,滤波器的插入损耗小于1.5 dB。当频率大于1 000 MHz,带外大于50 dB。实物的测试结果与仿真结果相吻合,符合其设计要求。

图4 滤波器仿真与测试结果对照图

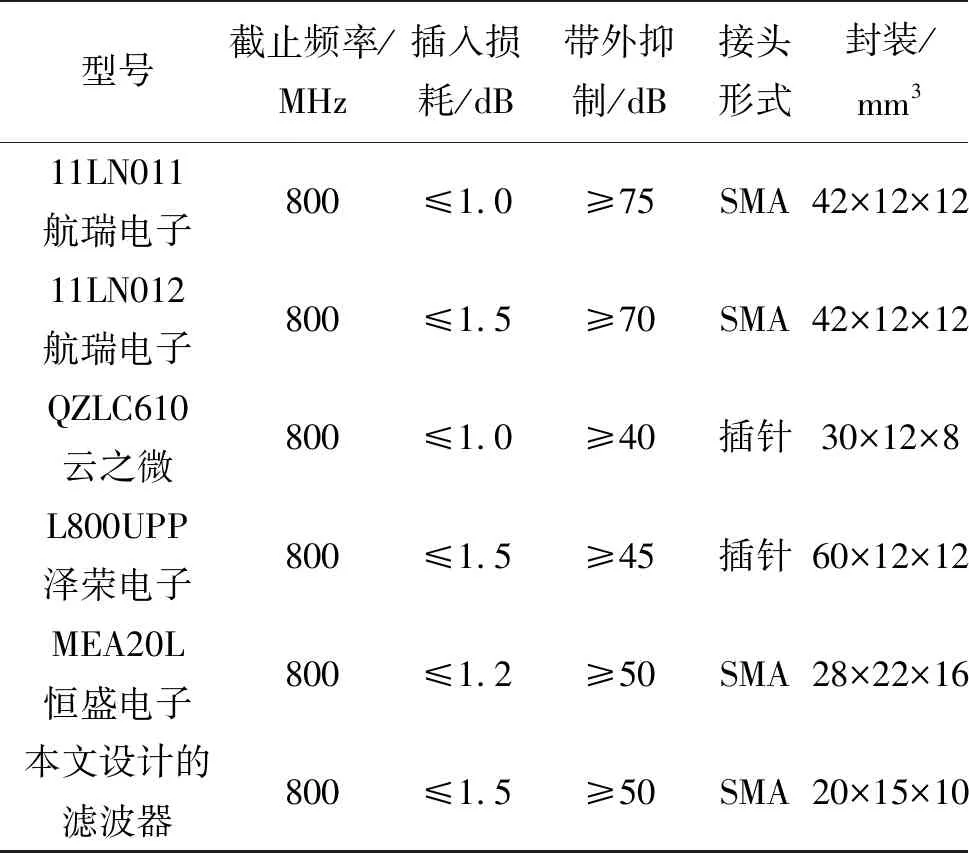

通过对比所加工的滤波器,与网上的现有设计的厂家的成品相对比,如表1所列:

表1 与现有相关产品的性能对比

可以看出所加工的滤波器与市面上的部分滤波器参数大致类似,然而其封装体积为20 mm×15 mm×10 mm,其体积远小于市面上的滤波器成品,在较小的体积要求下实现了优良的性能。所以具有低成本、高集成度、高性能的优点。

4 结论

本文从理论上研究了滤波器的原理与设计方法。在此基础上,提出了一种双层拓扑结构的低通滤波器模型,通过电感与电容的连接导线折叠,使得在尽量小的空间内布局尽量多的LC元器件,使得其整体结构相较于传统的单层结构滤波器体积缩小一半左右。通过对试验结果的对比分析,测量结果与理论计算、仿真值吻合较好,验证了模型的正确性。本文设计的低通滤波器具有小型化、高频带宽化、集成化的优点,适用于空间航天等对体积、插入损耗等有着较高要求的环境,同时其成本较低,易于加工,有广泛的工程应用前景。