基于递归学习的静态逻辑电路功耗优化方法

扎西群宗,次 央

(1.西藏自治区广电局033台,西藏 拉萨 850000;2.西藏自治区广电局071台,西藏 拉萨 850000)

0 引 言

随着技术不断发展与进步,集成电路芯片的集成度越高,电路中晶体管的尺寸越小,电路的工作速度就越快,同时对集成电路的功耗要求也就越高,集成电路在功耗设计过程中需要注意的问题也越来越多[1,2]。在同样功能需求的情况下,采用互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)的集成电路具有功耗较低的优势,尤其是静态功耗[3,4]。功耗的非稳态直接导致电路的温度明显上升,电路的可靠性大大降低,因此对静态逻辑电路功耗进行优化具有十分重要的现实意义和应用价值[5]。本文提出基于递归学习的静态逻辑电路功耗优化方法研究,在构建静态逻辑电路功耗模型的基础上,利用递归学习的方式对静态逻辑电路功耗收敛进行优化。

1 静态逻辑电路功耗收敛优化方法

1.1 构建静态逻辑电路功耗模型

在对静态逻辑电路功耗收敛进行优化前,结合电路功耗本身的属性特征构建功耗模型[6]。一般情况下,静态逻辑电路功耗可分为静态功耗和动态功耗两个部分。其中,静态功耗的计算公式为

式中:Wj为静态逻辑电路的静态功耗;Iz为通过栅极氧化层的隧穿电流值;I1为反偏二极管的漏电流值;Ib为电路竞争电流值;It为MOS晶体管的亚阈导通电流值;U为经过静态逻辑电路的电压值大小[7,8]。

动态功耗的计算公式为

式中:Wd为静态逻辑电路的动态功耗;Id为P型金属氧化物半导体(P-channel Metal Oxide Semiconductor,PMOS)和N型金属氧化物半导体(N-channel Metal Oxide Semiconductor,NMOS)同时导通时产生的短路电流值;Wf为负载电容充放电引起的开关功耗。

漏电流是决定静态功耗大小的关键因素,经过电路的电流信号跳变频率不会对其产生影响,电路中的信号翻转情况是决定动态功耗大小的主要因素[9]。栅极氧化层厚度的改变将直接导致静态逻辑电路的总漏电流值增加,对应的静态功耗也将随之增加。在此基础上,造成静态逻辑电路功耗参量波动的其他因素包括电源电压和电流的大小。

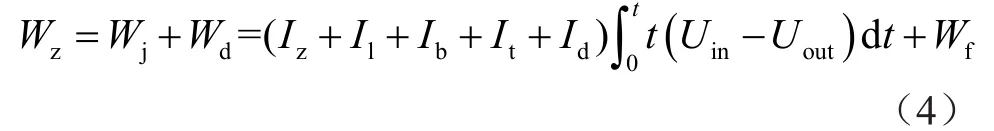

在特定的应用范围内,瞬时功耗与电源电压和电流成正比关系,以此为基础构建以电压为核心的功耗表示方式,具体为

式中:Uin为静态逻辑电路的输入电压值;Uout为静态逻辑电路的输出电压值;t为运行时间。

在此基础上,本文构建的静态逻辑电路功耗模型可以表示为

式中:Wz为静态逻辑电路的总功耗。

1.2 基于递归学习的功耗收敛优化

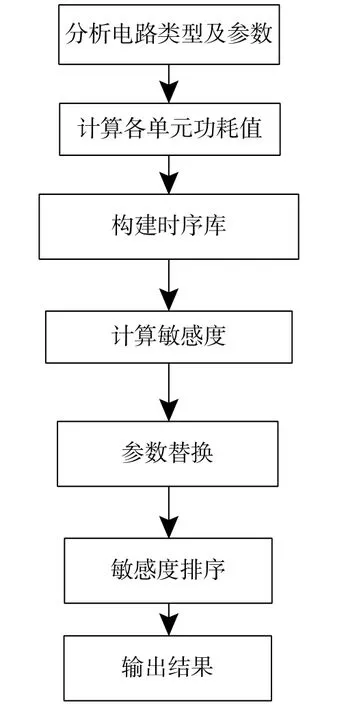

在上述基础上,采用递归学习的方式对静态逻辑电路功耗收敛效果进行优化。在电路正常运行的条件下,静态逻辑电路电压的收敛速度是影响其功耗收敛效果的重要因素。基于递归学习的静态逻辑电路功耗收敛优化流程如图1所示。

图1 基于递归学习的静态逻辑电路功耗收敛优化流程

采用递归学习对静态逻辑电路功耗收敛进行优化前,需要先进行参数准备。考虑到集成程度是影响栅极氧化层厚度的主要因素,在数据准备阶段要对电路单元的类型与尺寸进行分析。综合考虑当前延时情况,设置不同的电压值,分析不同电压环境下静态逻辑电路单元延时的标准差和均值。根据获取的延时数据,计算各个单元对应的功耗值,计算公式为

式中:Wzi为静态逻辑电路中i单元的功耗;为静态逻辑电路中i单元的延时标准差;εi为静态逻辑电路中i单元的延时均值。

构建以静态逻辑电路各个单元功耗为基础的时序库,为后续的优化调节过程提供数据参考。将电路的延时作为递归学习的敏感度函数,计算电路中所有单元在时序库内的敏感度函数值,当对应单元的参数不造成电路功耗的波动时,将其作为可替换的单元进行敏感度量化设置,并保存到时序库队列中。在此基础上,对队列中单元敏感度按照取绝对值后降序的方式进行排列,单位时间内功耗下降幅度越大,则表明此时延时和延时偏差的波动范围越小,对应静态逻辑电路功耗收敛性越高。逐个替换队列中的敏感度函数值,当对应的功耗延时小于该单元的可调节余量时则保留该替换操作。完成对电路单位运行周期内各个单元全局时序的计算后,确保电路不存在时序违规,此时输出结果即为功耗收敛优化后的参数。

2 测试分析

为了验证本文提出的基于递归学习算法的电路功耗优化方法的有效性,将其与文献[4]所提方法和文献[5]所提方法进行功率控制对比测试。在测试阶段,测试电路共计27个,使用C语言将设计的优化方法转化为可执行的控制措施。本文使用的操作系统为Windows 2020,编译工具为VC10.0,对应的硬件环境参数为Intel Pentium(R)Dual-Core,中央处理器(Central Processing Unit,CPU)大小为256 GB,随机存取存储器(Random Access Memory,RAM)大小为6.0 GB。

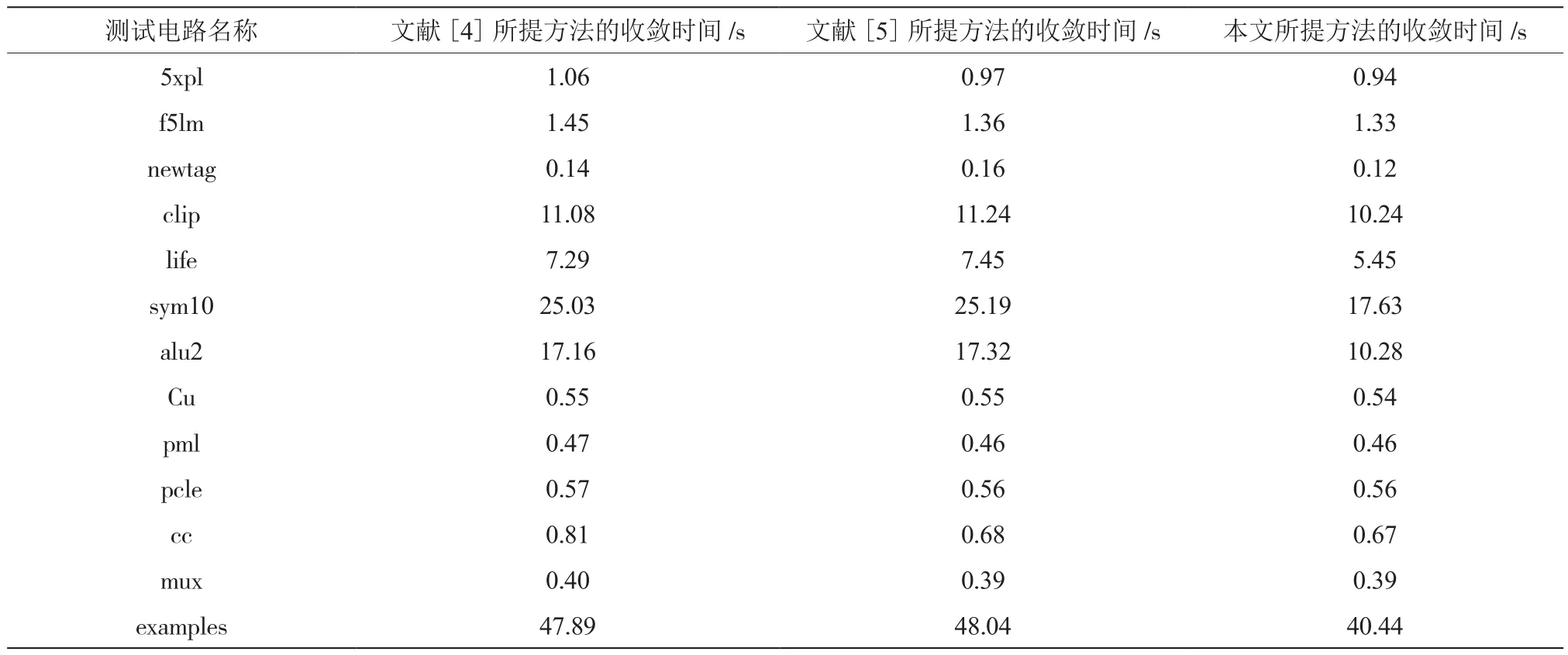

为了确保功耗测试结果的可靠性,采用随机生成的方式产生输入数、输出数和乘积项数。设置初始惯性权重系数为1.0,终止惯性权重系数为0.20,按照线性递减的计算方式在学习因子为1.2的条件下进行200次迭代。3种方法对FPRM静态逻辑电路的功耗收敛时间测试结果如表1所示,

表1 FPRM静态逻辑电路功耗收敛时间

在3种方法对静态逻辑电路功耗的控制过程中,对应的收敛时间都随着测试电路的类型出现了明显的波动。对于5xpl、newtag、Cu、pml、pcle、cc以及mux等规模较小的电路,3种方法的收敛时间相近;对于sym10等规模较大的电路,本文所提方法的收敛时间均较短,能够实现FPRM逻辑电路功耗的快速收敛。

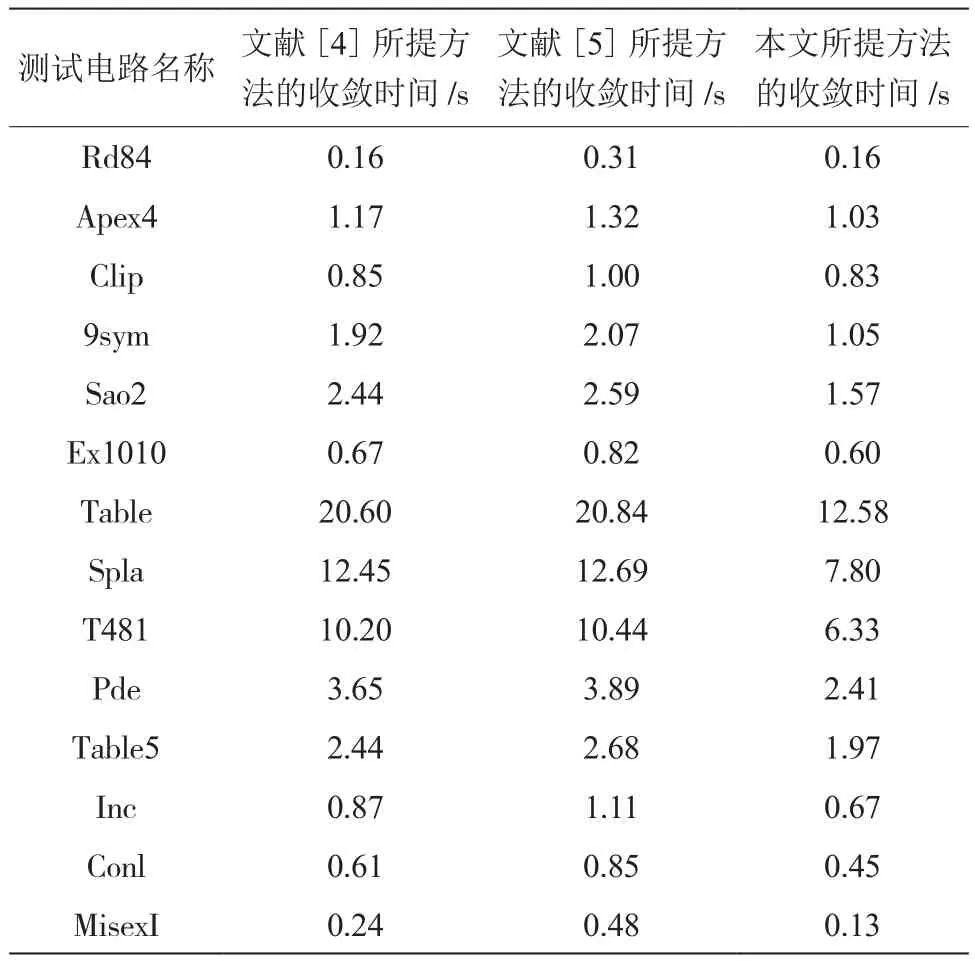

3种方法对混合极性XNOR/OR电路的功耗收敛时间测试结果如表2所示。

表2 混合极性XNOR/OR电路功耗收敛时间

对于Rd84、Conl、MisexI等规模较小的电路,3种方法的收敛时间差异并不明显;对于Table、Spla等规模较大的电路,本文所提方法的收敛时间较短,可以实现混合极性XNOR/OR电路功耗的快速收敛。

3 结 论

综上所述,设计基于递归学习的静态逻辑电路功耗优化方法,从电路功耗的收敛性角度出发,利用递归学习的优势大大减少静态逻辑电路功耗维持稳定的时间开销。通过本文的研究,以期为实际静态逻辑电路的运行提供帮助,促进相关行业的长久发展。