一种高性能八通道CAN 集线器方法

阳乐凯

(广州致远电子股份有限公司,广东 广州 510641)

我们知道,强大的网络可以为系统的稳定运行提供可靠的保障,通信网络可以认为是控制系统的中枢神经系统。CAN 总线控制系统的网络搭建应在早期给予足够的重视,做到网络总体规划,合理设计及安装,总的来说,网络搭建需要做好以下几个步骤的工作才能保障总线长期稳定的运行。

本产品实现8 通道CAN 集线器功能,实现8 个通道CAN 帧接收、缓存、帧映射、帧转发等功能。通过UART(USB 或RS232)使用类似ModBus 协议与上位机通信,实现CAN 集线器的功能配置。CAN 集线器能实现多个CAN 网络的透明连接,可以在总线级别实现复杂结构的多点连接;CAN 集线器使得主干网络没有支线长度限制,网络中任意两个节点可以到达协议距离,该设备具有8 个通信端口,每个端口都有独立的CAN 收发器,能倍增节点数目,因此,在提供自由的布线方式的同时,也解除了系统总线上CAN 收发器最大节点数驱动限制。每个端口还具备检测总线活跃及总线故障指示灯,方便观察CAN 总线网络工作状态。CAN 集线器可用于波特率高达1Mbps 的CAN 网络,所有通道均可在不同的波特率下工作,其符合CAN 规范2.0A(11 位CAN 标识符)和2.0B(29 位CAN 标识符),支持透明的,协议独立的CAN 消息传输,使其适用于多种应用。[1]

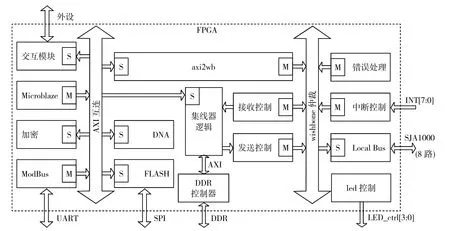

1 总体框图

整个系统采用FPGA+SJF1000 方式,FPGA 负责将SJA1000 的CAN 数据波特率、路由表、滤波表、帧映射的规则进行各路之间的转发,通过FPGA 的串口实现产品的配置和监控。本设计主要实现8 通道CAN 的集线器功能,实现8 通道之间的转发和帧映射功能,实现框图见图1。主要由wishbone 仲裁部分和AXI 互连部分各模块组成。

图1 内部设计框图

wishbone 部分各模块实现8 通道sja1000 的管理。LocalBus 主要实现与8 通道sja1000 的通信;中断控制实现对sja1000 中断的接收和管理;错误处理模块实现各通道的错误自动处理;接收控制和发送控制配合集线器逻辑实现本设计的核心功能——帧缓存、帧映射和路由等功能;axi2wb 模块为通过AXI 配置各通道sja1000 提供接口,实现Microblaze 对各通道sja1000 的配置。[2]

AXI 互连部分主要实现上位机对集线器功能的控制。其中ModBus 模块主要实现通过UART 与上位机通信,UART 可以通过USB 或RS232 两种UART,两种UART 会自动切换,当有USB 插入时则使用USB 转UART 的ft232 的串口,没有USB 插入时则自动切换到RS232 的串口来通信;加密和DNA 模块主要实现对固件的加密;flash 模块主要实现信息的存储,包括固件、配置信息和加密信息等;交互模块主要实现对外设的控制和与上位机的交互操作;axi2wb 模块实现对各通道sja1000 的配置接口;Microblaze 用于实现以上功能的控制和与上位机的交互,上电后实现对固件的加密验证,实现从flash 读取上位机的配置并将其配置到指定的sja1000 中或集线器逻辑中,并通过交互模块对其它各外设的控制和与上位机的交互。

集线器逻辑实现帧缓存、帧映射和转发等功能。集线器逻辑从接收控制模块接收帧后通过AXI 接口和DDR 控制器将帧缓存到外部DDR3 中;当能发送时从DDR 中读取出来,并根据配置来映射帧并转发到设置的通道中,通过发送控制模块发送到sja1000。

2 设计实现

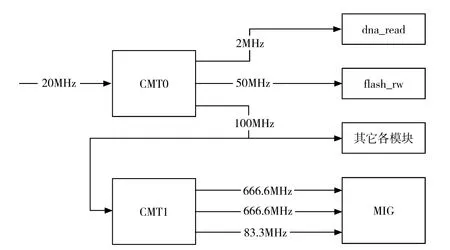

2.1 各模块时钟关系

本设计中各模块时钟关系如图2,外部输入时钟20MHz,通过CMT0 生成100MHz 主时钟到各模块;同时也输入到CMT1 中用于生成MIG(DDR 控制)的各时钟(6666.6MHz 差分时钟和83.3MHz 时钟);另外,由于flash 最大支持80MHz,这里使用CMT0 生成的50MHz 时钟;DNA 读取模块中DNA 原语(Spartan-6)中最大只支持2MHz,所以DNA 模块使用CMT0 生成的2MHz 时钟读取器件DNA。

图2 各模块时钟关系

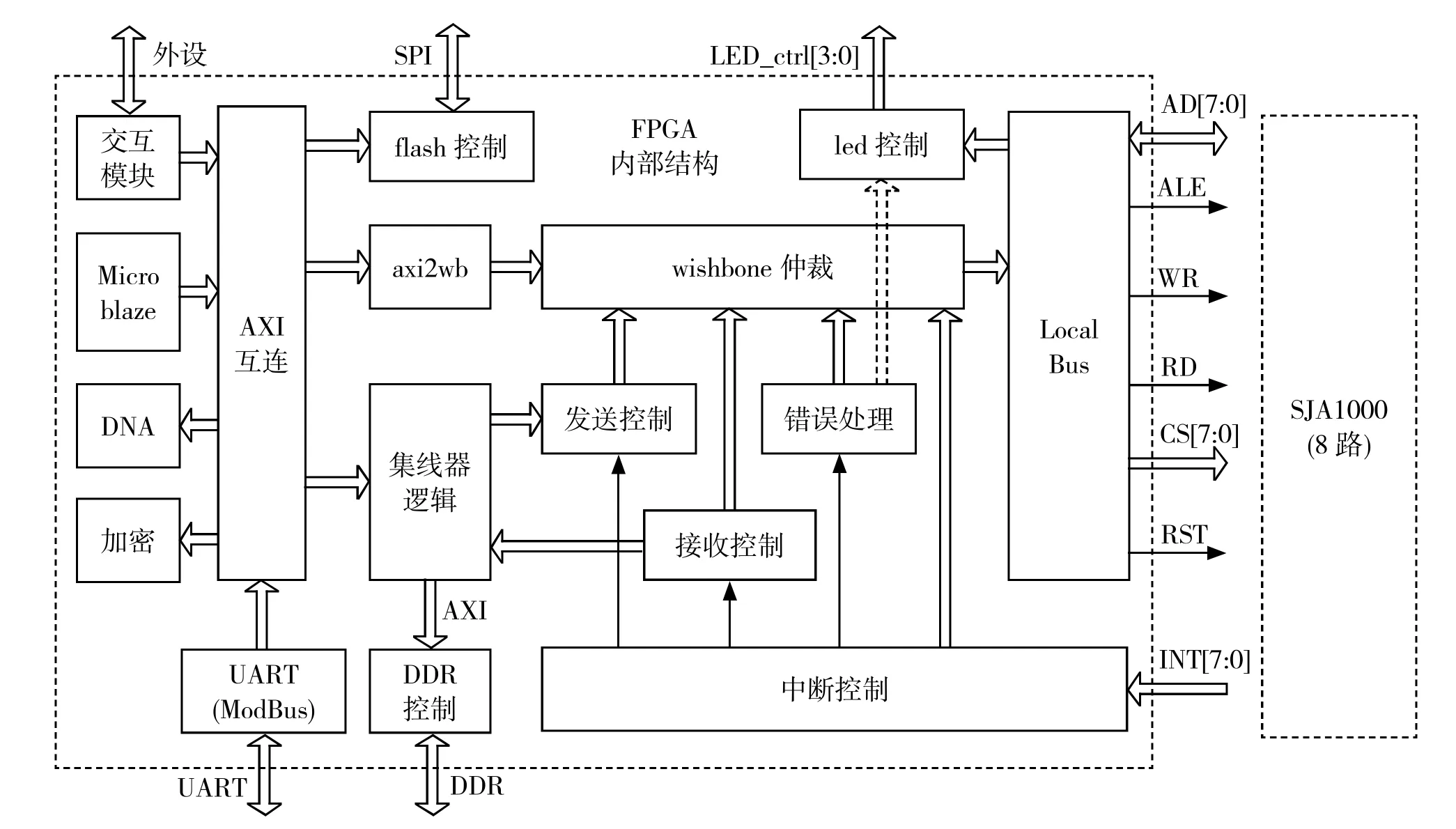

2.2 内部详细结构

CANHub-AS8 内部详细结构如图3,sja1000 控制模块主要有localbus 模块、中断控制模块、错误处理模块、接收控制模块和发送控制模块;与上位机通信主要有ModBus 模块、交互模块、flash 控制模块和Microblaze;加密部分主要有加密模块和DNA 模块,加密信息存入flash 中;axi2wb 模块主要实现sja1000 的配置;集线器逻辑主要实现帧映射、路由转发和帧缓存等。

图3 集线器内部详细结构

sja1000 配置和与上位机通信的各操作主要有Micro blaze 实现,Microblaze 软件控制流程如图3,主要实现上电复位后对加密的验证;从flash 读取设备序列号存入寄存器操作;初始化各通道sja1000;外部按钮的处理和USB 插入和拔出的处理等;对上位机发送命令的处理等。[3-7]

3 结语

对于现有技术的控制方式,由于ARM 处理速度受限制,当需要8 路CAN 通信同时使用的时候,经常出现丢帧、帧重复等错误,本设计采用FPGA 作为主控,由于FPGA 接收到中断只要几个时钟周期(几十ns)就可以开始处理,而ARM 收到中断需要指令跳转,而且还不止一次跳转,各种计算也是串行的,而FPGA 中各种计算都是并行的,比如ARM 接收到一帧的1Byte就要存储到内存,这个过程要先接收1Byte 再写入内存,不能同时开始,而且写内存的时间也不短;而FPGA中在收到1Byte 后存入寄存器(很快,一个时钟周期=10ns),在写入缓存(其实写入缓存也很快)的同时就可以继续接收下1Byte 了,大大提升了处理速度。