基于FPGA的多通道雷达数据回放系统设计

赵英潇,苏 阳

(1.军事科学院 军事科学信息研究中心,北京 100036; 2.中国电子科技集团公司 第十四研究所,江苏 南京 210012)

为应对雷达应用面临的目标多样化、环境复杂化和任务多元化等问题[1-3],需要不断改进和验证雷达实时信号处理系统及其处理算法。雷达实时信号处理系统大多是基于DSP(Digital Signal Processor)[4]、GPU(Graphics Processing Unit)[5]、FPGA(Field Programmable Gate Array)[6]、MIC(Many Integrated Core)[7]等专用处理芯片设计的。采用MATLAB等通用数据处理软件[8-10],只能对实时处理算法性能进行间接和粗略验证。采用目标模拟器尽管能够对雷达实时处理系统及算法进行直接功能验证[11-12],但难以模拟复杂的目标特性和跟踪环境。通过实际目标跟踪任务可对实时信号处理系统及算法进行完备的性能测试,但由于各次跟踪任务的目标特性和跟踪环境存在差异,故无法有效地对多种实时处理算法的性能进行比较。

雷达数据回放系统可将雷达回波数据按照雷达工作的时序及数据率发送至实时数字信号处理子系统,使任务执行时的目标特性、目标环境和雷达工作状态得以完整复现。与上述3种方式相比,雷达数据回放系统既能保证目标、环境及雷达时序的真实性,又能保证任务场景的稳定、可控和可重复性,适用于雷达实时处理系统及算法验证。

文献[13~15]对雷达数据回放系统展开研究,但是这些研究大都针对单一数据类型、单数据通道或单一回放板卡,难以被应用于复杂雷达系统中。针对以上问题,本文设计并实现了一种宽窄带一体化、多通道雷达数据回放系统,解决了数据回放中的数据高速传输、精准时序控制、板间同步控制等问题。本文设计的雷达数据回放系统可被直接嵌入至原有雷达系统的硬件平台中,无需配置额外的板卡或线缆,具有良好的集成性和通用性。

1 系统硬件平台

本文依托某相控阵雷达系统进行数据回放系统的设计与实现。雷达系统接收端结构如图1所示。

当雷达工作时,回波信号经宽/窄带接收机变频、模数转换后,分别下传至数据存储处理系统的宽/窄带PCIe(Peripheral Component Interconnect Express)光纤板。PCIe光纤板一方面将多通道回波数据传输至磁盘阵列服务器,另一方面可将数据转发至实时数字信号处理系统。

本文中,将数据回放系统集成于图1的数据存储管理系统内。其主体控制逻辑嵌入至PCIe光纤板的FPGA,数据链路复用雷达回波接收及处理时的数据链路,无需额外增加板卡及线缆。当数据回放系统工作时,由磁盘阵列服务器读取雷达回波数据,通过PCIe接口下传至宽/窄带PCIe光纤板。PCIe光纤板模拟雷达工作时序将数据转发至实时数字信号处理系统。磁盘阵列服务器及PCIe光纤板实物如图2所示。

图1 雷达系统接收端结构Figure 1. Structure of the radar receiving terminal

(a) (b)

2 总体结构设计

2.1 数据回放设计实现思路

雷达回波数据以帧为单位进行存储及回放。单帧数据由帧头及多个脉冲数据块组成,其数据格式如图3所示。通过提取帧头中的帧起始标志、波门起始时间B、雷达周期Tr、驻留脉冲数N等信息,计算出对应的定时控制计数值,进而控制雷达回波数据回放,使数据回放的时序及数据率与雷达工作时相一致。

图3 单帧雷达回波数据组成结构Figure 3. Frame structure of the radar echo data

2.2 总体结构设计

根据章节2.1所述的设计实现思路,系统总体结构设计如图4所示。

图4 系统总体结构图Figure 4. Structure of the radar echo signal playback system

数据回放系统工作时,由上位机(服务器)软件读取磁盘阵列中的多通道雷达回波数据,并利用PCIe接口以DMA(Direct Memory Access)的方式传输至宽/窄带PCIe光纤板。宽/窄带PCIe光纤板分别提取数据中的雷控信息(雷达周期、波门位置等),并按照雷达工作时序将多通道数据并行发送至实时信号处理系统。

雷达工作状态信息提取及回放时序控制是在PCIe光纤板的FPGA中具体实现的。FPGA顶层模块结构设计如图5所示。

图5 FPGA顶层模块结构设计图Figure 5.Top module structure in the FPGA

PCIe模块用于实现FPGA与上位机之间的数据交互。FPGA以PCIe DMA读的方式接收上位机下传的雷达回波数据,并在FPGA挂载的DDR3中进行缓存。DDR3_Ctrl模块用于对DDR3进行读写控制,该模块屏蔽了DDR3复杂的读写控制逻辑,为用户提供了与FIFO(First Input First Output)类似的读写控制接口。

FH_Read模块用于从数据中提取帧头中的帧起始标志位、波门起始值、雷达周期、驻留脉冲数等信息并据此计算出相应的时序控制计数值。State_Machine模块可根据FH_Read模块输出的时序控制计数值,操纵DDR3_Ctrl模块读取雷达回波数据。

时序控制后的雷达回波数据经Delay模块延时,再经Transcode模块位宽模块,最终分发至各路数据通道的GTX(Gigabit Transceiver)模块。GTX模块负责与实时信号处理系统进行高速串行通信。

3 PCIe DMA实现流程

回放系统通过PCIe DMA方式,将磁盘阵列服务器中的雷达回波数据高速下传至PCIe光纤板。Xilinx公司提供了多种系列FPGA的PCIe IP核[16]及PCIe DMA通用程序模块[17]。上述产品通过上位机完成对FPGA PCIe DMA相关寄存器的读写控制,实现了PCIe DMA数据传输。在此基础上,本文结合雷达数据回放的具体应用情形,增加部分寄存器状态位和控制字,PCIe DMA具体控制及响应流程如图6所示。由于雷达回波数据既可能包含全部数据通道,也可能仅包含部分数据通道,为简化FPGA端的控制逻辑,需要由上位机(磁盘阵列服务器)进行多通道数据的预处理,对齐并补全多通道数据。随后,根据数据类型及FPGA缓存容量,上位机对单次DMA传输的数据量大小进行设置,并清空FPGA数据缓存。在每次DMA操作之前,上位机需要读取FPGA内部的DDR3自定义空信号,确保缓存剩余空间足够用于下一轮DMA传输。

图6 PCIe DMA控制及响应流程图Figure 6. PCIe DMAcontrol and response procedure in the playback system

4 回放时序控制

雷达回波数据下传到PCIe光纤板之后,按照雷达工作时序经光纤传输至实时信号处理系统。由章节2.2可知,数据传输精准时序控制主要由State Machine模块实现,该模块由主从嵌套状态机构成。

图7为主状态机的状态转移图,其中帧头回放(FSM1)、脉冲数据n回放(FSM2)、脉冲数据N回放(FSM3)这3个主状态又分别嵌套从状态机1~3,且每个从状态机都设有单独的时序控制计数器。如图7所示,当同时检测到PCIe模块输出的DMA起始信号DMA_start_en和DDR3模块输出的自定义空信号DDR3_prog_empty拉高时,主状态机由初始状态(FSM0)进入FSM1状态,回放帧头数据。当检测到从状态机1返回的结束标识信号FSM1_finish时,主状态机进入FSM2状态,回放前N-1个脉冲数据。当检测到从状态机2返回的结束标识信号FSM2_finish时,主状态机进入FSM3,最后回放第N个脉冲数据。当检测到从状态机3返回的结束标识信号其FSM3_finish时,主状态机进入FSM0状态,开启下一帧数据回放。

图7 主状态机状态转移图Figure 7. State transition of the master state machine

帧头回放状态(FSM1)对应从状态机1,其状态转移图如图8所示。当主状态机进入FSM1状态时,会向从状态机发送启动信号start_enable。检测到该信号后,从状态机1由初始状态进入帧头回放开始状态。此时从状态机1将缓存数据读使能信号ddr3_rd_en拉高,控制DDR3_Ctrl模块读取DDR3缓存数据,并传输至GTX模块,同时时序控制计数器开始计数。当检测到帧头结束标志时,从状态机1进入帧头回放结束状态,将ddr3_rd_en信号拉低,结束从DDR3内读取数据。当时序控制计数器计数到CB,即波门起始时间B对应的计数值时,从状态机1进入初始状态并向主状态机返回结束标志FSM1_finish。

图8 从状态机1状态转移图Figure 8. State transition of slave state machine FSM1

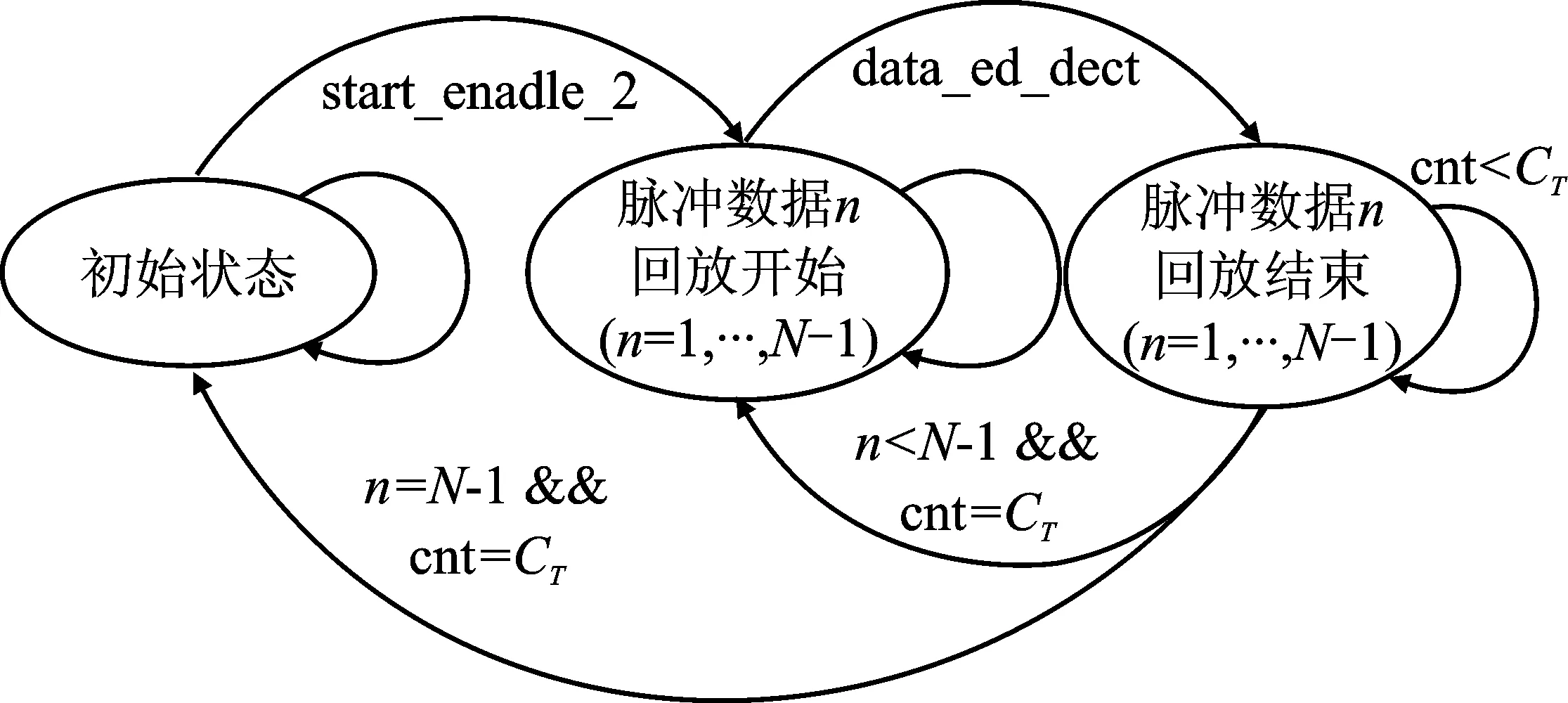

脉冲数据n回放状态(FSM2)对应从状态机2,其状态转移图如图9所示。该状态机与从状态机1类似,不同之处在于进入脉冲数据n回放结束状态后,当时序控制计数器计数到CT,即雷达周期Tr对应的计数值时才开始状态转移。若n 图9 从状态机2状态转移图Figure 9. State transition of slave state machine FSM2 脉冲数据N回放状态(FSM3)对应从状态机3,其状态转移图如图10所示。该状态机与从状态机1类似,不同之处在于脉冲数据N回放状态进入初始状态所需的计数值为CT-CB对应的计数值。 图10 从状态机3状态转移图Figure 10. State transition of slave state machine FSM3 宽、窄带回波数据分别通过两块PCIe光纤板进行回放。当宽、窄带数据同时回放时,由于两块板卡上State_Machine模块计数器的时钟为非相参本地时钟,因此在数据回放过程中,宽、窄带数据传输的时间偏差将持续累加,导致数据回放具有不同步性,影响后端实时处理系统的正常工作。 本文定义Tclk为时序控制计数器时钟周期,α为Tclk的相对误差,t为雷达回波数据回放持续时间,N为t对应的计数器时钟累积计数值,M为连续回放脉冲数。设Δt为板间同步回放时间偏差,可得 Δt≤N·(2·α·Tclk)=2αt=2αMTr (1) 设β为实时处理系统对于Δt的相对容许度,为达到多类型数据并行实时处理的要求,需满足 Δt≤β·Tr (2) 由式(1)和式(2)可推出,当式(3)成立时,数据回放的板间时间偏差可满足实时处理系统的要求。 (3) 在假设雷达回波数据的雷达周期时,要求各数据同步回放的时间偏差不超过雷达周期的一半。驱动State Machine模块的时钟模块的频率误差为50 ppm,根据式(3)可知,在连续回放的回波数据帧数不超过5 000的情况下,即可认为两块板卡为同步回放状态。 以上为数据回放过程中雷达周期为定值的情形。当回放数据雷达周期非定值时,式(1)和式(2)变为 (4) (5) 由式(4)和式(5)可推出,当式(6)成立时,数据回放的板间时间偏差可满足实时处理系统的要求。 (6) 如果连续回放的帧数超过了式(3)或式(6)所得到的上限值,就需要采取额外的板间同步控制措施。为解决数据回放的板间同步问题,本文分别提出软件同步控制方法和硬件同步控制方法。 图11为软件同步控制流程。通过读取宽带和窄带数据文件,并根据其帧索引列表进行数据分割,使得两类数据文件的帧序列号保持一致。随后,向宽带和窄带PCIe光纤板同时发起DMA传输。两板单次DMA传输的脉冲数相同,且不能超过式(3)或式(6)要求的上限值。当两块板卡的DDR3自定义空信号均拉高时,向两块板卡同时发起新一轮PCIe DMA传输。 图11 软件同步控制流程图Figure 11.Procedure of software synchronization control method 软件同步控制方法灵活且易于实现,其数据回放的板间时间偏差可被控制在Tr级别(1 ms及以上量级)。但是当实时数字信号处理系统需要对不同类型的雷达回波数据进行更为严格的同步控制时,则需要采用硬件同步控制方法。 硬件实现方法主要是利用光纤将两块PCIe光纤板连接起来,在光纤接收端使用恢复时钟驱动时序控制计数器,保证两块板卡的计数器时钟为相参时钟,数据回放的板间时间偏差不再随回放时间累积。恢复时钟的使用可参照文献[18]。硬件同步控制方法可将数据回放的板间时间偏差控制在Tclk级别(10 ns量级),相比软件同步控制方法具有更高的同步控制精度,但其开发和实现成本也相应较高。 本文依照设计方法完成回放系统的开发实现,其软件界面如图12所示。将回放系统功能模块嵌入至数据存储管理系统内,用户可对回放数据进行选择,并根据数据通道数进行回放数据的预处理。用户点击开始/停止回放按钮,可启动/停止数据回放。图13为系统将雷达回波数据回放至实时数字信号处理系统后的实时成像结果。 由图12和图13可知,本文设计的系统实现了多通道数据的并行回放,并实现了宽带去斜数据与窄带数据的同步回放。回放过程中,单路光纤通道的链路速率为3.2 Gbit·s-1,单板最多可支持6个光纤通道的数据回放,峰值回放速率可达1 920 MB·s-1。(注:图12、图13分别为数据存储管理系统和实时数字信号处理系统软件界面。根据保密要求,在原始界面截图的基础上,对雷达参数等敏感信息相关的按钮及状态栏进行模糊化处理,仅对数据回放操作及功能验证相关的部分界面进行清晰显示) 图12 数据回放软件操作界面Figure 12. Operation interface of the playback software 图13 回放数据实时成像结果Figure 13. Real-time imaging results of the radar echo signal from the playback system 本文设计并实现了一种基于FPGA的宽窄带一体化、多通道雷达数据回放系统,并详细阐述了回放系统的平台组成、回放系统总体结构设计、PCIe DMA实现流程、数据回放时序控制方法、宽窄带数据回放同步控制方法。该系统支持宽窄带两种数据类型的同步回放,各数据类型可支持1 920 MB·s-1峰值回放速率和6路并行数据通道,且已被应用于某相控阵雷达中。本文设计的回放系统基于雷达原有硬件平台来实现,无需增设板卡或接口,其设计与实现方法具有良好的通用性,可为雷达数据回放系统设计和雷达实时处理系统的性能验证提供参考。

5 板间同步控制

6 系统测试结果

7 结束语