基于MLVDS 接口电路在波控系统中的应用

王相昂,马诗洋,刘悦,李永佳

(中国电子科技集团公司第五十八研究所,江苏无锡 214072)

波控系统的主要任务是在满足雷达的环控条件下,根据雷达控制的指令完成对天线阵面波束合成的实时控制[1],主要负责将移相码、衰减码、控制码等波控码和相关时序信号实时分配转发给TR 组件、延时放大组件等微波组件,实现天线波束的电控扫描。

相控阵雷达的有源通道数,与传统雷达相比较有较大增加,在一般机载雷达中通道数量达1 000~2 000[2-3]。所以信号的传输通常使用总线的方式,进而降低板间连接器与线缆的数量及重量,而总线的选择,通常选用RS422 总线[4]。该设计选用MLVDS作为通信总线,MLVDS 作为多点LVDS,可以驱动多个收发器实现总线的互联应用,其具有高传输速率、低功耗和低噪声的特点[5]。波控单元的主控芯片有较多选择,例如FPGA、ASIC 等,相比较于ASIC 而言,FPGA 的程序可随意更改,以便适应多变的应用环境和系统参数。在航天领域中,通常SRAM 型FPGA 抗单粒子翻转的能力较差,而反熔丝FPGA 本身对辐照免疫,可靠性较高,在航天领域应用较为广泛[6-8]。早期国内外航天器所需的FPGA 产品均来自美国的Actel 公司,而当前为应对西方对我国的技术封锁和核心元器件禁运,亟需实现反熔丝FPGA 产品的国产化[9-11]。

该设计中采用中国电科58 所的反熔丝FPGA 型号为JRT54SX72A 作为控制器,MLVDS 接口采用中国电科58 所宇航级芯片JRMLVD201,完成多节点数据传输,在此基础上设计实现了一种波控单元设计。

1 波控系统总体框架设计

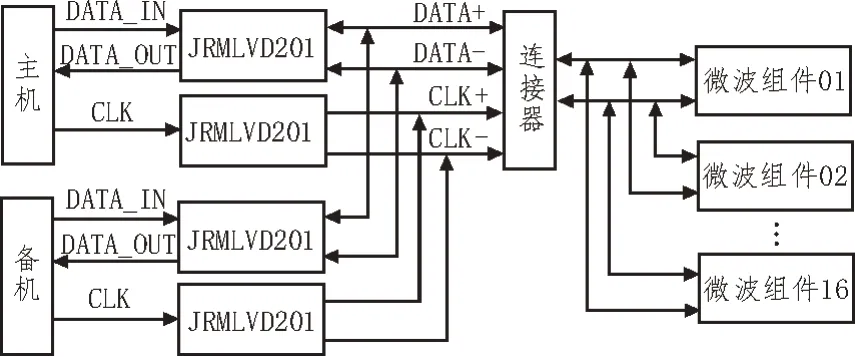

该文设计的波控单元通信主要由RS422接收器、FPGA 控制器、MLVDS 总线接口及电源组成。模拟主控将波控码和时序信号以RS422 差分信号形式送入波控单元的RS422 接收器。RS422 接收器将波控码和时序差分信号转换成单端信号送给FPGA 控制器;FPGA 控制器完成串/并转换后,校验判断波控码的正确性,正确的数据进行多路分发到ASIC 组件中,错误数据被丢弃,并告知主控重新下发码值。为了验证该波控单元的功能,设计了测试系统,主要由模拟主控、波控、ASIC 组件组成,连接关系如图1 所示。所谓ASIC 组件是指在很多微波组件中,组件控制芯片是定制的ASIC,与射频芯片集成在TR组件内[12-13]。

图1 波控系统信号流框图

由于微波组件的数量较多,因而时序信号采用总线的形式以降低电缆的数量和整机质量,通常选用RS422 总线;在工程上RS422 接口芯片作为总线时,最多驱动8 个器件,且只能传输单向信号,而该波控单元产生的MLVDS 信号以总线形式传输,每个MLVDS 芯片驱动16 个ASIC 组件,并且可以传输双向信号。

MLVDS 支持多节点互连的拓扑结构,可提供较高的数据传输速率(理论上高达500 Mb/s)和更低的功耗[14];该设计依托某星载项目,考虑主备芯片交叉备份,单路实现了驱动16 个组件,其中CLK 为单向信号,DATA 为双向信号,就波控系统而言,考虑冷备份单路只需要4 颗JRMLVD201 芯片。波控单元MLVDS 接口冷备份方案如图2 所示。

图2 波控单元MLVDS接口冷备份方案

波控单元板卡采用冷备份方式进行设计,所以系统只能对主机或者备机单独上电。波控单元通过板载连接器和对外甩线的方式与组件通信。根据数据传输线理论,数据传输的速率及远近除了选定合适的电平类型,驱动芯片,还有传输载体及传输线的选取[15-16]。该设计的线缆采用等长双绞线加屏蔽的方式,同时选择高速低损耗的传输材质。

2 MLVDS接口硬件电路设计

JRMLVD201 是抗辐射多点低压差分信号(MLVDS)驱动器和接收器,相比LVDS 标准TIA/EIA-644,MLVDS 标准增加了多点应用。驱动器输出支持的最小负载可达30 Ω,同时具备冷备份功能。

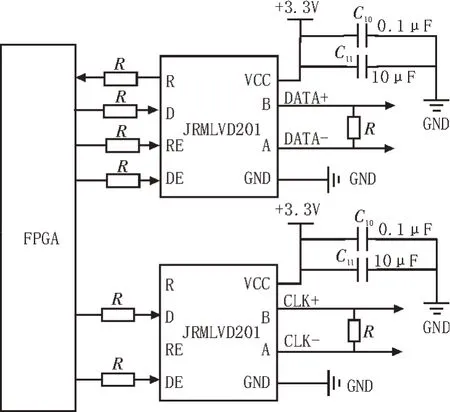

图3为JRMLVD201硬件设计图,其中包括发送给TR 组件的数据信号TR_DATA、时钟信号TR_CLK、模式控制信号RE、DE,其中CLK 与DATA 信号均由FPGA 控制产生,并经JRMLVD201 转换成MLVDS 差分信号送给各微波组件,RE、DE 信号通过TTL 电平加BUFFER 后,直接发送给各ASIC 组件。

图3 JRMLVD201电路图

波控单元发给各ASIC 组件的控制信号采用点对点通信方式,这是为了保证分发给各微波组件的数据能同时到达,保证布相时间的一致性。波控单元发给各微波组件的时序控制及数据信号采用MLVDS 总线的形式,设计的每路MLVDS 总线挂载16 个微波组件即“1 拖16”结构,这样做的目的是为了控制电缆的数量和整机重量。

设计中的MLVDS 应用半双工链路,即在相同总线中包含多个驱动器与多个接收器,端接电阻器位于总线的两端。在该拓扑中必须采用双端接地,以支持位于整个传输线路中不同点的多个驱动器。由于这两个端接电阻以并联形式连接,因此多点驱动器所能看到的有效电阻为50 Ω,其计算公式如式(1)所示:

根据传输线理论,当负载阻抗等于传输线特征阻抗时,入射波才能被负载完全吸收不会产生信号反射,为此在连接多个MLVDS 接收器的“总线式”通信拓扑中,需要在最远一个接收器的前端并接一个820 Ω终端匹配电阻,使得16 个组件得到最佳的匹配电阻约50 Ω。

3 MLVDS总线打码方式设计

该设计中由于ASIC 组件数量较多,波控单元的FPGA 打码信号线与实际的ASIC 组件连线不是点对点关系,通过将组编号与通道号设置成相应的映射关系,这种关系为矩阵映射关系。这样就牵涉到信号线的复用,通过MLVDS 电平传输CLK/DATA 与RE/DE 信号,以二维矩阵的控制方式选择具体通道。

图4 中横轴为复用的16 个RE/DE 通道,纵轴为7 组CLK/DATA 通道。当要选择具体通道时,使能相应的RE/DE 通道和CLK/DATA 通道即可,例如图中所选择的打码/回读通道为67 通道。

图4 通道选择矩阵控制图

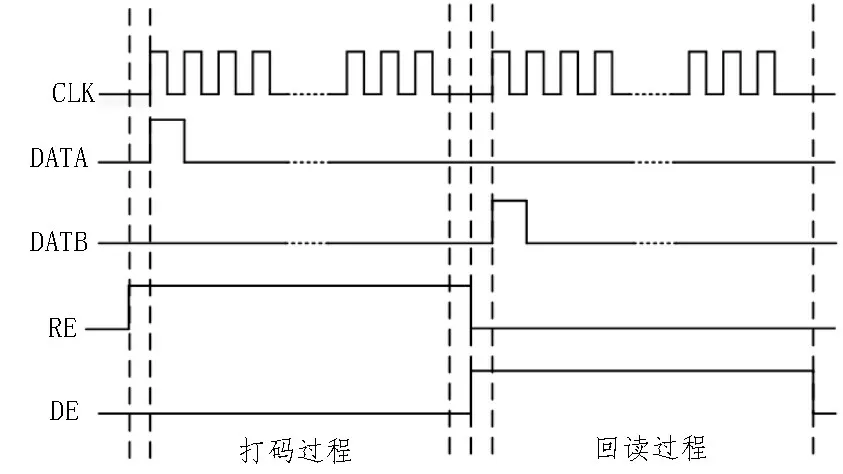

在ASIC 组件进行打码之前,首先需要把ASIC芯片设置为接收状态,如图5 中的RE 与DE 分别设置为1 和0;同样与ASIC 组件相连接的用于传输数据和时钟的JRMLVD201 芯片的RE 信号设置为1,DE 信号设置为1,这样MLVDS 信号才可以用于向外传输数据,回读过程与之相反。

图5 ASIC组件打码回读波形图

4 测试分析

测试平台配备一块模拟主控板,通过RS422 接口发送遥控指令,波控板收到遥控数据后,提取有效打码信息,最后把打码数据下发给相应的ASIC 组件。模拟主控板通过网口与上位机通信,由PC 机经以太网网口使用UDP/TCP 协议下发控制命令,通过RS422 下发到波控板,再经过MLVDS 接口到各个ASIC 组件,该波控单元的测试系统如图6 所示。

图6 测试实物图

图7 上位机界面

PC 机的功能是通过网口接收并显示测试主板统计的波控系统接收的遥控包数和通道打码状态信息,带宽为1 000 Mb/s。上位机界面有自动打码和手动打码两种选择,有误码率和误码次数的统计。在测试的过程中,上位机负责生成随机码,由模拟主控通过RS422 送入波控单元。波控单元中RS422 接口通信模块用于收发管理,再由FPGA 负责提取报文中的打码信息和对ASIC 组件进行回读校验,并记录组件的打码状态。

为了对MLVDS 总线数据传输速率和带载能力进行评估,在上位机界面选择不同打码间隔时间,从而计算出一定时间内上位机下发的数据量,即可计算出传输速率。通过插拔后端ASIC 组件数量来控制MLVDS 带载能力。

测试方法如下:该测试系统中1-7 组的ASIC 组件数量均为16 个,持续测试时长为2 h,若在2 h 的测试中上位机界面没有出现误码触发,则此组可达到目前设置的测试速率,后续继续缩短打码时间间隔增加测试速率,直到上位机出现误码触发,以此记录当前组最大传输速率。

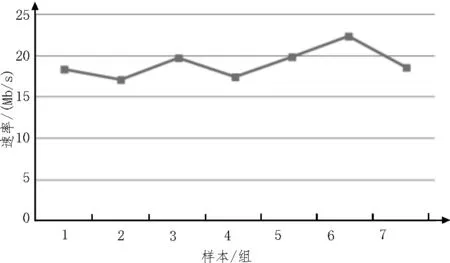

由于在PCB 上的1-7 组走线长度各不相同,因此各组之间速率会有差异,从图8-11 可以看出,数据传输速率稳定在10~20 Mb/s 之间,实现从波控单元到ASIC 组件“1 拖16”结构通信。当波控单元到ASIC 组件甩线长度为1 000 mm 时,其中速率最高可达18.7 Mb/s;当线长为500 mm 时,速率最高可达20.32 Mb/s;当线长为250 mm 时,速率最高可达22.3 Mb/s。

图8 线长1 500 mm时各组传输速率测试曲线

图9 线长1 000 mm时各组传输速率测试曲线

图10 线长500 mm时各组传输速率测试曲线

图11 线长250 mm时各组传输速率测试曲线

5 结论

该文基于MLVDS 接口电路作为总线传输设计的波控单元,采用反熔丝FPGA 作为主控制器[17-18],经过实验该波控单元通过1 拖16 线缆传输,传输距离为1 000 mm 时,传输速率可达18.7 Mb/s,板卡总功耗仅为1.5 W;该设计可满足一般相控阵雷达上波控单元的使用需求。相比较RS422 接口芯片为总线传输,采用MLVDS 总线接口,可使得波控单元设计尺寸、质量、芯片数量均有所降低。