基于FPGA的光电编码器的接口设计

李 鹏

[摘要]详细研究对增量式光电编码器脉冲信号进行细分、计数以及传输的基于FPGA(现场可编程逻辑阵列)的接口电路。采用以高度集成的FPGA芯片为核心的设计方式,实现增量式光电编码器对信号的处理。编码器输出的数据在FPGA芯片中进行细分、辨向、计数等传输处理,最后所得的数据经寄存器存储。验证光电编码器FPGA接口信号处理系统的可行性。

[关键词]FPGA 光电编码器 接口 信号

中图分类号:TP3文献标识码:B文章编号:1671-7597(2009)0510006-02

本课题的目的就是通过使用FPGA芯片实现对光电编码器输出信号进行数据采集,实现小型化、集成化、同时能够对相应的数据进行处理。整个数据处理系统的绝大部分数据处理工作都在FPGA芯片中进行的,具有很高的效率。

按照FPGA自顶向下的设计思想,将光电编码器的实现分成倍频、鉴向模块、计数模块、时钟模块、控制模块和FIFO模块这几部分。倍频、鉴向模块主要功能是产生四倍频信号和计数方向信号以提供给计数器;计数模块的主要功能是根据编码器的旋转方向对其进行加计数和减计数。时钟模块的主要功能是控制整个编码器的时钟信号。控制模块的主要功能是控制计数器对不同脉冲分别计数。FIFO模块的主要功能是能对脉冲进行读写操作,能把脉冲数据有效的保存。

一、时钟模块

本系统选用了300KHZ信号作为CLK信号的时钟。而系统的全局时钟频率是3MHZ,因此我们对3MHZ的信号进行了分频,将其分频为需要的300KHZ。

在FPGA设计中一般都使用全局时钟网络,这样可以驱动所有触发器和时序电路,保证到各个时序元件(触发器)时钟输入端等长,同时全局时钟网络还具有很强的驱动能力,保证时钟信号引入的抖动非常小。

鉴于时钟信号的重要性,对3MHZ的分频我们使用计数器分频,将其分成所需的300KHZ。

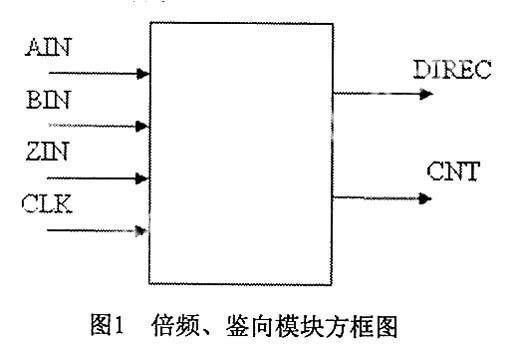

二、倍频、鉴向模块

倍频、鉴向模块是光电编码器FPGA实现的一个主要模块。设计的倍频、鉴向模块方框图如图1所示。

其中CLK时钟为在时钟模块产生的250KHZ的时钟信号。AIN,BIN,ZIN对应于通道编码器的输出信号。

DIRECT,CNT为倍频、鉴向后的输出信号,其中CNT为四倍频后的输出,DIRECT为鉴向后的输出信号。

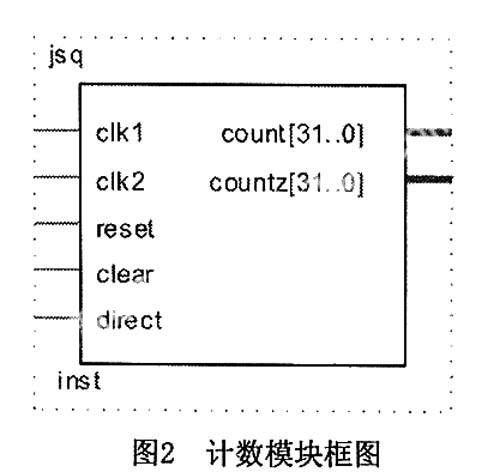

三、计数模块

计数模块是根据编码器旋转方向DIRECT的值,对四倍频后的信号进行计数,当DIRECT为逻辑‘1时,进行加计数;反之则进行减计数。其方框图如图2所示。

计数器模块介绍如下:

clk1,clk2:来自时钟模块的时钟信号。

reset:系统的复位信号。

direct:来自倍频鉴向模块的方向信号。

clear:系统的清零信号。

count[31..0]:计数器对A、B相的计数输出。

countz[31..0]:计数器对Z相的计数输出。

鉴向,倍频和计数模块都设计好了后,就可在顶层文件中直接调用它们了。因为设计中大量使用了触发器,因此如果是直接调用,则会产生时钟偏斜问题。

在本设计中为了避免产生时钟偏斜,采用了两个时钟的方法,因为计数器主要是对四倍频输出信号CNT计数,因此根据CNT的相位,由CLK时钟派生出一个和CNT频率相同的衍生时钟,这样,在计数器模块中只对这个衍生时钟进行计数就可以了。通过这种方法即解决了时钟偏斜问题,同时也解决了四倍频信号计数的问题。

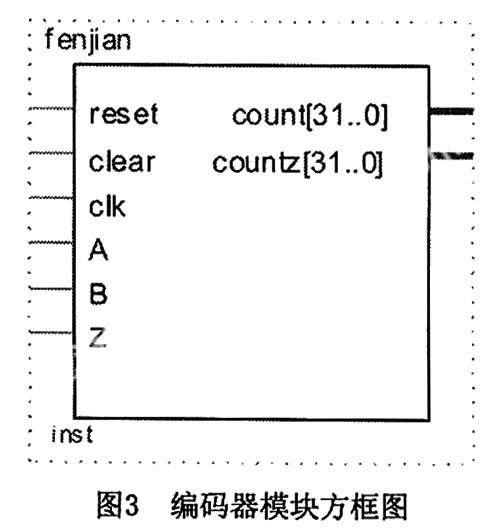

将时钟、鉴向、倍频、计数模块综合在顶层文件后,生成综合的编码器处理模块。图3是倍频、鉴向、计数后综合模块的方框图。

综合后编码器模块信号介绍如下:

clk:系统时钟输入信号,时钟频率为3MHZ。

reset:系统复位输入信号,系统复位是计数器清零。

clear:计数器清零输入信号,当控制信号为1时,对计数器清零。

A,B,Z:编码器的输入信号。

count[31..0]:计数器对A、B相的输出信号。

countz[31..0]:表示是对Z相计数的计数信号。

四、控制模块

控制模块主要是为了控制计数器在不同状态下对不同的脉冲分别进行计数,它的设计主要包括数据选择模块和计数控制模块。

1.数据选择模块

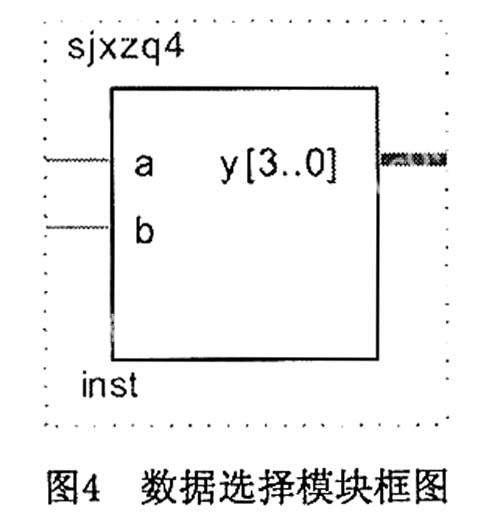

为了实现分别对A、B相和Z相输出脉冲的计数,采用数据选择模块来给定控制的信号。根据m、n两个输入信号的状态来控制计数控制模块,从而实现对它们的分别计数。其结构框图如图4所示。

数据选择模块介绍如下:

a,b:模块的输入信号;

y:模块的输出信号,作为数据控制模块的控制数据输入信号。

2.计数控制模块

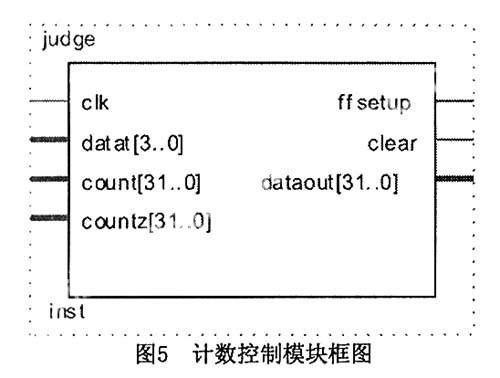

计数控制模块主要就是收到计数状态控制模块送来的控制信号,通过分析、判断,从而来控制计数器。其结构框图如图5所示。

计数控制模块的介绍如下:

clk:时钟信号;

data[3..0]:控制信号;

count1[31..0]:对A、B相计数数据的信号;

count1z[31..0]:对Z脉冲计数信号。

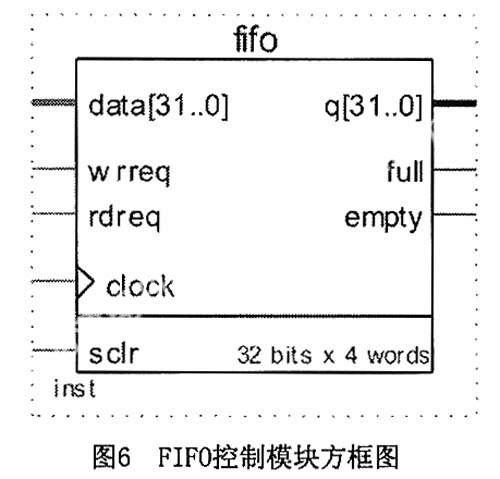

五、FIFO读写控制模块

FIFO是先入先出存储器,它是一种单向数据传输物理器件,它只允许数据从输入端流向输出端。FIFO器件有两个端口:写端口(din)和读端口(dout)。FIFO存储器分成两大类:同步FIFO存储器和异步FIFO存储器。同步FIFO存储器只有一个时钟信号,它同时用来控制存储器的读、写操作;异步FIFO存储器有两个时钟信号,分别控制存储器的读操作和写操作;

由于本系统中的FIFO读和写操作都是相同的时钟频率下进行操作,因此设计中选用了同步FIFO存储器。FIFO存储器有7条信号线,其中DATA,CLK,WRREQ,RDREQ是存储器的输入信号,DATA为输入数据信号线,WRREQ为存储器写操作控制线,RDREQ为存储器读操作信号线。Q,EMPTY,FULL是存储器的输出信号,Q为输出数据信号线,EMPTY为存储器空信号,逻辑‘1有效,表示当前存储器为空,可以对存储器进行写操作。FULL信号为存储器满信号。当写入的数据与设定的存储器深度相等时,FULL信号为逻辑‘1有效,表示当前存储器已满。

进行存储器写操作时, WRREQ为逻辑‘1,则存储器在时钟CLK的控制下,将DATA数据信号线上的数据写入到FIFO存储器中存储。同时EMPTY空信号为逻辑‘0。进行存储器读操作时,RDREQ为逻辑‘1,则存储器在时钟CLK的控制下,将以先入先出的方式读出存储器中的数据,同时FULL满信号为逻辑‘0。

本次设计根据设计要求设计了FIFO存储器的读写控制模块,设计方法使用了状态机的设计方法。FIFO读写控制模块分为FIFO写模块和FIFO读模块两个部分。FIFO写模块的功能是将锁存后的计数值写入存储器中。FIFO读模块的功能是将FIFO中存储的计数值读出。

FIFO控制模块方框图如图6所示。

各引脚信号功能介绍如下:

CLOCK:时钟输入端。

SCLR:复位信号输入端。

WRREQ:FIFO存储器写使能输入信号。为1时将锁定后的计数值写入到FIFO存储器中。WRREQ是计数器控制模块输出的控制信号。

RDREQ:FIFO存储器读使能输入信号。为1时,启动FIFO读模块,从FIFO存储器中读出编码器的计数值。

DATA:FIFO存储器输入数据信号线。

Q:FIFO存储器输出数据信号线。

六、整体功能模块的设计及仿真

当系统各部分模块设计成功后。按照FPGA的设计思想,就可以在QuartusⅡ软件中将编码器输入信号的倍频鉴向模块、时钟模块、计数模块、计数控制模块和FIFO读写模块各个部分模块在顶层文件中综合,利用仿真工具对其进行仿真。仿真后的时序图如图7所示。

对仿真图进行分析可以看出,整个的仿真过程分为两个阶段。

第一阶段,当编码器正转时,m、n信号为00时,empty信号为高电平,full信号为低电平;当m、n信号为01时,向FIFO中写的是对A、B相计数的数值;当m、n信号为10时,向FIFO中写入的是对Z相计数的数值。在两个时刻empty信号为低电平,full信号为高电平。当给定一个读信号时,FIFO开始向外读数据,读出了写入FIFO中的计数值,q信号为00000002。

第二阶段,当编码器反转时,m、n信号的变化同第一阶段相同。当给定一个读信号时,FIFO开始向外读数据,读出q信号为FFFFFFFE。

这样就完整的实现了系统的功能,说明整体的FPGA 模块已达到了设计的要求,从而来实现数据的传送。

七、结束语

基于FPGA的光电编码器的接口设计来对数据进行采集和处理,克服了使用电路板和单片机对数据进行处理而产生的通用性差、编译复杂等缺点。将信号处理等大量工作集成在FPGA中进行处理,具有实现小型化、集成化、同时能够进行较高频率数据处理等优点。

参考文献:

[1]刘皖、何道君、谭明,FPGA设计与应用[M].北京:清华大学出版社,2000.

[2]董莉莉、熊经武,光电编码器的发展动态[J].光学精密工程,2000(8).