基于ISL5416的GPS/BD-2接收机DDC设计与实现

梁立林,王晓,李朝海

(电子科技大学电子工程学院,四川成都610054)

全球卫星导航具有政治、经济、军事等多方面的重要意义,世界各大国和国家集团都在竞相发展全球定位卫星系统[1]。目前4大卫星导航系统(GPS,Galileo,GLONASS以及中国的BD-2)并存的格局日渐端倪,多个导航卫星星座的建立使多星座兼容操作成为可能。对多星座兼容接收机而言,同一时刻可视卫星的数量增加,一方面使系统的可用性得到了提高,另一方面使卫星的选择范围扩大,有利于我们采用选星策略去选择位置更好的卫星,提高定位精度等。GPS是目前世界上最成熟的卫星导航系统,BD-2是我国自主研发的新一代卫星导航系统。目前,对GPS/BD-2兼容接收机的研究还处于起步阶段。针对GPS和BD-2开展研究,对于我国国家经济安全和国防安全意义重大[2]。

随着GPS抗干扰技术的发展,为了实现数字波束形成,在此基础上,加上某种自适应抗干扰算法,现代的GPS接收机一般都采用阵列天线,要求有多个天线接收通道[3]。因此多通道多载波的DDC设计是实现GPS/BD-2接收机的重要基础,也是设计实现中的难点,随着DDC通道数增加硬件资源开销增大,增加了硬件设计的困难。这里采用专用数字下变频器件ISL5416,结合实际工程需求完成了16阵元GPS/BD-2接收机的DDC设计。

1 系统整体结构设计

1.1 整体结构

该系统设计有16个天线阵元。接收的信号有GPS的L1波段,信号频带为(1 575.42±1.023)MHz,BD-2的B1波段,信号频带为(1 561.098±2.046)MHz。

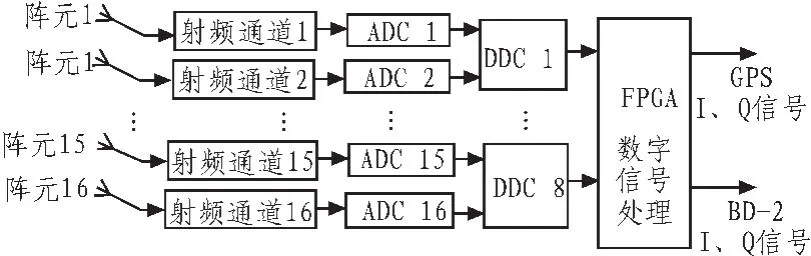

接收机总体框图如图1所示。16个天线分别对应16个射频通道,射频通道只是信号通路,信号经过射频通道没有发生性质变化,只是信号频谱从射频搬移到中频。接收机对北斗和GPS信号的接收共用一个射频通道,并且这一射频通道在结构上也更加简化。ADC输出的数字信号仍然属于多载波的中频信号,需通过2个DDC通道作下变频处理从而分别得到GPS和BD-2信号的数字基带信号。因此,最终实现16个阵元的信号接收需要32个DDC通道,ISL5416是4通道DDC,8片ISL5416组合的结构能够实现系统要求。

图1 接收机总体框图Fig.1 Overall block diagram of the receiver

1.2 工作原理

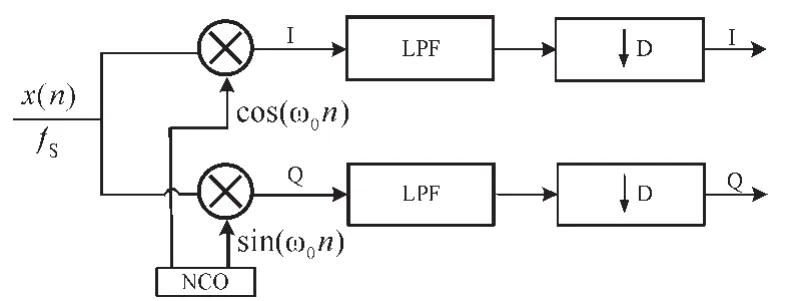

软件无线电中,信号的解调是在基带上完成的,因此基于低通或带通采样得到的数字中频信号都需要通过数字正交变频技术转换为数字基带信号[4]。数字下变频器是将实数的数字中频信号转换为复数的数字基带信号,其正交性由数控振荡器(NCO)输出的正交本振来保证。经下变频的数字基带信号一般都有比较严重的过采样状态,因此在下变频中要进行抽取处理,降低数据率,减轻后续处理的负担[5]。数字下变频框图如图2所示。

图2 数字下变频框图Fig.2 DDC block diagram

2 设计实现

2.1 器件选型

目前数字下变频器主流实现方案有2种:FPGA方案和ASIC芯片方案。

1)FPGA擅长并行运算和流水线处理,能够满足DDC对高速处理需求,另外,由于FPGA设计的灵活性,使DDC模块能根据具体系统的需求量身定制,实现资源和性能的优化,特别适合一些需要高带宽或特殊采样率的场合。其缺点是参数调整的灵活性差难以实现可变带宽,程序的效率和可靠性难以保证,开发调试难度大,另外占用FPGA资源较多。

2)由于DDC在无线电系统中应用广泛,DDC专用芯片(ASIC)的性能经过严格验证,其可靠性和稳定性相对FPGA程序要高很多,用户可灵活配置其内部参数以实现不同指标。但ASIC的结构固定,处理性能有一定局限。目前常见的DDC专用芯片有Intersil公司的单通道DDC HSP50016,HSP50214,4通道的DDC HSP50216,ISL5416;ADI公司的集成ADC和4/6个DDC通道的AD6654。

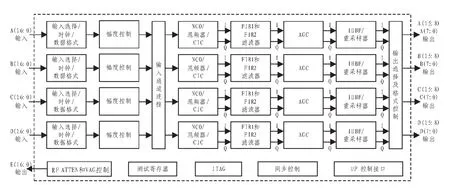

综合考虑该系统设计要求DDC通道数较多,并要求将宽带数字中频信号中不同载频和带宽的信号分离到中频,因此这里采用ISL5416型DDC。ISL5416是4通道大动态范围宽带可编程DDC,每个通道有独立的NCO、混频器、数字滤波器、AGC和重采样滤波器,每个通道都可以独立编程并且实时更新,能够通过将各个通道级联或者多相滤波以增加处理带宽,其功能框图如图3所示。

2.2 DDC电路及参数设计

图3 ISL5416功能框图Fig.3 Function block diagram of ISL5416

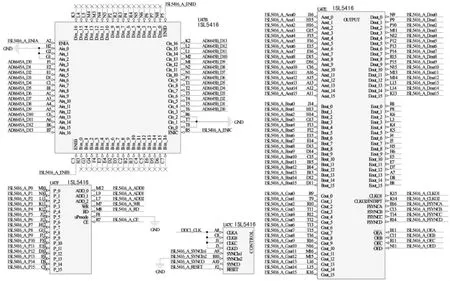

本设计系统,信号经射频通道下变频到中频后,信号频带分别为GPS:(67.42±1.023)MHz,BD-2:(53.098±2.046)MHz。ADC采样率为80 MHz,对信号进行带通采样,根据带通采样原理可设DDC的NCO频率分别为12.58和26.902MHz。最大信号带宽为4 MHz,所以可将下变频信号进行16倍抽取,最后得到I、Q基带信号以5 MHz的数据率输出,DDC芯片ISL5416系统时钟也设计为80 MHz,ISL5416有4个独立的下变频通道,分别取2个作为GPS和BD-2下变频通道。ISL5416有4组信号输入接口,但内部交叉开关可以灵活配置输入连接,所以为了方便硬件电路设计,只选用两组接口分别接到2个ADC芯片的输出,再通过芯片交叉开关配置将信号连接分配到4个DDC通道输入信号接口。同时,ISL5416输入接口为17位,为了连接14位ADC芯片AD6645的输出,在硬件设计上,将ISL5416输入口的低3位接地,高14位接ADC输入。ISL5416关键部分电路原理图如图4所示。

参考ISL5416设计手册根据系统指标,并结合系统设计要求,完成ISL5416各模块的配置和设计如下:

图4 ISL5416关键部分电路原理图Fig.4 Key component schematic circuit diagram of ISL5416

2.2.1 输 入和输出接口

ISL54166输入时钟:80 MHz,时钟输入引脚CLKC;输入数据格式为16位二进制补码,定点;输入模式为门控(GATED);NCO中心频率为GPS:12.58 MHz,BD-2:26.902 MHz;ISL5416的输出接口为4组16位并行输出接口,4个下变频通道要同时输出4组I、Q数据则需要8个16位输出接口。因此采用分时复用输出的方式,即在第1个时钟输出GPS基带数据,在第2个时钟输出BD-2基带数据。接口数据率为10 MHz。

2.2.2 C IC滤波

CIC滤波器通带宽度很窄,而且级数越高相对带宽越窄。在相同相对带宽下,级数越高混叠衰减越大。综合考虑,在混叠衰减-100 dB的条件下,CIC配置如下:

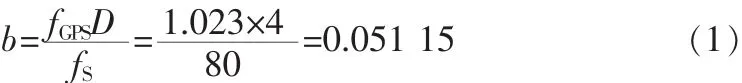

1)GPS CIC级数为5,抽取因子4,输入数据率80 MHz,通带1.023 MHz,计算CIC滤波器的带宽比例因子b为:

参见ISL5416数据手册[6]表可知CIC滤波器通带衰减-0.257 dB,混叠衰减-119.749 dB。

2)BD-2,CIC级数为5,抽取因子4,输入数据率80 MHz,通带2.046 MHz,参照式(1)计算CIC滤波器带宽比例因子b为0.102 3,参见ISL5416数据手册上的表可得带宽比例因子为0.10时,通带衰减-0.717 dB,混叠衰减-96.135 dB。

2.2.3 F IR1滤波器

FIR1有32抽头,有20位可编程系数,20位输入数据,24位输出,每个时钟计算4抽头,如需使用全部32抽头则每次计算共需8个时钟。FIR1的抽取数可以编程为1~8。

由于前级CIC滤波器抽取因子为4,FIR1每次计算只有4个时钟周期,因此可以选择将FIR1配置为16抽头的FIR滤波器,抽取因子为2,输出数据率为10 MHz。GPS和BD-2滤波器设计分别如下:

1)GPS输入数据率20 MHz,通带1.023 MHz,截止频率为6 MHz,阻带衰减80 dB,通带波纹0.1 dB,抽取因子为2,输出数据率降为10 MHz。

2)BD-2输入数据率20 MHz,通带2.046 MHz,截止频率为7 MHz,阻带衰减80 dB,通带波纹0.1 dB,抽取因子为2,输出数据率降为10 MHz。

2.2.4 F IR2滤波器

FIR2有64抽头,有20位可编程系数,20位输入数据,24位输出,每个时钟计算8抽头,如需使用全部64抽头则每次计算共需8个时钟。FIR2的抽取数可以编程为1~8。由于CIC与FIR1总的抽取因子为8,因此可以使用全部64抽头。GPS和BD-2滤波器设计分别如下:

1)GPS输入数据率10 MHz,通带1.023 MHz,截止频率为1.6 MHz,阻带衰减80 dB,通带波纹0.1 dB,抽取因子为2,输出数据率降为5 MHz。

2)BD-2输入数据率10 MHz,通带2.046 MHz,截止频率为2.5 MHz,阻带衰减80 dB,通带波纹0.1 dB,抽取因子为2,输出数据率降为5 MHz。

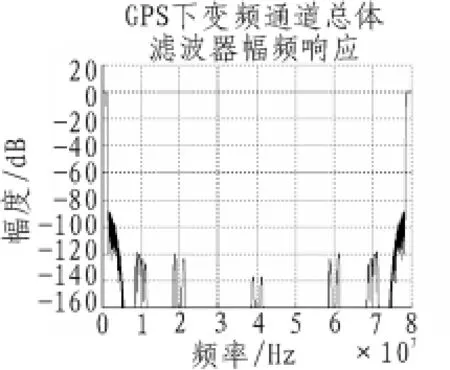

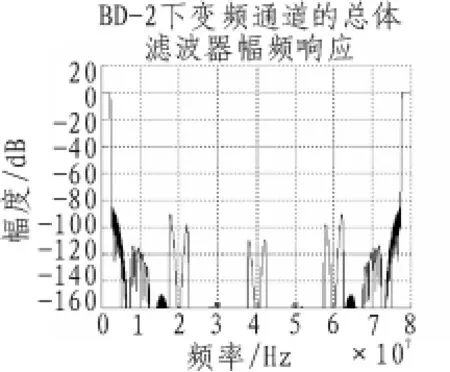

DDC下变频通道,经CIC、FIR1和FIR2级联抽取滤波,3个滤波器级联的总体频率响应如图5和6所示,从图中可以看出带外抑制在90 dBFS以下能够满足实际要求。

图5 GPS下变频通道滤波器级联滤波总效果图Fig.5 Overall filter frequency response of GPS DDC channel

图6 BD-2下变频通道滤波器级联滤波总效果图Fig.6 Overall filter frequency response of BD-2 DDC channel

3 性能测试

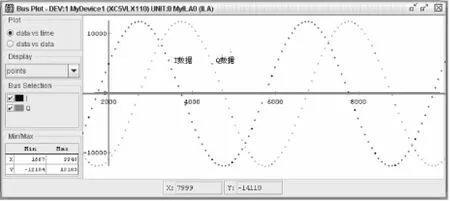

本系统采用AD6645高速ADC采集数据,并将数据输入ISL5416。通过XILINX公司的XC5VLX110,百万门级的FPGA接收DDC下变频后数据。调试时,通过FPGA调试工具软件ChipScope抓取FPGA内ADC数据及ISL5416输出的I、Q两路数据。FPGA内的DDC输出I、Q数据如图7所示。由图可见,ISL5416正确地输出了正交的I、Q两路信号。

图7 ChipScope抓取FPGA内的DDC输出I、Q数据Fig.7 DDC output I and Q data of FPGA obtained by ChipScope

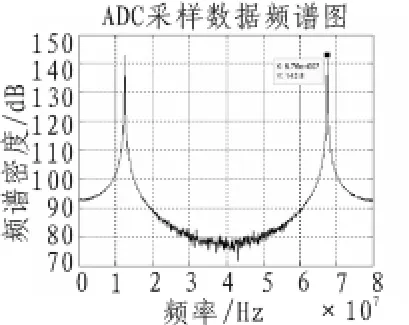

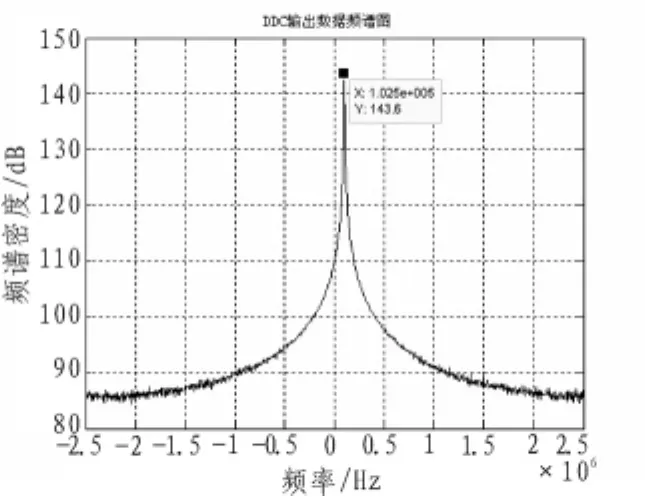

采用安捷伦信号发生器33250A产生67.52 MHz单频正弦信号,在ADC采样率为80 MHz时,采样得到信号频谱如图8所示。信号经ISL5416下变频之后得到I、Q两路数据,I、Q两路数据合成的复信号频谱如图9所示。

图8 ADC采样数据信号频谱Fig.8 Signal frequemcy spectrum of data sampled by ADC

图9 ISL5416输出信号频谱Fig.9 Output signal frequency spectrum of ISL5416

从以上两图可以看出,67.52 MHz单频正弦经80 MHz采样,ISL5416按上文所述的配置工作,频谱搬移67.42 MHz,输出正交的I、Q两路信号,I、Q两路信号的频率为100 kHz,实现了频谱的搬移,阻带抑制符合要求,ISL5416正常工作,实现数字下变频。

4 结论

本文根据工程项目需求,结合4通道专用DDC芯片可灵活配置的特性,合理设计,将接收机中ADC采样后的多载波中频信号,通过DDC通道下变频得到GPS和BD-2的I、Q数字基带数据,以便后续的阵列信号处理及抗干扰算法研究。最终,使用8片DDC芯片ISL5416,实现了16阵元GPS/BD-2接收机的DDC设计。由于此类接收机阵元数多,各通道结构一致,采用专用DDC芯片节约成本,也避免了采用FPGA设计DDC时的重复设计。为软件无线电在16阵元GPS/BD-2接收机的实现提供了解决方案,并具有较强的商用价值。

[1]章燕申.高精度导航系统[M].北京:宇航出版社,2005.

[2]蒋昊,常青,修春娣.GPS/BD-2兼容接收机信息处理系统的设计与实现[J].信息与电子工程,2009,7(6):506-510.JIANG Hao,CHANG Qing,XIU Chun-di.Design and implementation of information processing system of GPS/BD-2 compatible receiver[J].Information and Electronic,Engineering,2009,7(6):506-510.

[3]卢德兼.多干扰下GPS接收机抗干扰自适应算法[J].计算机应用,2009,12(29):344-347.

LU De-jian.New GPS adaptive anti-jamming algorithm in multi-interference circumstance[J].Journal of Computer Applications,2009,12(29):344-347.

[4]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001:3-4.

[5]程佩青.数字信号处理教程[M].北京:清华大学出版社,2006:6-8.

[6]Intersil Americas Inc.ISL5416 DataSheet.[EB/OL].(2004-08)[2010-06-01].http://www.datasheetcatalog.org/datasheet/intersil/fn6006.pdf.