高级加密标准AES算法的FPGA实现

文张斌 颜回中

(暨南大学信息技术研究所,广东广州510075)

1.引言

随着计算机和通信网络的广泛应用,信息的安全性已受到人们的普遍重视。信息安全已不仅仅局限于政治、军事以及外交等领域,而且也与人们的日常生活息息相关。现在密码学理论和技术已得到了迅速发展,它是信息科学和技术中的一个重要研究领域。目前随着密码分析技术的不断发展,超期服役的DES算法已被攻破,DES密钥长度为56位,存在密钥过短的缺陷,3DES是一种由DES衍生出来的算法,虽然增加了密钥长度,但3DES的加密和解密时间消耗较大。Rijndael数据加密算法成为AES算法的标准以来,经过多年来的分析和测试,至今没有发现AES的明显缺点,也没有找到明显的安全漏洞。标准的商品化CPU和DSP无法跟上数据加密算法的计算要求。基于FPGA高度优化的可编程的硬件安全性解决方案提供了并行处理能力,并且可以达到所要求的加密处理性能基准。

2.算法说明

2.1 算法概要

AES是分组密钥,算法输入128位数据,密钥长度也是128位。用Nr表示对一个数据分组加密的轮数。每一轮都需要一个与输入分组具有相同长度的扩展密钥Expandedkey(i)的参与。由于外部输入的加密密钥K长度有限,所以在算法中要用一个密钥扩展程序(Keyexpansion)把外部密钥K扩展成更长的比特串,以生成各轮的加密和解密密钥。

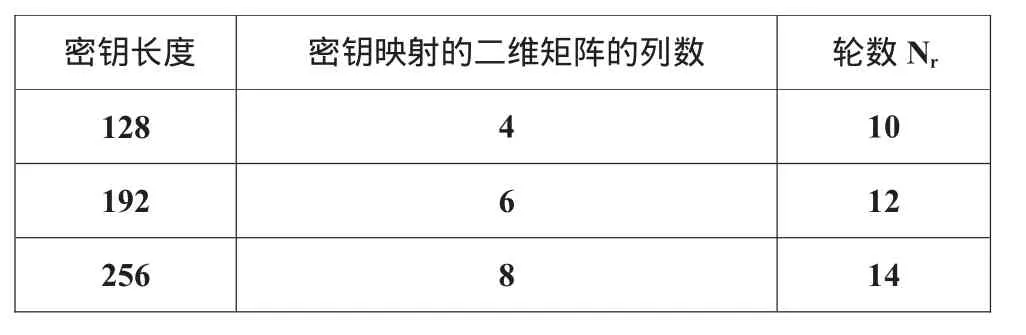

表1 密钥长度与Nk,Nr的关系

Rijndael算法由加密、解密和密钥编排三个算法组成。加密算法是把明文经过Nr+1轮变换得到密文,AES具有128比特的分组长度,对于128,192,256位密钥长度的Rijndael算法,Nr分别取10,12,14。密钥编排是对初始密钥进行扩展以产生各轮变换所需要的轮密钥。

2.2 AES密钥调度

密钥调度包括两个部分:密钥扩展和轮密钥选取。密钥扩展是指把Nk比特初始密钥映射为所谓的扩展密钥,而轮密钥选取则是从扩展密钥中选择出Nb比特的轮密钥。

2.3 以加密为例的轮变换

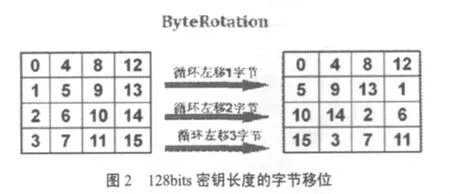

轮变换由字节替代、字节位移、列混合和轮密钥加法4个模块组成。字节代替(ByteSub)变换是一个非线性的字节代替,它在每个状态字上独立地进行运算。代替表(或S盒)是可逆的,且是由两个变换的合成而构造出来的。对于128字节的密钥长度的AES轮变换的字节移位可见图2。

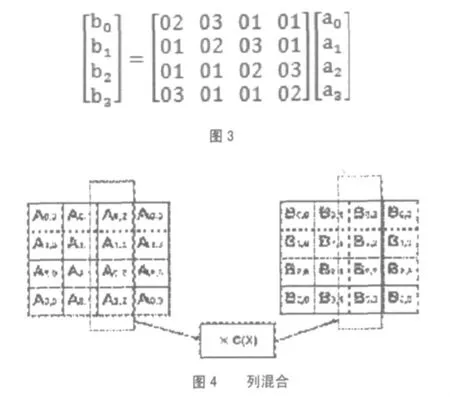

列混合对状态矩阵的列独立进行变换,将状态的列看作是有限域GF(28)上的多项式a(x),与多项式c(x)=03x3+01x2+01x+02相乘(模x4+1)。令b(x)=c(x)×a(x),写成矩阵形式为:

3.AES的FPGA实现

由AES原理可以看出,通过FPGA实现AES算法,各部运算可以分解为最基本的查找和异或。

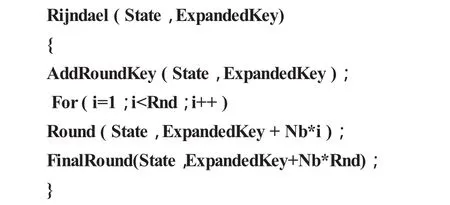

用伪代码表示的Rijndael加密算法,如提前进行密钥扩展,Rijndael加密算法描述可变为:

本设计是用FPGA实现AES加密/解密。命名为wb_aescom troller.V文件包含数据输入输出,接口转换,控制;其它的各个模块均以独立的V文件描述,如sbox.V文件描述的是字节替换表模块(ByteSubstitution,S-盒)。以下以加密为例,详述其过程。

加密开始时,首先由输入密钥开始密钥扩展,由此也决定将要进行循环的轮数。根据输入密钥长度的不同,进行不同轮数的循环。首先是执行密钥加(RoundKey-Add),之后进行Nr轮的运算(最后一轮没有列混合)。

每一轮的开始首先是轮密钥加(RoundKey-Add),本设计中,用了一个128*8的存储器,在加密模块开始时(即数据输入时)同时开始工作,扩展后的密钥存入寄存器组,通过输入密钥的长度和计数器来决定当前输入的、将要进行轮密钥加的128位密钥。字节替换(Byte-Sub)用查找表的方式实现。列混合(M ix-Col)主要是XTime和xor运算,可以分为最简单的xor运算。明文(plaintext)经过Nr轮的运算,即得到密文(ciphertext)输出。

在ModelsimSE6.0软件仿真平台上,编译project里面的所有V文件,经仿真,把工程上的测试文件test_bench_top加入wave,仿真输出波形,可见图6和图7所示。

因此,结合上图5和图6,可以发现384比特的tmo序列的前面128bits被提取为密文;中间128bits作为明文以及加密输入码;后面的128bits作为密钥。仿真输出后,发现加密后输出码流test_out与ciph一致,从加密码流再经解密的输出码流test_out2与最初输入码流plain一致,即设计输出结果符合整个设计要求,AES算法得以实现,结果正确。

4.结束语

本文讨论了用FPGA实现AES算法的设计方案,重点详述了AES算法的原理以及FPGA实现步骤。通过用Verilog语言编写实现程序,在ModelSim SE6.0软件平台上进行编译、仿真,使得以Rijndael数据加密算法的AES高级加密标准得到很好的体现。实验结果表明,本设计基于FPGA可编程逻辑器件的实现方法提供了并行处理能力,达到设计所要求的加密处理性能基准。

[1] 夏宇闻.Verilog数字系统设计教程(第二版)[M].北京航空航天大学出版社,2008.

[2] 储奕锋.AES算法的FPGA实现[J].开发研究与设计技术.2007:191-193.

[3] 张延伟等.VerilogHDL程序设计实例详解[M].人民邮电出版社,2008.

[4] 吴鹏,李开成.基于FPGA的Rijndael算法实现的研究[J].计算机与通信信号.2007(120):46-48.

[5] 唐金艺.AES算法FPGA实现分析[J].计算机安全.2008(6):14-20.

[6] 苏国强,郑小平等.基于低成本FPGA的AES算法实现[J].甘肃高师学报.2009(14):17-19.

[7] 刘腕,何道君等,FPGA设计与应用[M].清华大学出版社,2006.