基于FPGA 的PCI 总线图像采集卡研究与设计

李宇雷

(中国航空工业第六一三研究所数控维修中心,河南 洛阳 471009)

随着视频技术以及大规模集成电路的飞速发展,视频监控系统的应用越来越广泛。作为数字图像信号处理过程中不可缺少的重要部分,图像采集系统将前端相机所捕获的模拟信号转化为数字信号,或者直接从数字相机中获取数字信号,然后通过高速总线传回计算机,凭借强大的操作能力,可以方便决捷地对信号进行分析处理。另一方面视频采集技术也日趋成熟,可用于视频采集卡设计的集成芯片种类繁多,其中基于PCI总线的视频采集卡以其高的数据传输率,即插即用,低功耗等众多优点,得到广泛的应用。

1 图像采集卡总体设计

设计图像采集卡,在芯片和结构上有很多种选择,一般根据设计的需要进行选择。

1.1 系统方案

通过各种方案的比较,系统采用视频解码芯片进行视频信号的解码和同步信号的提取,先利用专业数字图像量化器SAA7110 将模拟视频信号转化为数字视频信号,通过一块ZR36120 和一块SAA7110 芯片就可初步完成视频采集卡的设计,不需要外围芯片,设计成本较低。至于逻辑控制与数据传输,采用的方案是:基于FPGA 和PCI 总线的采集方案,在我们的实际工作中,为了使设计在图像压缩和图像多路采集的硬件实现上有扩展性,PCI 接口芯片选择PLX 公司生产的PC19052,在PC19052 和SAA7111之间用FIFO 存储芯片IDT7206 作为数据缓冲器。PCI9052 没有提供这种串行总线的接口,所以可以借助FPGA 来虚拟I2C 串行总线的信号初始化SAA7111,还能实现数据的实时传送。

1.2 工作原理

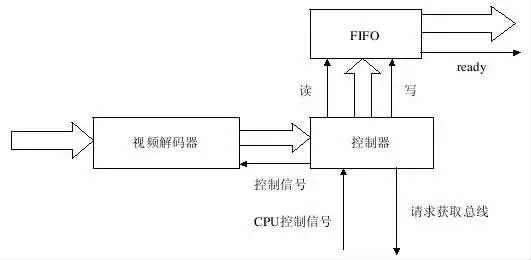

本系统的核心控制部分由一片FPGA 芯片实现,分成三个模块:图像数据采集控制(I2C 总线)、FIFO 读写控制器、与PCI 接口芯片通信。设计的图像采集卡系统原理如图1所示:

图1 系统原理图

整个系统中,FPGA 是中心控制器件,它协调各个部分的时序和工作。系统上电后,它负责图像采集模块的初始化,数据缓冲模块的数据写入,PCI 接口的状态转换和数据传输。下面介绍系统的工作流程,其示意图如图2所示:

图2 系统工作示意图

其工作过程如下:系统上电,PCI9052 的LEREST#管脚置低,同时也复位视频解码器和FIFO,控制器初始化视频解码器;视频信号经过视频解码器后形成YUV 格式的量化的数字信号,其高8位为亮度信号,并产生行、场同步信号;控制器同时接到PCI9052 的RD#命令,根据来自视频解码器的同步信号,并产生FIFO 的写信号,将有效的亮度信号存入FIFO;PCI 总线开始读取数据,并把数据送往PC机。

2 硬件设计与驱动开发

系统要实现一定的功能,必须要在一个对应的平台上进行软件开发,这里主要针对图像采集系统中的典型模块进行详述。

2.1 数据采集

在初始化过程中,我们设置SAA7111为:一路模拟视频信号输入(AI12),625行50HzPAL制式,YUV422 16位数字视频信号输出制式。由于只采用黑白灰度图像,所以只取16位数字视频信号输出的前8位给FIFO。为了控制图像有序的进行采集,需要充分利用视频信号中的同步信号,用其来做数据存储的控制信号。模拟视频信号每扫描一行或对一帧进行扫描完一次后,都会产生延迟,这时是没有有效数据输出的,只有在行参考信号HREF、场参考信号VREF同时有效时,VP0~VP8才有效。由于输出数据的格式设置为YUV422的,所以输出数据与LLC2同步,所以可以利用FPGA的逻辑控制电路,RTS0作为高电平有效开关,HREF和VREF一同作为与非门输入,经过开关,作为LLC2输入的使能输入,LLC2输出作为工作同步时钟接到W。同时LLC作为FIFO的读工作时钟,也应利用FPGA的逻辑电路。

2.2 数据传输与逻辑控制

局部总线使用总线时钟作为工作时钟,同时,先入先出存储器使用LLC 作为读取操作同步时钟接到R。局部总线控制信号RD#用作先入先出存储器R 的时钟开关,控制FIFO的数据读出,当局部总线读取数据时,RD#信号有效,使先入先出存储器在LLC时钟上升沿从缓冲队列中取出数据写入输出缓冲寄存器。当RD#信号有效后,数据被依次读出,每经过一次时钟上升沿,先入先出存储器缓冲队列中向外读出一个数据(8位)。当先入先出存储器缓冲对列空时,局部总线上无法获取有效数据,必须暂停局部总线上的读操作,插入相应的等待时间。当LRDYi#引脚功能有效,在局部总线数据读写时,只有等到LRDYi#上信号输入为有效时,操作才可结束。

2.3 PCI 接口

PCI9052可用作PCI从设备适配器的总线接口芯片,它能适应多种局部总线的设计要求,其新增的ISA 总线接口信号组可控制多个ISA 总线设备。

其中PE 为写使能信号,当它为高电平时,写操作有效。PRE为写保护寄存器访问控制信号,当PRE为低电平时,读写对存储器有效;当PRE 为高电平时,读写对写保护寄存器有效。当写保护寄存器被设置后,对大于寄存器存储值的地址写操作将无效。当PCI9052上电,自动读取EEPROM 中的数据初始化其内部寄存器部分内容。还有一部分主要涉及到PCI 连接器和PCI9052相关引脚的连接关系,因为PCI9052为PCI总线提供了非常简单的接口,只需将PCI9052 上的PCI 总线接口引脚与PCI 总线连接器上的同名引脚相连接即可。在PCI 连接器上有两个引脚是与连接器本身有关的,即PRSNTI#和PRSNT2#。另外,如果扩展板是可以配置的,引脚PRSNTl#和PRSNT2#的接法必须表示出最大配置下的功耗要求。

2.4 软件设计

一个典型驱动程序完成的功能包括:初始化设备、创建和删除设备、处理I/O 请求、访问硬件、调用其他驱动程序、处理热插拔设备加入或删除的情况以及NT事件等。驱动程序不必支持以上所有功能,只有“初始化”模块是必需的,其余的模块都是可选的。使用VxD和WDM具有通用性强,加载方便等特点,但在编写、调试过程中会极大加大难度。但是编写WDM 需要专门的开发、调试工具,难度很大,开发周期长。相比较而言,开发DLL驱动程序较为容易,但是DLL驱动程序通常是16位的,要想在Windows 9x下访问内存映射的设备,或者处理硬件中断或者进行DMA操作,必须同时开发一个“转换层”DLL。特别是要想提供对“即插即用”设备的充分支持,就必须是VxD。使用VxD开发驱动程序的优点也是显而易见的,VxD直接运行在Ring0 层,即系统最底层,对硬件和软件有直接控制权,功能十分强大,而且实时性明显强于DLL驱动程序。

3 总结

图像采集系统是数字图像信号处理过程中不可缺少的重要部分,这里将FPGA 作为整个数据采集系统的控制核心和传输桥梁,一方面根据上位机的指令来完成对整个系统工作模式和状态的精确时序控制,控制图像采集和压缩解压,另一方面通过FPGA 来控制PCI 总线端的接口功能,来实现的数据实时传输模式。根据前人的经验,数据总体传输率小于PCI 最大理论数据传输率,但是所需要的数据传输率48MB/s 比132MB/s 小很多,所以此方案是可行的,能实现四路实时传输显示。今后可以考虑一路数据用两片FIFO 采用乒乓方式进行存储,这样可以加快数据的传输,提高系统得性能。同时还可以将PCI 接口芯片的功能集成到可编程器件中,这样使电路板的集成度提高,降低了系统总体的成本,节约资源。

[1]李贵山,陈金鹏.局部总线及其应用[M].西安:西安电子科技大学出版社.2003.

[2]吴一波.基于PCI 总线的高速视频采集系统设计与实现[D].国防科学技术大学硕士论文.2002.

[3]鲁新龙,王元钦,马宏,侯孝民.一种基于总线的数据采集系统设计 [J].指挥技术学院学报.2001.5.