基于EDA技术的步进电机控制电路设计

杨显富,丁中木梁

(1.成都大学电子信息工程学院,四川成都 610106;2.成都大学实验技术中心,四川成都 610106)

0 引 言

步进电机是一种把脉冲信号转换为相应的角位移,并用脉冲信号进行控制的特殊运行方式的同步电动机.在额定负载范围内,它的角位移量和转速不因供电电压、负载、环境条件的波动而变化,因而很适合工作在简单的开环控制系统中,这些优点使步进电机得到了广泛的应用[1].步进电机运行通常要经历起动、恒速、停止3个过程,由于启动过程是一个增速过程,和恒速运行相比电机还要多增加克服加速产生的惯性转矩的负担,且增速越快,惯性转矩越大,如果负载转矩加惯性转矩超过了步进电机能提供的电磁转矩就会出现“失步”;反之,停止过程是一个减速过程,减速过快容易出现“越步”现象.为了实现精确控制,必须对步进电机的增速和减速过程加以控制,使其满足应用所希望的增、减速规律.由于步进电机的转速与加给它的电脉冲频率成线性正比关系,要控制转速的递增与递减,只要控制脉冲频率的递增与递减就能达到目的.为此,本文采用VHDL硬件描述语言设计了一款用于步进电机的脉冲频率控制电路,和普通的数字电路设计相比,这种基于EDA技术的设计更具优势,其方便的仿真功能,使设计过程更轻松快捷.

1 步进电机的加减速控制策略

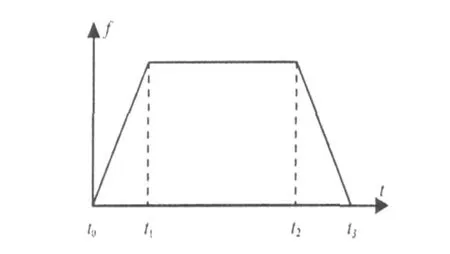

目前,对步进电机的加减速控制有很多方法,如梯形图法、指数法、抛物线法等[2],本设计采用梯形图法.如图1所示,t0~t1时段是步进电机的起动过程,驱动步进电机的脉冲频率按一定斜率线性递增;t1~t2时段是恒速运行阶段,脉冲频率不变;t2~t3是停止过程,频率按一定斜率线性递减.梯形图法的特点是频率变化呈线性规律,这里采用频率线性递增与递减是考虑到可使起动与停止为一个匀加速与匀减速过程,而匀加速匀减速所产生的惯性转矩是一个恒值,只要选择好频率上升(下降)斜率,做到负载转矩加惯性转矩不超过所选步进电机能提供的最大电磁转矩,就可避免电机出现“失步”和“越步”现象.

图1 驱动步进电机的脉冲频率变化规律示意图

按图1所示的脉冲频率变化规律完成电路设计的关键在频率上升和下降这两段,在数字电路中要实现脉冲信号频率变化最简单的方法就是分频[3,4],但分频所得到的一系列脉冲信号之间只能做到周期呈线性变化,而频率呈线性变化却难以做到.为此,本文引入DDS的变频思想来实现图1提出的技术要求.

2 DDS变频与变频电路设计

2.1 DDS变频原理

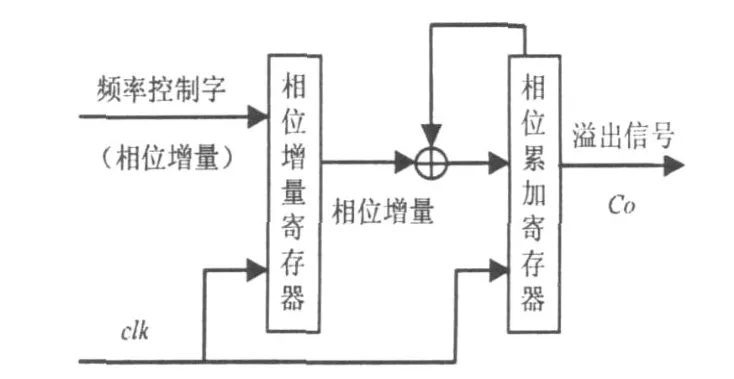

DDS是一种全数字化的频率合成技术[5,6],由它合成的信号,其频率和相位都能线性可控.DDS的频率可变是基于相位增量累加的思想(见图2):在时钟信号clk作用下对相位增量寄存器输出的相位增量作累加后寄存,相位累加寄存器取二进制 n位,当累加值大等于2n时产生溢出,累加仍然在进行,相位累加寄存器的值又一轮从小到大变化,直到再次溢出.显而易见,溢出速率高低和相位增量有关,增量值越大,累加到溢出的速度越快,即溢出率和相位增量成线性正比关系.如果相位累加寄存器每溢出一次,让溢出信号 Co求反一次,则可输出脉冲,这个脉冲信号的频率代表了溢出率.只要给相位增量寄存器不同的频率控制字(相位增量),就可以在 Co获得对应的不同频率的脉冲信号.

图2 DDS变频原理示意图

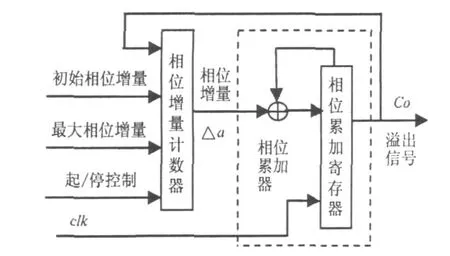

2.2 可控自动变频电路设计

图3 可控自动变频原理示意图

从图2可以看出,要从Co获得某个恒频脉冲,只需输入一个固定的频率控制字就行了,而要获得频率的递增与递减则需要让频率控制字的值按线性规律递增与递减.为了实现上述功能,可将图2稍加改进,把相位增量寄存器改为相位增量计数器(见图3).设相位增量计数器为二进制 m位,通过起/停控制输入起动指令后,在时钟脉冲clk作用下,相位累加器对相位增量△a进行累加,溢出后,用 Co脉冲一个周期中的上升沿或下降沿作为相位增量计数器的时钟触发信号,对输入的初始相位增量做一次累加计数,使△a增大为初始值的2倍.之后,相位累加器完成第二轮累加溢出,输出 Co第二个周期的脉冲.这个脉冲的频率将是第一次输出的2倍,而第二个周期脉冲的跳沿再次触发相位增量计数器对初始相位增量作第二次累加,使△a为初值的3倍.依此类推,不难看出,Co脉冲信号每个周期频率等值递增一次,递增幅度受控于初始相位增量,给定初始相位增量越大,频率增幅越大,频率上升越快,初始相位增量可以控制图1中 t0~t1时段脉冲频率的上升斜率.当相位增量计数器在 Co脉冲作用下对初始相位增量作累加计数直到相位增量△a大于或等于输入给定的最大相位增量后停止累加计数.此后Co输出恒频脉冲,恒定频率的高低由最大相位增量控制,给定最大相位增量越大,恒频频率越高,这就实现了图1中 t1~t2时段对脉冲频率的要求.同时,图3中的相位增量计数器为可逆计数器,在 Co恒频输出期间,通过起/停控制发出停止指令后,相位增量计数器在 Co脉冲作用下对初始相位增量作递减计数,相位增量△a由最大相位增量开始递减(递减幅度和递增幅度相同由初始相位增量决定), Co脉冲频率也随之递减,这一过程满足了图1中 t2~t3时段对脉冲频率的要求.

3 控制电路的VHDL描述与仿真

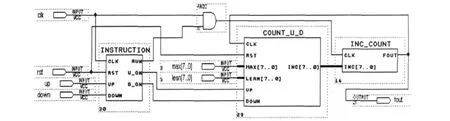

图4 脉冲频率控制器原理示意图

对图3中的相位累加器和相位增量计数器分别用VHDL语言进行描述后,就可在图形编辑界面做原理图连接设计.图4为设计完成的脉冲频率控制器原理图.图4中,模块为相位累加器, fout为脉冲输出信号,模块为相位增量计数器,lean为初始相位增量,用于控制输出脉冲频率的变化斜率,max为最大相位增量,用于控制恒频工作的频率.与图3相比,图4增加了指令寄存器INSTRUCTION模块,这是为方便控制而设置的,clk为电路的工作时钟信号,rst为复位信号,up为起动信号,down为停止信号.

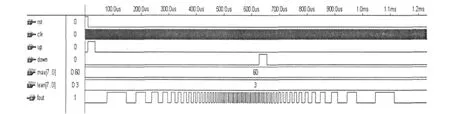

图5是电路的仿真波形.图5中的fout输出是在给定最大相位增量为60,初始相位增量为3的情况下仿真出的脉冲波形.可见,在输入 up、down的控制下,fout波形前段是频率递增过程,中间是恒频过程,后段是频率递减过程.

图5 控制电路仿真波形图

4 结 语

本文从分析步进电机工作过程入手,结合步进电机运行特点,针对其起动和停止过程可能出现的“失步”和“越步”现象,采取频率线性递增和递减的方案来控制步进电机.用DDS中相位累加实现变频,较之采用分频变频的思路,能圆满获得频率线性变化结果.采用VHDL语言描述电路逻辑功能使设计更为轻松快捷,所设计的电路功能完备,尤其是增频斜率可控,最高脉冲频率可控,为步进电机应用在不同场合提供了方便.同时,对设计电路经过EDA技术的编译、综合后再进行波形仿真.结果表明,电路输出的脉冲频率变化规律完全满足设计期望.

[1]任志锦.电机与电器控制[M].北京:机械工业出版社, 2002.

[2]秦兴,周川东,王文.基于FPG A的步进电机控制器设计[J].组合机床与自动化加工技术,2002,20(7):56-58.

[3]庞淑娟,倪受东.基于FPG A的步进电机速度控制器的设计[J].新技术新工艺,2008,20(4):32-33.

[4]温凯,马跃,郝斌.基于FPG A的步进电机控制器设计[J].电脑知识与技术,2010,6(4):978-980.

[5]丁卫东,郭前岗,周西峰.一种基于FPG A的SPWM波的实时生成方法[J].计算机技术与发展,2011,21(2):211-214.

[6]潘松,黄继业.EDA技术实用教程[M].北京:科学出版社,2006.