高带宽数字内容保护技术接收端的研究与设计

蒋特林,阳玉才

(合肥工业大学电子科学与应用物理学院,安徽合肥 230009)

高清视频信号是一种典型的可以从一个系统传输到DVIHDMI接口的信号。这些接口能保证传递的视频图像保持原本的质量,因此可以获得更多的终端用户,但对于企业来说,同时会出现更多没有经过授权和非法复制传输的风险。

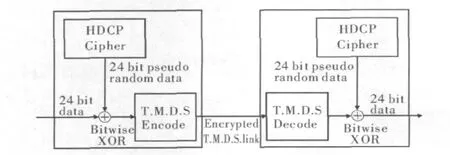

传统的知识版权保护技术仅仅能够保护已经存储在某种介质上的数据,但是高清视频信号仍然能够通过DVIHDMI之类的数字接口进行传输[1],为了解决这个问题,HDCP就应运而生[2]。HDCP是一个基于数据加密和授权验证的内容保护系统。图1描述了HDCP在数字视频信号的发射端和接收端系统中的角色。

图1 视频传输系统中的HDCP[3]

为解决速度和功耗的问题,使用最小差分信号传输(Transition Minimized Differential Signaling,TMDS)来传输信号[2]。在DVI和HDMI里都有一个为控制在发送端与接收端信息交换的通道,这个通道类似于显示器数据通道(Display Data Channel,DDC)。

1 HDCP接收端的结构

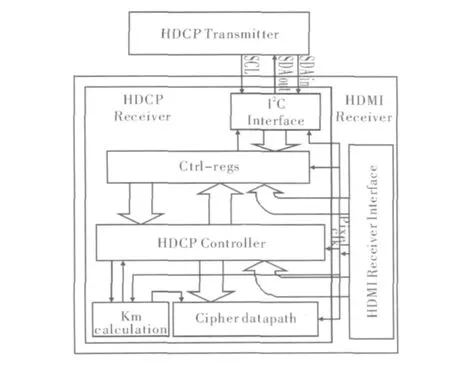

图2描述了HDCP接收端的基本结构。HDCP接收端有2个通信模块:HDCP发送端位于HDMIDVI接收端芯片的外部;而接收端位于HDMIDVI接收端芯片的内部。

HDCP发送端通过I2C总线发送授权认证信号给接收端。HDMI接收端接口通过HDCP控制寄存器的更新来发出操作指令,从而控制HDCP接收端的状态,以及提供必要的信息HDCP接收端知道工作在视频传输的阶段,从HDMI接口接收到解密信息并发送回去。

HDCP接收端由4个模块组成:I2C从机接口,控制寄存器,HDCP控制器以及数据加密机。应该注意图2描述的是HDCP接收端的工作环境,不能把它理解成HDCP发送端和HDMI接收端输入或输出信号的最终传输示意图。文中的最终目标是设计一个同时能够支持DVI和HDMI的HDCP接收端。

图2 HDCP接收端的结构

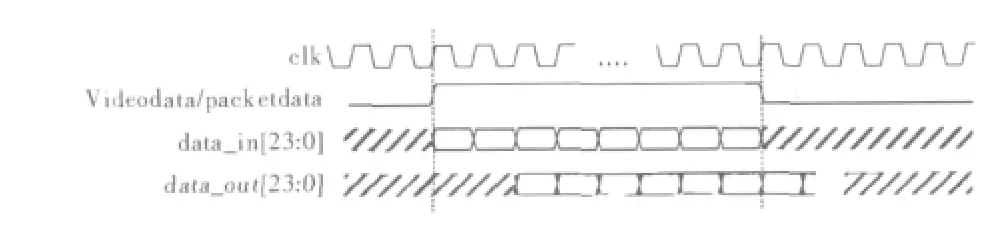

当打包数据或视频数据是逻辑高电平时,数据从HDMI输入到HDCP接收端的解密才有效。数据的输入与输出必须在2个时钟周期内完成。HDMI只有在这个时间内才能够接收到数据。图3描述了数据输入与输出之间的时序关系。

图3 数据输入与数据输出的时序图

2 子模块的设计

2.1 数据加密模块

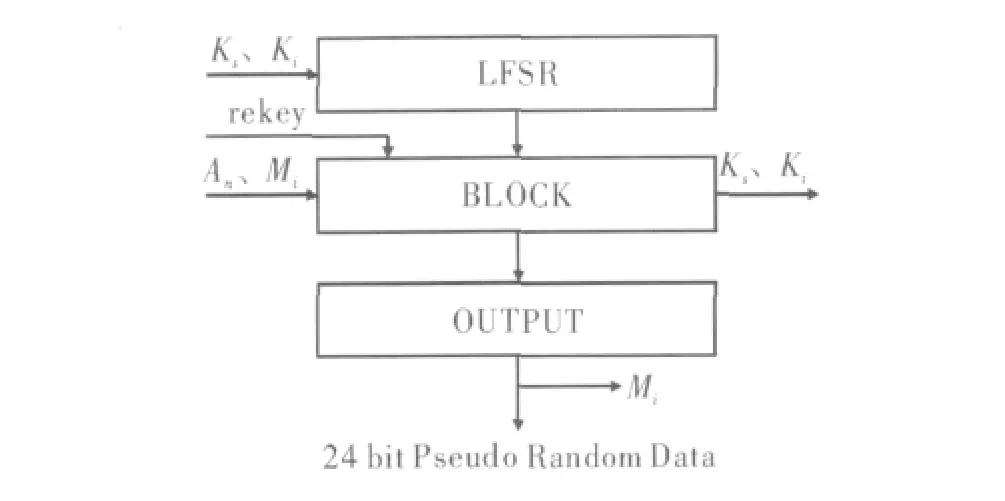

数据加密是为了将数字内容进行加密,防止不合法的传输和复制,它是内容保护的核心逻辑模块。HDCP加密好的数据是由HDCP加密机产生的24位伪随机数据流与HDCP保护内容的数据按逐位异或的结果。HDCP加密是一种能同时为身份授权认证和高速传输非压缩视频数据的特殊加密设计[4]。

数据加密模块采用流加密方法实现,流加密的结构如图4所示,主要由3部分组成[3]:

(1)线性反馈移位寄存器(Linear Feedback Shift Register,LFSR)模块。包括4个不同长度的线性反馈移位寄存器和一个混叠网络。

(2)分组模块。由2个结构非常类似的轮函数B和轮函数K模块组成。

(3)输出功能模块。由基于异或的组合电路组成,在每个时钟脉冲里产生一个24位的伪随机数据。

HDCP控制器根据不同的数据流通方式,分为以下几种不同加密的操作模式:hdcpBlockCipher,hdcp-SteamCipher,hdcpRekeyCipher,HDCPRngCipher。在HDCP的协议中对上述几种操作模式都有详细的介绍。HDCPRngCipher操作模式仅为用在发送端中,所以在此不需要支持该种操作模式。

图4 数据加密模块

2.2 HDCP接收端控制器

HDCP控制模块控制HDCP接收端的所有操作,它通过个状态机来实现以下功能:

(1)HDCP接收端的状态的控制。

(2)计算Km值,HDCP接收端把Key存储到控制器中。

(3)接收端授权认证状态的转换。

(4)HDCP加密状态的转换:OESS,EESS,两种加密方式[5]。

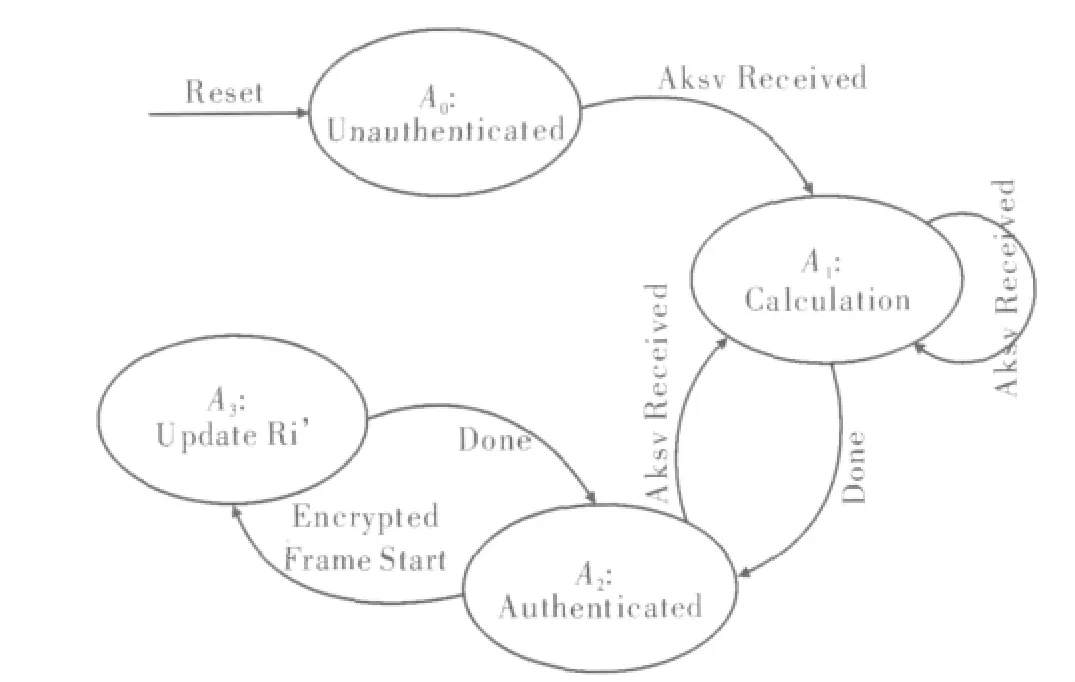

图5描述了授权认证的4个状态之间的关系。状态A0:未授权认证状态;状态A1:计算;状态A2:授权认证完成;状态A3:更新Ri'的值。

图5 授权认证状态图

在Aksv更新信号获得确认后,HDCP控制器根据HDCP发送端的KSV值使用56位二进制的加法来计算Km'值。

在一个时钟内进行20次56位的加法操作可能会产生不能接受的延迟。为了解决这个问题在此提出两种方法来实现该操作。方法一:采用流水线结构,在每个周期里完成一次56位的加法操作,然后在20个周期里完成Km'的最终计算;方法二:使用节约加法器来压缩从2~20的算子,然后执行最终的加法操作。方法二比方法一具有更高的可执行性,但是需要占用更多的资源;方法一相对能节约更多的资源但是延时大。

根据HDCP协议的要求 H DCP接收端必须在100 ms内完成 Km'、Ks'、M0'、R0'值的计算并把有效的R0'值传给HDCP的发送端,该过程是在HDCP发送端的读操作到HDCP发送端完成把Aksv写到视频接收端的操作之后进行,这就意味着延迟在这不是问题,所以在此选择方法一来进行计算Km'值。

接收端授权状态机是控制器模块的核心部分。其他所有的状态机操作指令都是由这个状态机发出的。授权状态的转换是以Aksv完成接收为标志,当HDCP发送端完成把Aksv写到HDCP接收端寄存器0x14位置时,控制寄存器模块将产生这个标志信号。

2.3 控制器寄存器

当HDCP接收端是第一连接器件时,控制寄存器根据HDCP协议中定义的,除了0x20~0x30,0x43地址位,这些是HDCP中继器的控制寄存器;当HDCP接收端是第二连接器件时,仅仅是控制寄存器的子集才允许进入的。I2C接口子模块会发出一个从HDMI接收端接口连接到第一还是第二的指示信号。

所有的寄存器只有一个能进行写操作的源信号。源信号可能来自3个地方:HDCP发送端,HDMI接口以及HDCP接收端。HDCP发送端能够往寄存器中的0x10地址中写入Aksv,0x15地址中写入Ainfo,0x18地址中写入An;HDCP接收端能够往寄存器中的0x08地址中写入Ri,在0x0A地址中写入pj;HDMI能够往寄存器中的0x00地址中写入Bksv,0x40地址中写入Bcpas,0x41地址中写入Bstatus。写操作的时钟信号不是系统时钟而是像素时钟。当最后一位Aksv写入到寄存器的时候Aksv,Ainfo寄存器复位到零,用复写寄存器机制来实现。

2.4 I2 C从机接口

Philips开始开发总线用来在器件内部和电视设备进行通信[6]。HDCP里面定义 I2C作为控制通道接口。有3种操作模式:读(read)、写(write)和短读(short read)。读与短读之间的区别是看读取数据过程是在Start(S)还是Repeated Start(RS)条件下初始化的。在短读模式中,在实际的读操作前不需要写入寄存器的偏移地址。

在此HDCP接收端里面必须有一个能够支持I2C总线的逻辑器件。I2C与第一连接器件的8位的二进制的地址是0111 010x;或者是16进制的0x74作为I2C地址,读写位置零。与第二连接器件的地址是0x76。I2C从机接口逻辑在决定与控制寄存器的哪部分连接根据HDCP发送端指示的从机地址来确定。这个子模块需注意以下几点:

(1)仅有4个寄存器支持该写操作即Aksv、Ainfo、An、dbg。

(2)必须有一个写操作先于Aksv到来。

(3)第一连接器件、第二连接器件与HDCP连接的端口不一样。

(4)地址自动增加必须由I2C接口实现。

(5)ksv FIFO读操作行为地址的增加不同于其他地址增加方法。

(6)授权触发条件:寄存器更新Aksv、Ainfo、An值,最后写入到寄存器中的0x14地址中用以触发HDCP接收端的授权认证序列。

在现代设计中,设计人员一直在寻求一种速度更快,面积更小的电路,以在提高可执行性的同时能减少成本。目前物理层的设计是解决这一问题的重要手段。用全定制设计方法来设计I2C从机接口可以达到减少芯片的面积和功耗。所有的逻辑门和时序元素,如锁存器、D触发器是使用静态的方式来提高电路的可靠性。最常见的方式就是使用主从结构的D触发器设计I2C从机接口。

3 结束语

讨论了HDCP接收端的结构,分析了具体的实现方法。其中包括I2C从机接口、控制寄存器、接收端控制器、加密机等子模块的设计。此HDCP接收端根据HDCP协议设计,符合HDCP协议的要求。

[1]EUGENE T L,AHMET M E,REGINALD L L,et al.Advance in digital video content protection[J].Proceeding of the IEEE,2005,93(1):171-183.

[2]Silicon Image Inc.High-Bandwidth Digital Content Protection White Paper[M].USA:Silicon Image Inc,2002.

[3]Microsoft Word.HDCP Specification Rev1_4.8[M].USA:Microsoft Word,2009.

[4]宋亚平,周玉洁.基于HDCP协议的流加密IP设计[J].通信技术,2007,40(11):314-315,318.

[5]Microsoft Word.HDCP Specification Rev1_1.9[M].USA:Microsoft Word,2003.

[6]KALINSKY D,KALINSKY R.Introduction to I2C[J].Embedded Systems Programming,2001,14(8):1101-1105.